一、可编程逻辑器件

1. 概述

逻辑器件 :用来实现某种 特定 逻辑功能的电子器件,最简单的逻辑器件是与、或、非门,在此基础上可实现复杂的时序和组合逻辑功能。

可编程逻辑器件(PLD-Programmable Logic Device):器件的功能不是固定不变的,而是可根据用户的需要进行改变 ,即由 编程 的方法来确定器件的逻辑功能。

编程:对可编程逻辑器件内部用于连接逻辑门的 开关 进行 配置 ,以实现需要的逻辑功能。

2. PLD的作用与特点

传统数字系统的设计使用标准芯片,电路器件多,电路尺寸大,功耗大,可靠性差,可实现的数字系统规模受到限制。

而使用专用芯片后,系统功能和性能更优,但设计周期长,风险大,设计成本高,一旦完成设计就很难修改。

为了综合两种方法的优点,PLD诞生了:一种按通用器件来生产,但逻辑功能是由用户通过对器件编程来设定的集成电路。

PLD 的优点:

- 集成度高,可以替代多至几千块通用

IC芯片,极大减小电路的面积,降低功耗,提高可靠性 - 具有完善先进的开发工具,提供语言、图形等设计方法,十分灵活;可以通过仿真工具来验证设计的正确性

- 可以反复地擦除、编程,方便设计的修改和升级

- 灵活地定义管脚功能,减轻设计工作量,缩短系统开发时间

- 保密性好

3. PLD的分类

简单PLD:

- PROM(可编程只读存储器,70年代)

- PLA(可编程逻辑阵列,70年代中)

- PAL(可编程阵列逻辑,70年代末)

- GAL(通用阵列逻辑,80年代中)

复杂PLD:

- CPLD (复杂PLD)

- FPGA(现场可编程门阵列)

二、简单PLD的原理与结构

1. 简单PLD的概念原理

任何 组合逻辑 函数均可化为 “与-或” 表达式,用 “与门-或门” 二级电路实现, 任何 时序电路 都是由组合电路加上存储元件(触发器)构成的。

因此,从原理上说 , 与-或阵列加上寄存器的结构就可以实现任何数字逻辑电路。

PLD采用 与-或阵列加上寄存器,以及可灵活配置的互连线的结构 , 即可实现任意的逻辑功能。

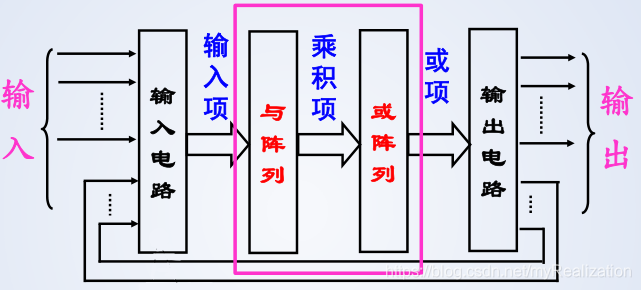

2. 简单PLD的结构原理

其中,输入电路由缓冲器和反相器构成,产生每个变量的原/反变量信号;

与或阵列由多个多输入与门和多输入或门组成,用以产生输入变量的各乘积项和或项。

连接到与阵列、或阵列的信号都要经过一个开关,通过一定的方法改变开关的状态,从而改变与阵列、或阵列的连接方式,以产生不同的与-或表达式,这个过程称为编程。

输出电路对将要输出的信号进行处理,既能输出纯组合逻辑信号,也能输出时序逻辑信号。

3. PLD的阵列图符号

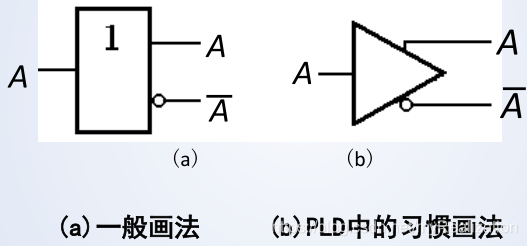

(1) 输入缓冲电路

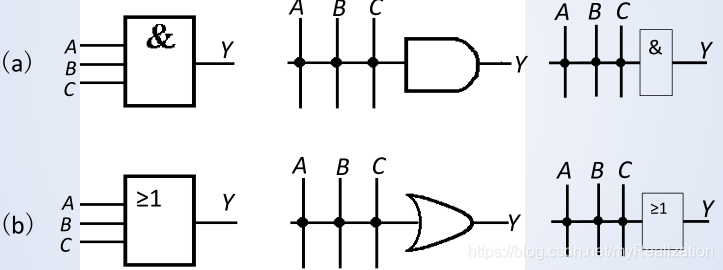

(2) 阵列线连接

其中,编程连接有一个 × \times × 作为标志。

(3) 多输入与门、或门的表达

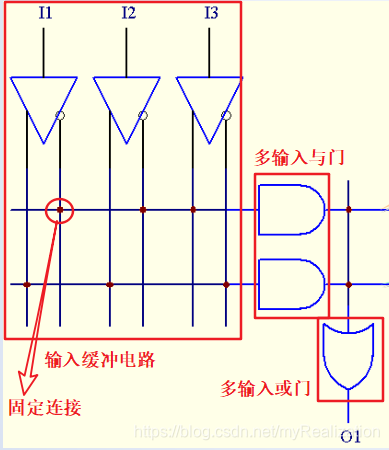

(4) 简单阵列的表示

该阵列表达了两个乘积项 P 1 P_1 P1 和 P 2 P_2 P2,与或逻辑表达式是 O 1 = P 1 + P 2 = I 1 ‾ ⋅ I 2 ‾ ⋅ I 3 + I 1 ⋅ I 2 ⋅ I 3 ‾ O_1 = P_1+P_2 = \overline {I_1} \cdot \overline {I_2} \cdot I_3 + I_1 \cdot I_2 \cdot \overline {I_3} O1=P1+P2=I1⋅I2⋅I3

本文介绍了可编程逻辑器件(PLD)的基础概念,包括PLD的定义、作用与特点,以及PLD的分类,如PROM、PLA、PAL、GAL、CPLD和FPGA。详细解析了简单PLD的原理与结构,以及复杂PLD的结构与应用。

本文介绍了可编程逻辑器件(PLD)的基础概念,包括PLD的定义、作用与特点,以及PLD的分类,如PROM、PLA、PAL、GAL、CPLD和FPGA。详细解析了简单PLD的原理与结构,以及复杂PLD的结构与应用。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1759

1759

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?