软件环境:vivado 2020.2 硬件平台:XC7Z020

dcp网表对于逻辑工程而言,有点类似于lib库或者dll对于c工程。主要是在交付或转手工程时候,不想把核心逻辑模块暴露给对方,这时就可以将模块封装成dcp网表,供对方正常使用,但又无法打开看到内容细节。今天用个小例子来说明如何将模块封装成dcp网表。

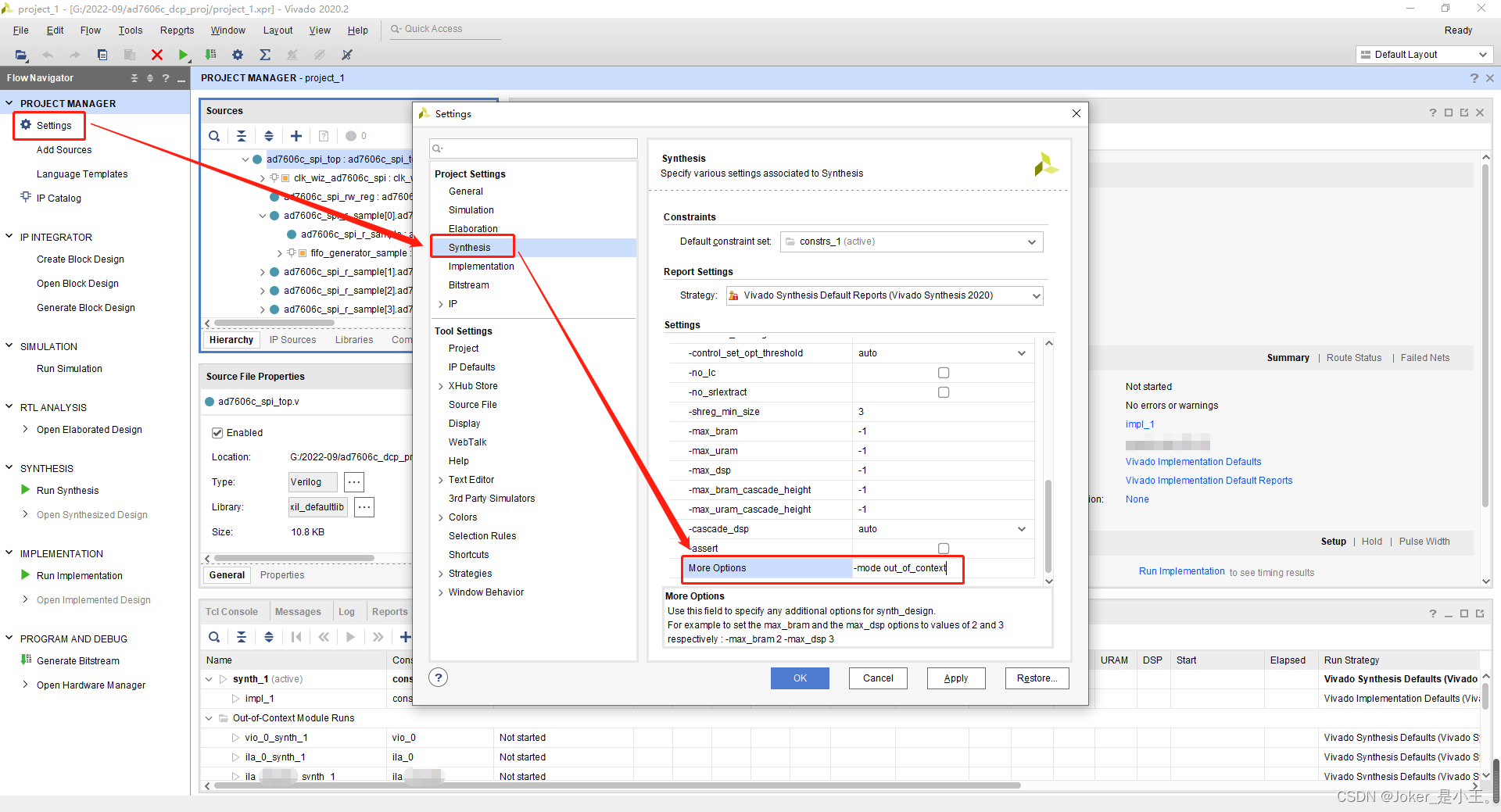

打开要处理的FPGA工程,左上方点击settings,选择synthesis,最下方在more options中,添加-mode out_of_context,然后apply,ok。

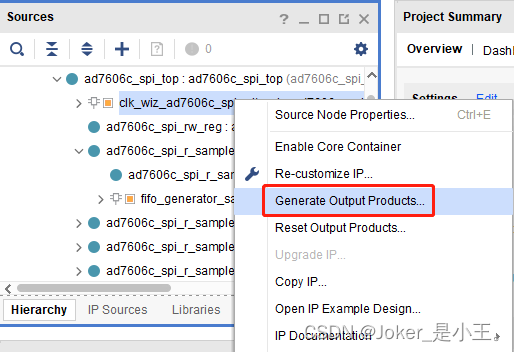

这里我拿之前写过的ad7606c代码做示例,可以看到我的采样模块中除了自己写的.v文件以外,还包含xilinx的clock wiz和fifo。所以需要注意下,在综合生成dcp之前,要把这些xilinx的ip重新generate一下,以global的方式。

弹出的对话框中选择global。fifo模块也做同样处理。

接下来将想封装成dcp的模块右键,set as top设置为顶层,top以下的所有均会封装进dcp。这里还需要注意,dcp文件不能传递参数,即不能通过parameter在顶层赋值,不能够通过parameter来修改dcp中的参数。

顶层设置好以后,点击左侧run synthesis进行综合。

综合完毕后,在工程路径/runs/synth_1,即可看到生成好的dcp网表文件。

将生成好的网表文件替换原工程中的对应模块,重新综合、布局布线、生成比特流即可。

最后重复一下生成dcp网表时需要注意的几个原则:

1.dcp文件不能传参,不要通过parameter进行参数传递;

2.dcp文件中可以包含xilinx的ip,但是ip名字最好特殊一些,不要用自动生成的那种fifo_0、clk_wiz什么的,以免和原工程的ip冲突,dcp中包含的xilinx的ip使用global方式重新生成;

3.dcp文件中不要包含需要license的ip,以免工程移动后,对工程修改无法重新生成比特流。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?