本文源于一个问题:最小电容DRC违反需要修复吗?

答:min电容DRC违反理论上肯定要解决,但实际上,min C电容极可能是库K得不对导致的,所以遇到min C电容DRC违反尤其是很多的情况时,请先找library的提供者去确认,先排除图书馆的问题,如果是真实的违反是必须要修掉的。

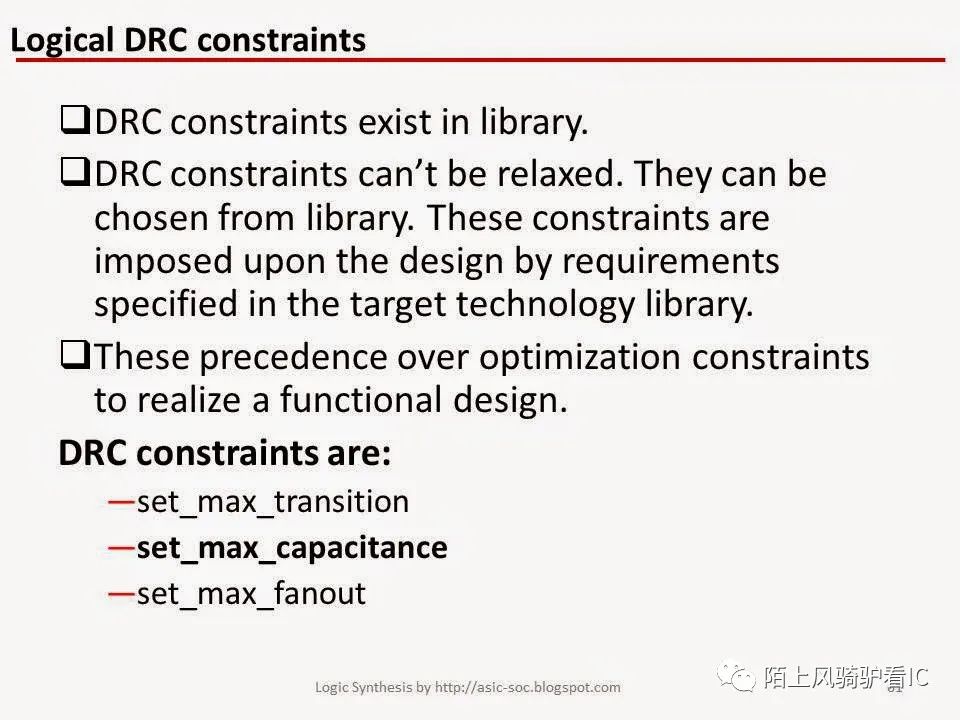

数字实现中有多种DRC,可回顾《数字电路实现中的DRC》。所谓的逻辑DRC指:

-

最大/最小过渡

-

最大/最小扇出

-

最大/最小容量

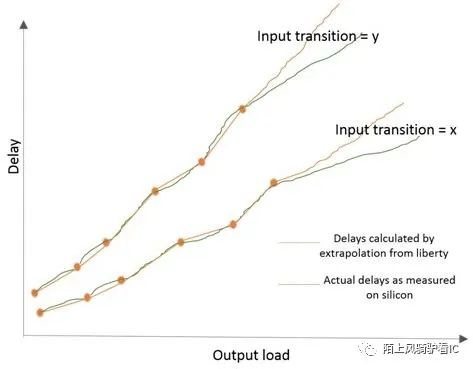

逻辑DRC的目的是限制std cell的行为在库中仿真范围之内,据称目前有两种主流的K库方式,一种是基于SPICE仿真:精确但代价大;一种是AI K库:代价小但是在这种情况下,图书馆中都只定义了transition跟load在一定范围内的table,在STA分析时,对于transition / load在表范围内的用内插得到对应的delay / transition / SOCV等值;对于 过渡/ 负载 在表范围外的用外插方式得到对应的德拉Y / TRAN SI蒂奥N / SO CV等值而外插往往会导致精度损失,所以在实现过程中要保证逻辑DRC在。库的范围内,或代工厂大爷要求的范围内。

-

铸造厂仅在此特定范围内保证电池行为的确定性。<代工厂大爷只保证cell在表内的行为。>

-

表征范围的上限和下限足够大/很小,因此非常罕见地期望该单元超出该范围。由于表征具有其自身的成本,因此将电池表征为极端载荷和过渡可能在经济上不可行。<代工厂大爷指定的表值基本覆盖了大部分需求,超过这个范围的需求不大,而如果要K范围大小的库,代价太大。>

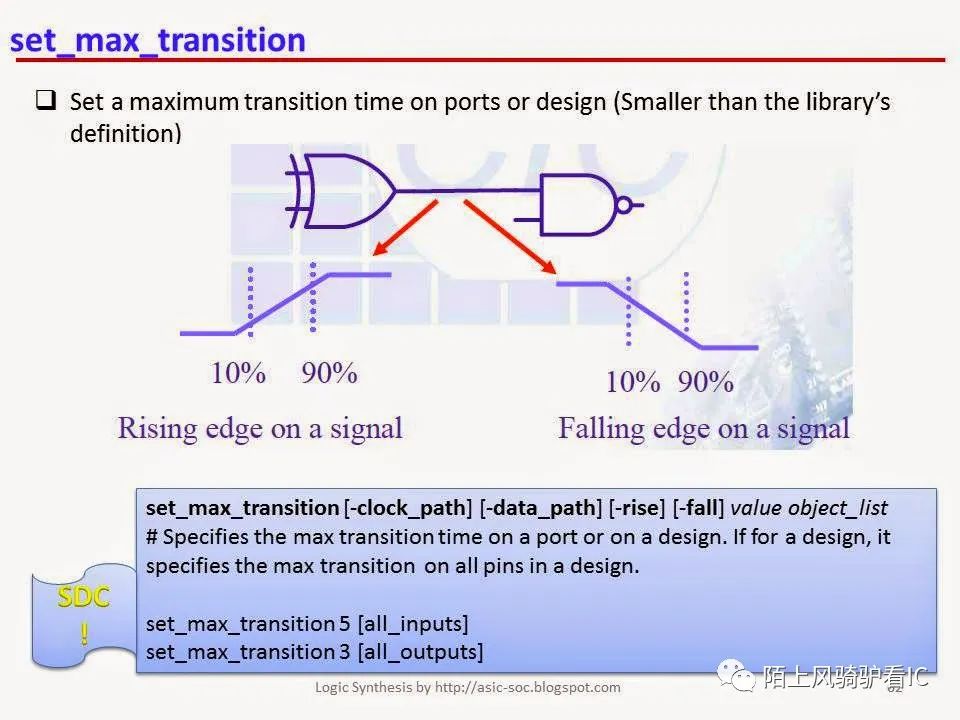

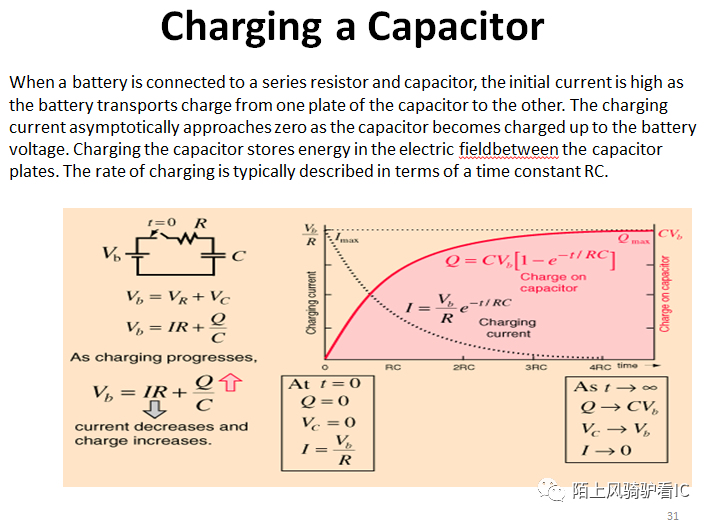

最大/最小转换时间: 用于约束信号沿时上升或下降过程所允许的最大或最小时间,在数字电路实现过程中,该值可以从库中转换,或使用命令set_max_transition,set_min_transition进行设置。两个值同时存在,工具在优化或检查时以最紧的为标杆,在电路中,通常输入端口的转换是通过driving cell或set_input_transition设置的,第一级std cell输入引脚的转换根据对应的net的RC计算得到,第一级std单元输出引脚的转换通过查表<单元输出转换= F(单元输入转换,单元输出负载)>得到,以此类推。任何一个结点的转换超过表值,都会报违反,都必须要修掉。

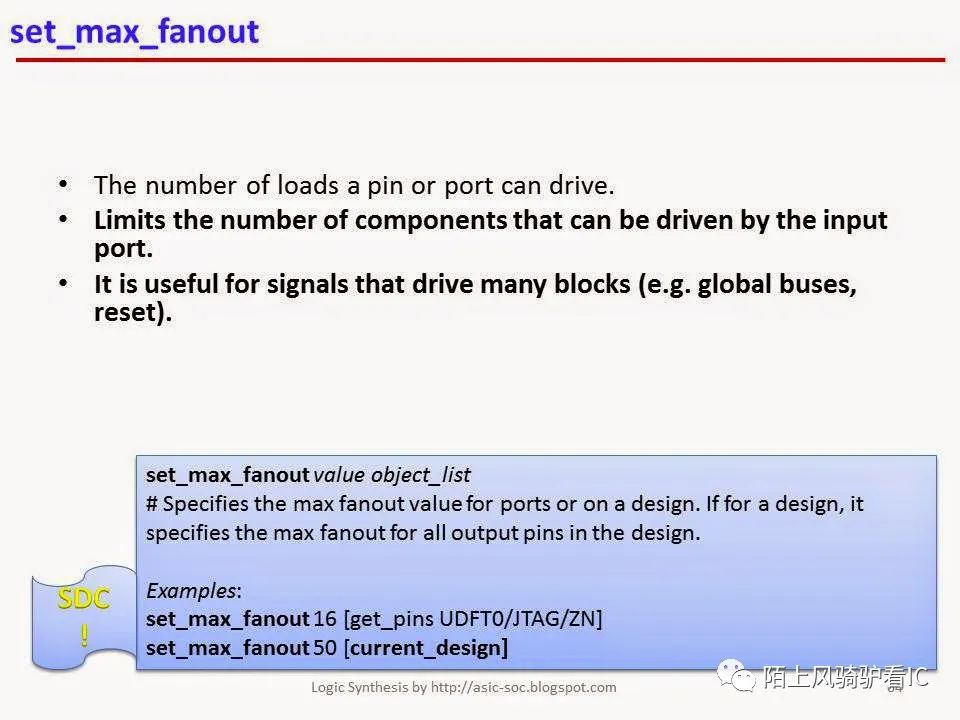

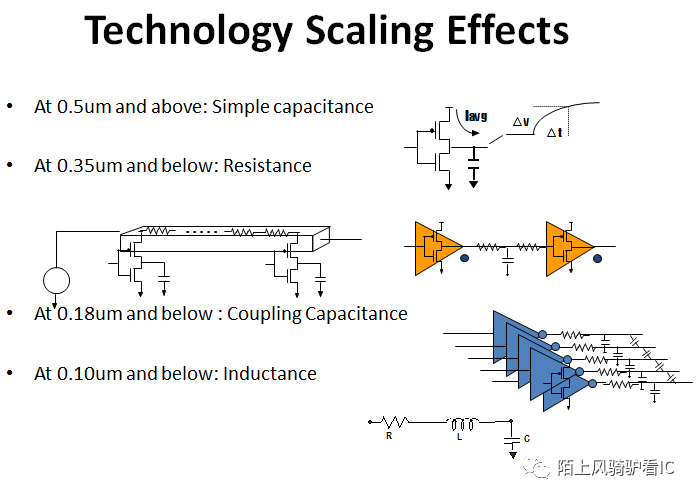

最大/最小扇出: 在老工艺的库中通常会有扇出的定义,在新工艺的库中通常都没有扇出的定义,所以在工具解析库时会报最大扇出未定义的警告,在实现过程中通常使用命令set_max_fanout / set_min_fanout来约束。所谓在先进工艺例程中,只要把max transition跟max capcitance修整干净,max_fanout并不是一个必须要遵守的硬规则。

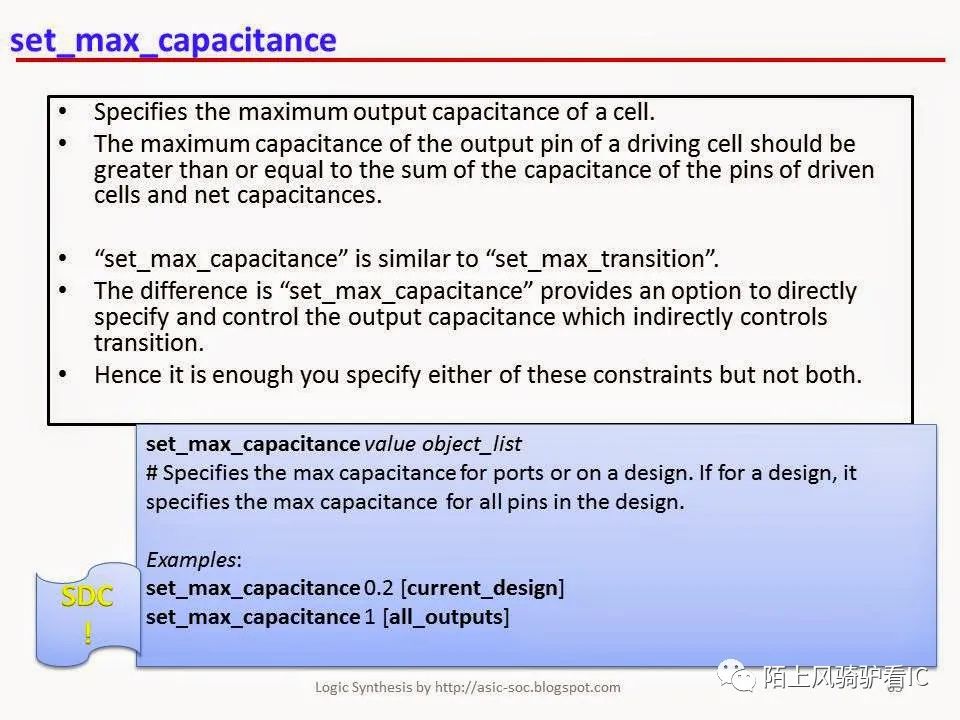

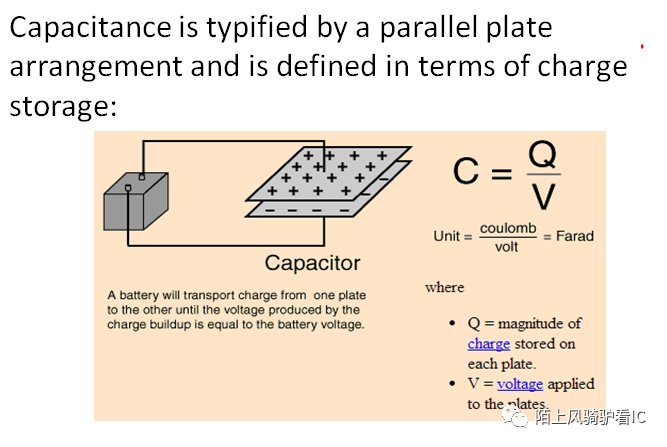

最大/最小电容: 定义单元输入或输出端口能够驱动的最大和最小负载电容,负载电容包括该引脚所驱动的网络电容跟引脚电容总和,在数字电路实现过程中,该值可以从库中识别,或用命令set_max_capacitance,set_min_capcitance定义,通常用命令设置的值不应该大于库中定义的值。同样在库中max_capacitance跟min_capacitance可能是一张一维或二维的表格,尺寸:因为负载电容会随频率变化,所以会在多个频点去K对应的max / min c电容值,此时库中的max / min c apacitance就是一张以频率为index的一维表。

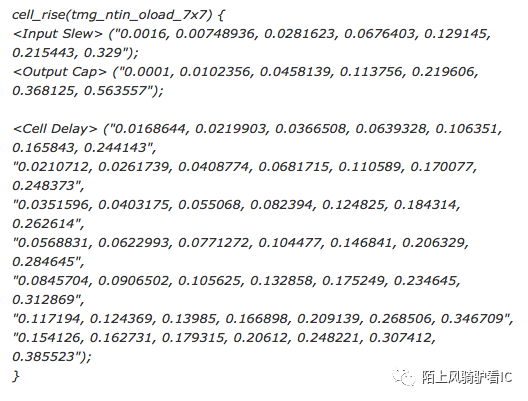

举个例子:下图是一颗卫星,电池的上升延迟的表,从表中可以得到,如果该电池的输入引脚的过渡小于0.0016ns或大于0.329ns或该电池的负载小于0.0001pf或大于0.563557pf就需要外插,一旦外插就要承担delay精确度损失的风险。

举个例子:下图是一颗卫星,电池的上升延迟的表,从表中可以得到,如果该电池的输入引脚的过渡小于0.0016ns或大于0.329ns或该电池的负载小于0.0001pf或大于0.563557pf就需要外插,一旦外插就要承担delay精确度损失的风险。

再回到文章开头的问题,分Ç apacitance DRC违规是否要修复?通过上面一通啰嗦,可知,所谓的逻辑DRC只是为了保证表值的精确度,如果超了表是否一定就会变石头?!当然不会,假设通过实测或仿真得到,在某个工艺点,外插入可以导致20%精确度的损失,如果DRC违反造成的延迟偏差已通过其他方式『挤压』回来了,则加了大小的不确定性且没有min period《论STA | 时钟分钟时间检查“或最小脉冲宽度”论STA | min脉宽》等违规,那这些DRC违规不修也不会变石头的。但是,强烈建议有DRC violaiton一定要修!

那么问题来了,修DRC通常有什么办法呢?通常,max logic DRC常用方法有:

-

永远是修DRC还是修timing还是修power,先修相声!

-

增加单元驱动:

-

升级单元以提高驱动强度

-

交换单元以缩短通道长度

-

交换细胞以降低Vt

-

动物理位置或线长:在实现工具中进行物理固定

-

为驱动器扇入锥中的逻辑部署类似的方法(适用于驱动器单元)。

-

负载分配(添加缓冲区)

-

尝试通过备用单元的移动/减少时序关键逻辑来消除拥塞区域。

最小 逻辑DRC修起来就比较简单,缩小大小 或交换成慢的引脚 电容大的单元,或者走一段蚯蚓线把电容增加,或者插个缓冲区。

驴说IC

本文转载于: 陌上风骑驴看IC [STA | 逻辑DRC]

2818

2818

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?