锁相环(PLL)作为一种确保系统同步的控制机制,广泛应用于频率合成、时钟恢复、信号调制与解调等多个方面。

探索锁相环(PLL)技术的深度和广度,最有效的途径之一便是通过专业书籍的系统学习。以下是为渴望掌握PLL知识的读者精心挑选的几本必备书籍,它们将引导您从基础理论到高级应用,全面深入地理解PLL的设计与应用。

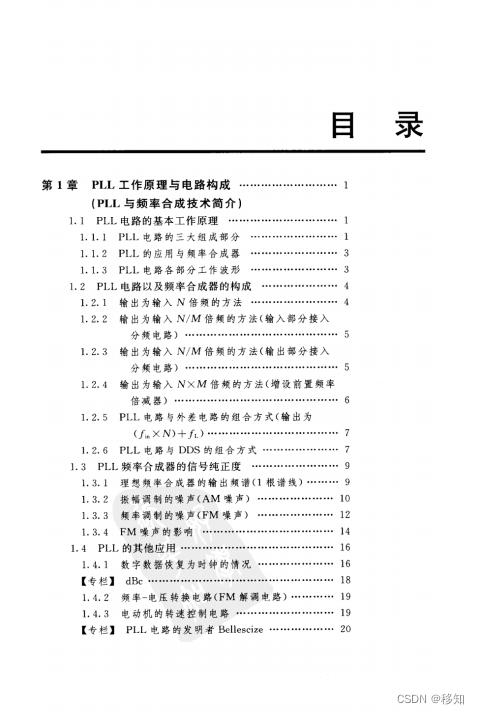

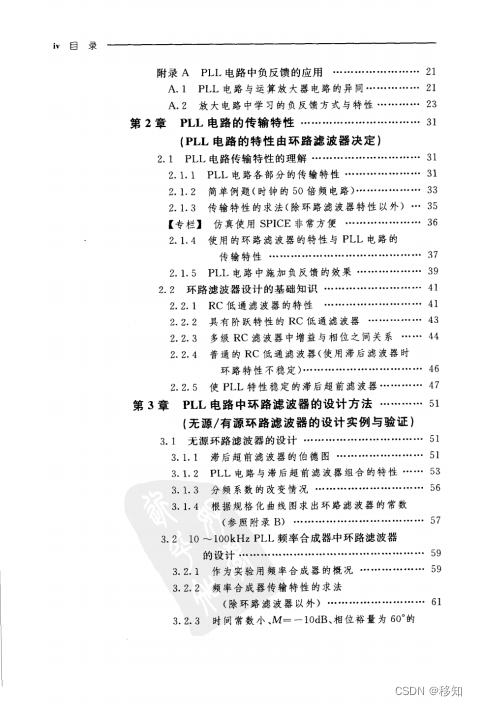

《锁相环(PLL)电路设计与应用》

作者:远坂俊昭

对于想要深入学习PLL的读者来说,这本书是一个不错的选择,可以帮助他们从基础概念开始,逐步深入到PLL的高级设计和应用中。逐步深入到复杂的设计和性能优化问题。

本书的内容丰富,覆盖了PLL的工作原理、电路构成、传输特性、滤波器设计方法、测试与评价技术,以及特性改善技术等多个方面。

本书适合电子工程领域的学生、研究人员以及从事相关工作的工程师。无论是对PLL技术感兴趣的新手,还是希望提升自己在该领域专业技能的资深专业人士,都可以从本书中获得宝贵的知识和启发。

通过系统地学习本书的内容,读者将能够设计出更加稳定、精确且高效的PLL电路,以满足日益增长的行业标准和性能要求。

《射频微电子》

作者:Behzad Razavi

《射频微电子》(RF Microelectronics )是一本专注于射频微电子领域的专业书籍,它详细讨论了射频电路设计中的各种概念和组件,包括锁相环(PLL)。这本书的第八章至第十一章对锁相环进行了深入的讨论。

◉第八章:讲解了VCO(电压控制振荡器)的相关知识。

◉第九章:介绍了锁相环的基本概念,包括鉴相器(phase detector, PD)的作用和工作原理。

◉第十章:讨论了整数分频器的设计与应用。

◉第十一章:则深入探讨了小数分频器的技术细节。

这本书适合那些希望在射频微电子领域,特别是在锁相环设计方面有所提高的工程师和学生。它详细讲解了VCO、鉴相器、分频器等PLL关键组件的设计和工作原理。还包含实际设计案例和技巧,有助于读者更好地理解和应用锁相环技术。

拉扎维的《射频微电子学》的中文翻译是余志平和清华大学微电子学研究院的周润德教授以及修过这门课的博士研究生门一起完成的,电子稿全文208页,如有需要,可联系老师领取。

1488

1488

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?