在数字设计的世界中,验证是确保硬件设计满足预期功能和性能要求的关键步骤。SystemVerilog作为一种先进的硬件描述语言,以其强大的验证特性,成为了设计和验证工程师的首选工具。

1. SystemVerilog验证的重要性

在数字设计流程中,验证是确保设计符合预期功能的关键步骤。SystemVerilog的验证方法包括功能仿真、形式验证和断言检查等,它们共同构成了一个全面的验证策略。

2. SystemVerilog的关键特性

面向对象编程: SystemVerilog支持面向对象的编程范式,使得设计模块化和重用变得更加容易。

并发建模: 通过并发语句和时序控制,SystemVerilog能够模拟复杂的时序行为。

断言和覆盖率: SystemVerilog的断言(Assertions)和覆盖率(Coverage)工具帮助工程师验证设计是否符合规范,并确保所有可能的执行路径都经过测试。

3. SystemVerilog在验证中的应用

模块验证: 使用SystemVerilog可以创建测试环境来验证单个模块的行为。

集成验证: 在模块验证的基础上,SystemVerilog支持更高层次的集成验证,确保不同模块间的接口和交互符合设计要求。

回归测试: SystemVerilog的自动化测试框架可以简化回归测试过程,确保设计更改不会引入新的错误。

SystemVerilog验证是确保数字设计质量和可靠性的关键。通过掌握SystemVerilog的验证工具和技术,工程师可以提高验证的效率,减少设计周期,并最终推出更加可靠的产品。

《SystemVerilog验证测试平台编写指南》是一本专为那些渴望深入掌握SystemVerilog验证技术的工程师和学生编写的专业书籍。本书不仅涵盖了SystemVerilog语言的核心概念,还通过丰富的实例和案例分析,展示如何利用SystemVerilog的特性,高效构建和优化一个既符合设计需求又满足验证标准的测试平台。

内容概括:

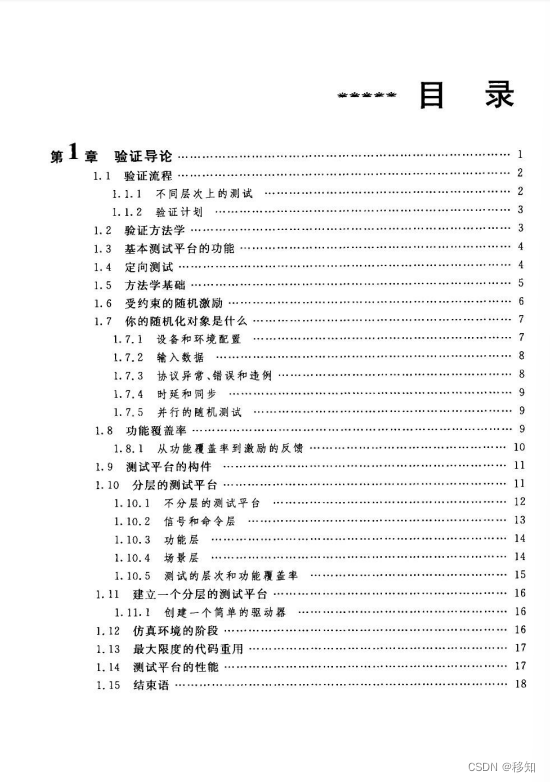

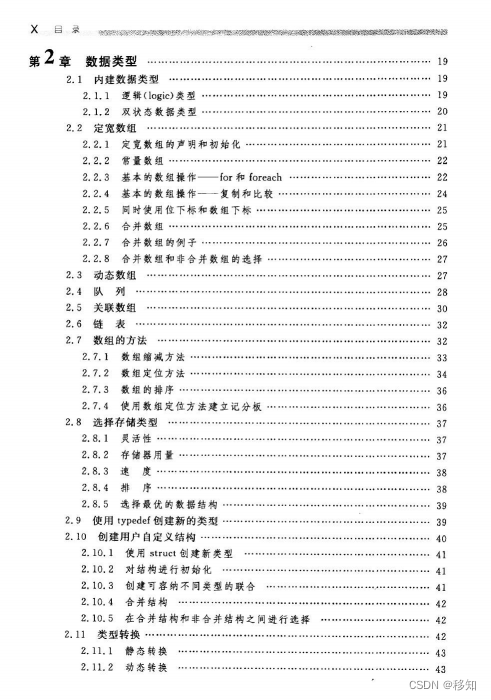

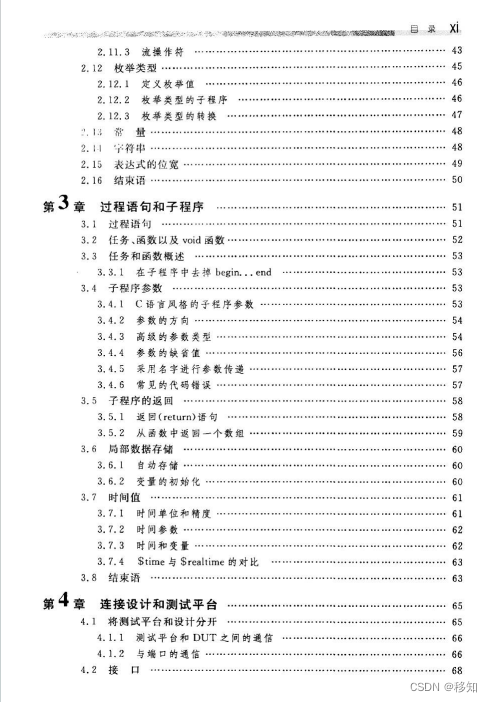

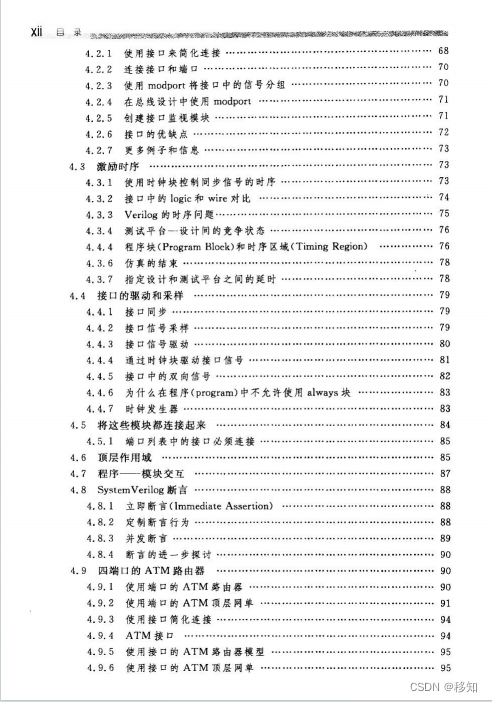

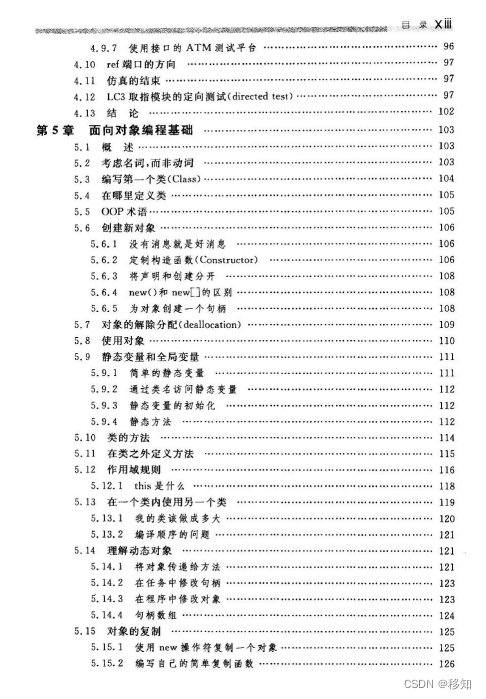

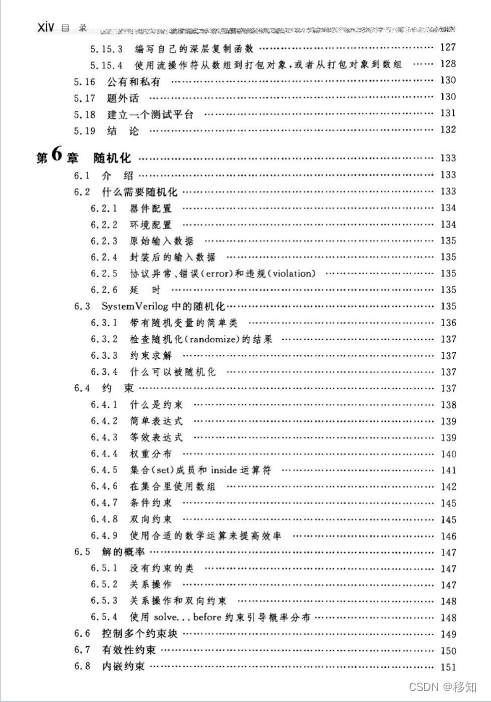

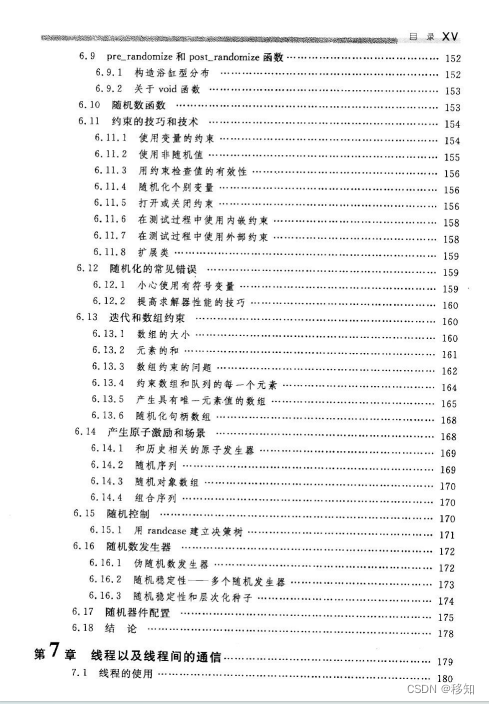

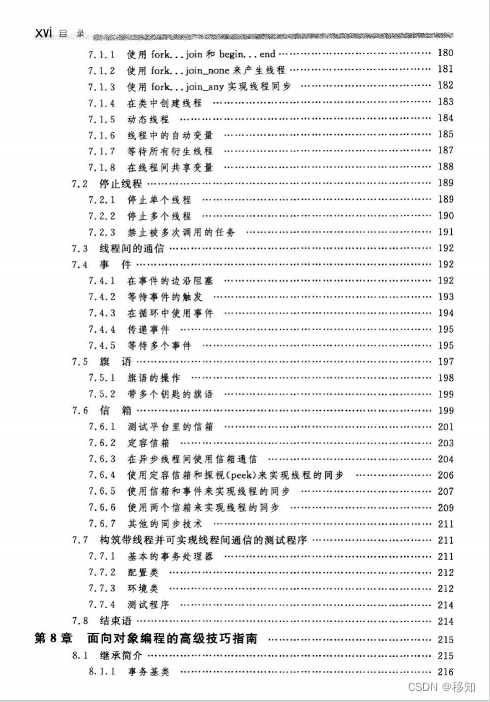

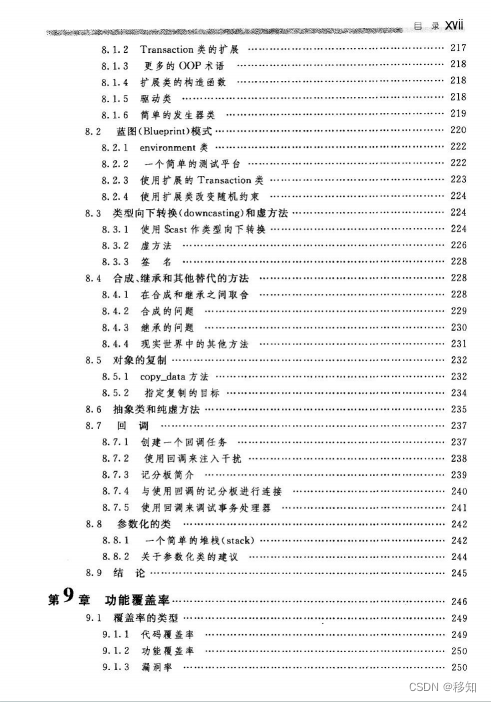

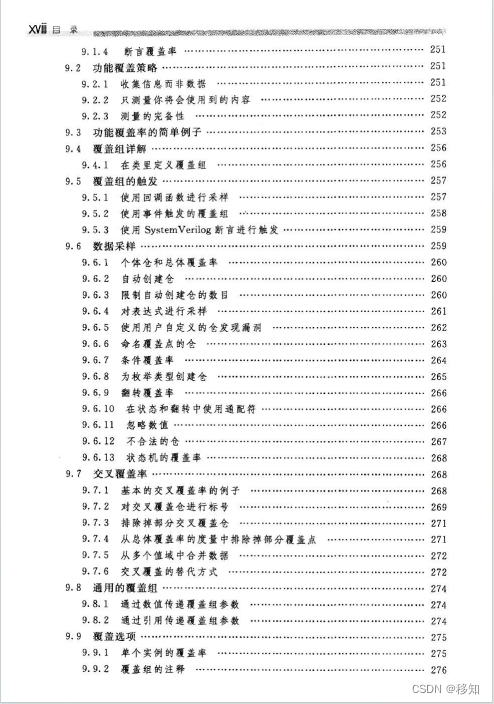

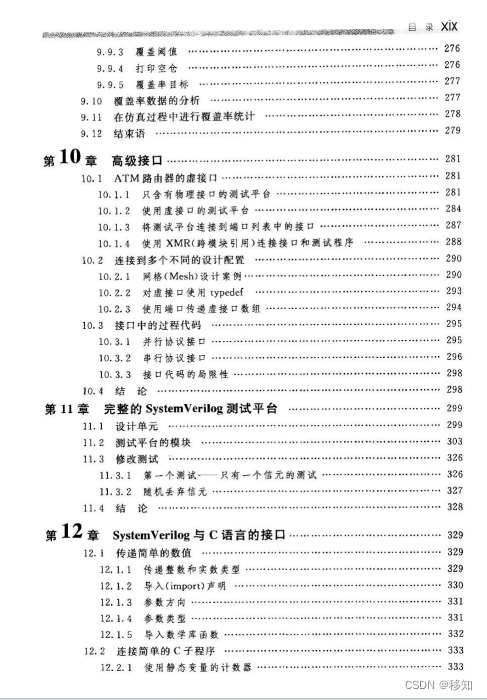

本书从SystemVerilog语言的基础出发,逐步深入到验证测试平台的构建策略。内容涵盖了数据类型、过程语句、子程序、面向对象编程基础、随机化技术、线程及其通信、高级接口技术等多个方面。每一章节都配有实际的代码示例和应用场景,使读者能够快速理解和掌握关键概念。

覆盖率驱动的测试: 强调了功能覆盖率在验证过程中的重要性,并提供了如何使用覆盖率来指导和衡量验证进度的方法。

随机化技术: 深入讨论了SystemVerilog中的受约束随机激励产生机制,帮助读者理解如何生成有效的测试用例。

多线程和通信: 展示了如何在测试平台中创建和管理多线程,以及如何实现线程间的数据交换和同步。

方法学的重要性: 书中不仅介绍了语言特性,还强调了验证方法学的重要性,帮助读者构建可靠且可重复的验证环境。

在本书中,介绍了SystemVerilog语言的工作原理,重点讲解了如何利用面向对象编程(OOP)的方法,构建由覆盖率驱动且受约束的随机分层测试平台。讨论了SystemVerilog与C语言的接口技术,通过丰富的实例和引导性的建议,本书将帮助读者理解并应用类、随机化、功能覆盖率等关键概念,以创建高效、可靠的测试平台。

面向对象编程(OOP)的应用

本书特别强调了面向对象编程在SystemVerilog验证中的重要性,详细介绍了如何利用SystemVerilog的OOP特性来创建模块化、可重用的测试组件。

与C语言的接口技术

书中描述了如何使用直接编程接口把C或C十十代码与 SystermVerilog 连接起来,这对于需要在验证过程中集成C语言模块的工程师来说,是一个宝贵的资源。

目标读者:

本书由资深数字电路工程师克里斯·斯皮尔(Chris Spear)撰写,他凭借多年的行业经验和对软件编程的深刻理解,为我们提供了一本深入浅出、实用导向的指导手册。适合具有一定Verilog编程基础的电路工程技术人员,以及高等院校电子类、自动化类、计算机类的学生。对于初学者,书中对SystemVerilog与其他编程语言的差别进行了清晰的阐述,非常有助于理解。

本书籍共387页,要想pdf版本,可联系老师领取

随着SystemVerilog语言的出现,统一的设计和验证语言已成为可能,这不仅促进了设计和验证工程师之间的沟通,还提高了整个验证流程的效率。

在数字设计的旅程中,验证是一个不可或缺的里程碑。《SystemVerilog验证测试平台编写指南》将作为您的指南针,引导您在复杂的设计验证领域中,找到最直接、最有效的路径。

224

224

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?