基于FPGA的2DPSK调制解调程序,verilog实现,含仿真和说明。

ID:36300630866693502

小马哥FPGA

基于FPGA的2DPSK调制解调程序,verilog实现,含仿真和说明。

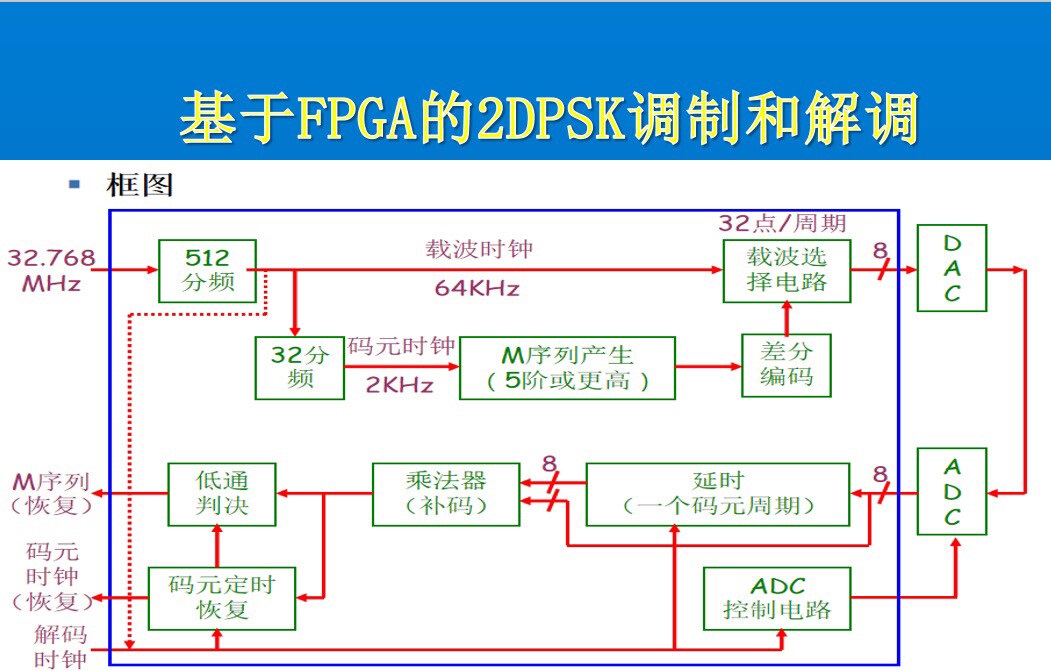

在现代通信领域,数字调制技术是一项重要的研究课题。2DPSK(二进制差分相移键控)调制技术作为一种高效的数字调制方法,被广泛应用于无线通信领域。本文将介绍一种基于FPGA的2DPSK调制解调程序的设计与实现,采用Verilog语言进行编码,并进行了仿真和详细说明。

首先,我们对2DPSK调制解调的原理进行简要介绍。2DPSK调制是一种相位调制技术,它通过改变信号的相位来传递信息。在2DPSK中,每个符号代表两个比特,通过将每个符号映射到相位空间中的一个点来实现。解调过程是将接收到的符号映射回比特流。2DPSK调制解调具有高效利用频谱、抗抑制和抗多径干扰等优点,因此在无线通信领域得到了广泛应用。

接下来,我们详细介绍了基于FPGA的2DPSK调制解调程序的设计与实现。本文中,我们选择Verilog语言作为设计语言,并借助FPGA平台实现硬件加速。Verilog语言是一种硬件描述语言,具有高度抽象、可综合和可仿真的特点,非常适合用于数字电路设计。FPGA是一种可编程逻辑器件,可以实现多种数字电路,并具有可重构性和灵活性。

在设计过程中,我们首先根据2DPSK调制解调的原理,将其分解为多个模块,每个模块负责完成特定的功能。在调制端,我们设计了位流生成模块、相位映射模块和信号输出模块,分别用于生成比特流、将比特映射到相位空间,并将调制后的信号输出。在解调端,我们设计了信号接收模块、相位解映射模块和比特恢复模块,分别用于接收信号、将接收到的信号映射回比特流,并实现比特恢复。这些模块通过互联,构成了完整的2DPSK调制解调系统。

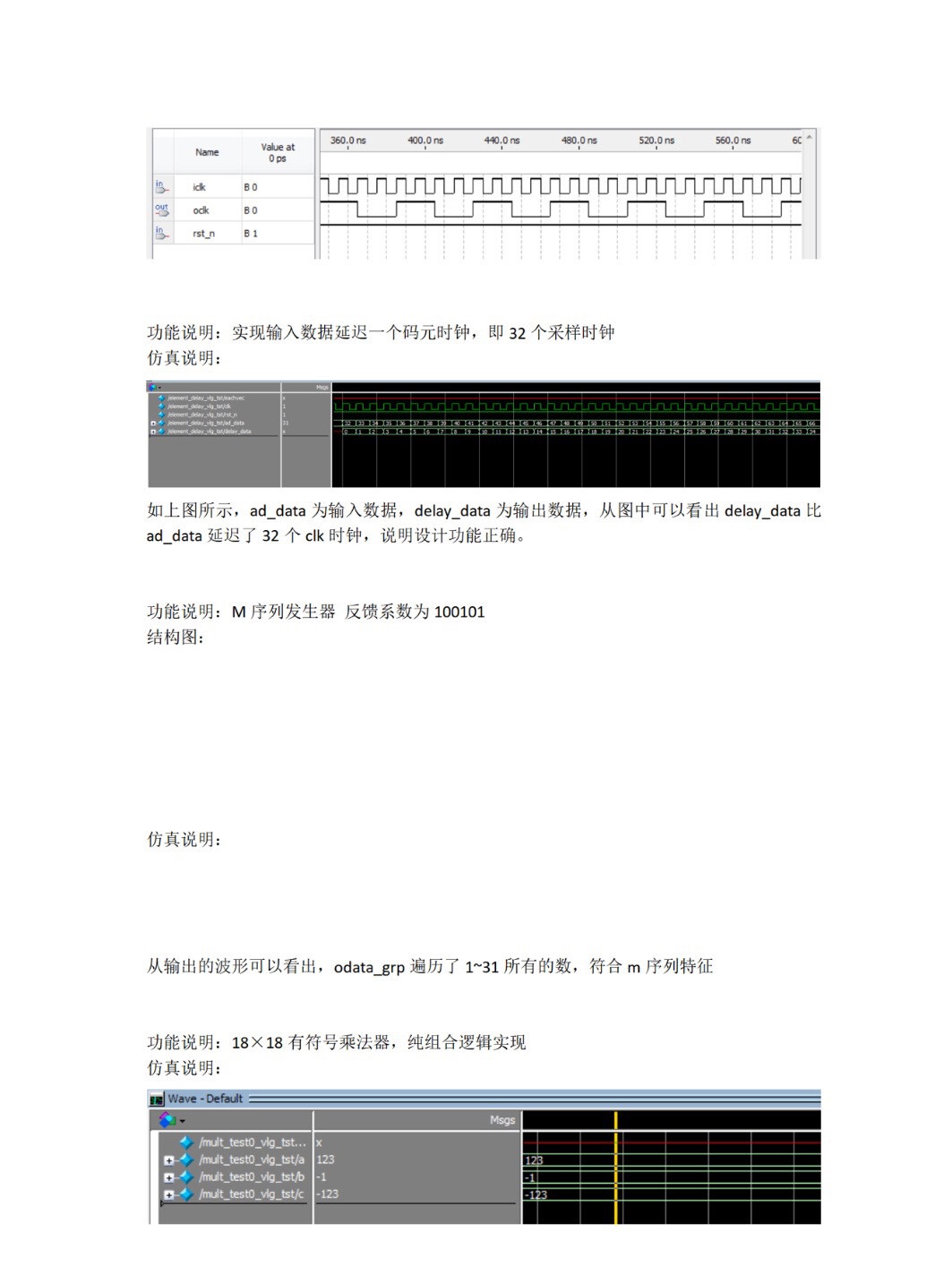

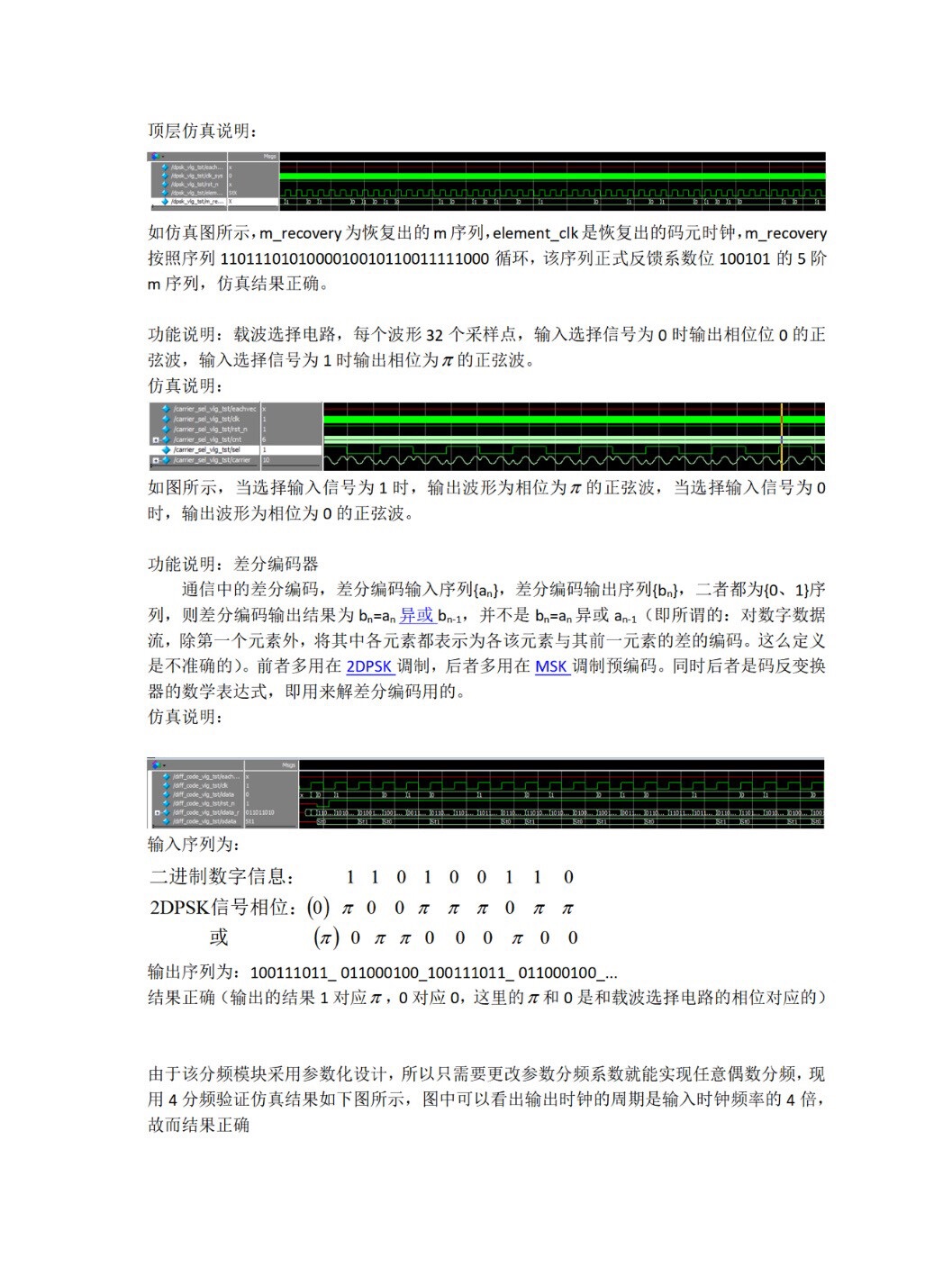

为了验证设计的正确性和可行性,我们进行了仿真实验。通过使用Verilog仿真工具,我们对设计的2DPSK调制解调程序进行了功能仿真和时序仿真。在功能仿真中,我们验证了各个模块的功能正常,并得到了正确的调制解调结果。在时序仿真中,我们分析了不同输入条件下系统的时序性能,并对整个系统进行了优化。

最后,我们对基于FPGA的2DPSK调制解调程序进行了详细的说明。我们介绍了程序的运行流程、模块之间的数据传输方式以及设计中使用的关键算法。通过说明,读者可以更深入地理解程序的实现原理,同时也为读者提供了参考,方便他们在类似的项目中进行设计和实现。

综上所述,本文基于FPGA的2DPSK调制解调程序的设计与实现,通过Verilog语言进行编码,并进行了仿真和详细说明。该程序具有高效性、可靠性和可扩展性,并在实际应用中具有较好的性能。我们相信这个设计与实现的过程和结果,对于学习和研究数字调制技术以及FPGA应用具有一定的参考价值。

相关的代码,程序地址如下:http://imgcs.cn/630866693502.html

1096

1096

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?