1、创建project,加入source Verilog和

constraint set_delay.xdc

set_max_delay -from [all_inputs] -to [all_outputs] 10

2、如果需要跑仿真,看时序图时,需要添加panda_tb.v文件和value.txt ,并修改数据

修改相关端口,实例化

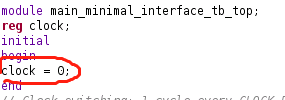

当为1时,会触发上升沿

通过反正仿真看时序图

2、利用脚本自动测数据

create_project s8_u8_u8 /home/cpan/workspace/6-20-vivado/12-21-dsp-data/order_dsp/s8_u8_u8 -part 7vx485tffg1761-2

add_files -norecurse /home/cpan/workspace/6-20-vivado/12-21-dsp-data/order_dsp/s8_u8_u8.v

add_files -fileset constrs_1 -norecurse /home/cpan/workspace/6-20-vivado/12-21-dsp-data/order_dsp/set_delay.xdc

update_compile_order -fileset sources_1

launch_runs impl_1 -jobs 1

close_project

3、

4、

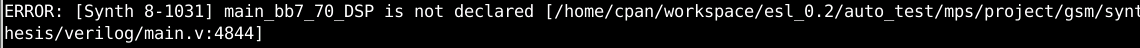

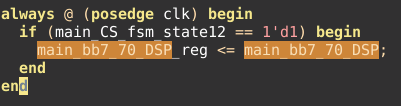

logical信号的命名规则不对

setOutputRegister(out_pin, start_state);

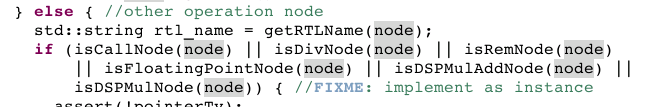

std::string RTLBuilder::getLogicOutName(Node *node, bool pointerTy)

2375

2375

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?