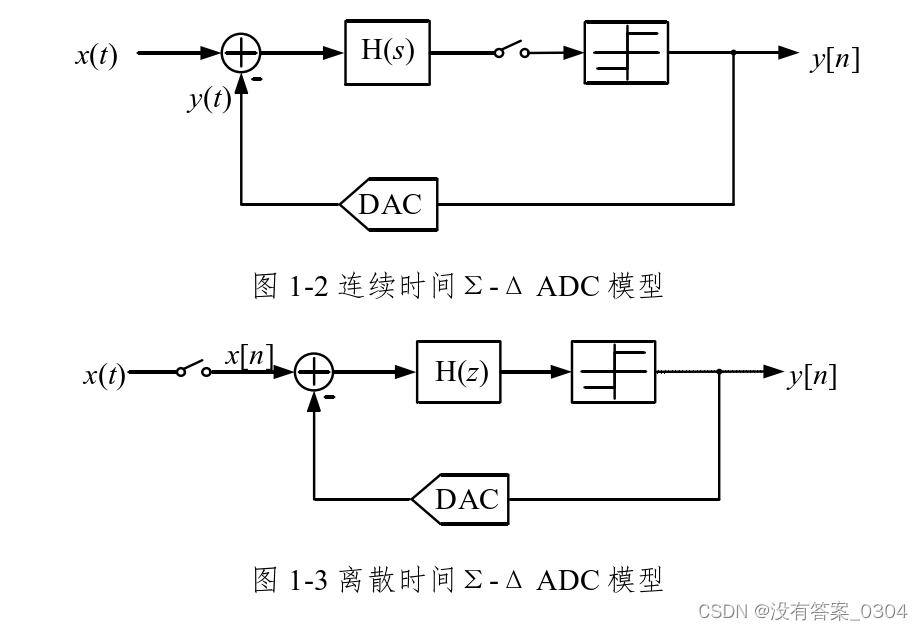

根据采样方式的不同,Σ-ΔADC又分为连续时间型和离散时间型。

连续时间型Σ-ΔADC采用电阻电容积分器,其采样电容位于积分 器之后,如图 1-2所示,无需额外的抗混叠滤波器,具有天然的抗混叠滤波效 果,通常在相对较高频率应用场景使用,但由于电阻工艺误差较大,较难实现高精度,其输出精度一般在14位以下;

离散时间型Σ-Δ ADC采用开关电容积分器,采样电容位于积分器输入之前,与连续时间型不同采样之前需要经 过抗混叠滤波以防止频谱混叠,如图 1-3 所示,由于电容匹配性相对电阻较好, 故离散时间Σ-ΔADC能够实现较高的精度,但由于采用开关电容积分器,电容充电稳定时间较长,较难在高精度的同时实现高速率,一般应用于中低速高精度应用场景,目前离散时间Σ-Δ ADC一般可以实现16位以上的精度。

增量Δ Σ原理的连续时间实现是很有吸引力的,因为它大大简化了驱动电路[ 2 ]。这种优势源于CT Δ Σ M的阻性输入阻抗,得益于此,前级不再面临驱动开关电容负载的前景。这反过来又降低了驱动放大器的功耗,简化了系统设计。此外,aCT Δ Σ M的电流消耗可以预期低于其离散时间的消耗。

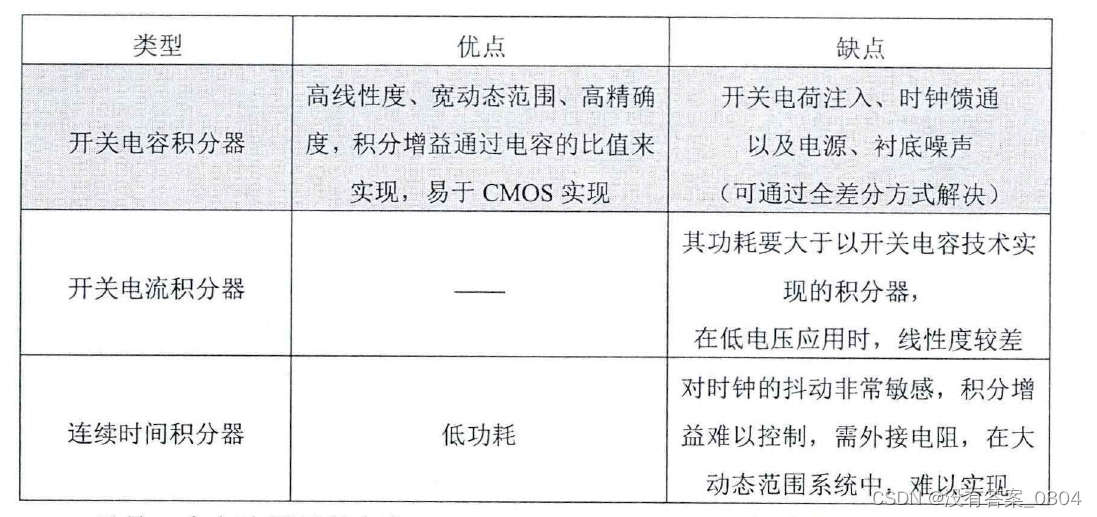

开关电容积分器的积分增益通过电容的比值来实现。这种实现方式不仅使得电路结构变得简单,且因为该电路中 的信号是用电荷而不是电流来表示的,因此时钟频率的漂移和抖动并不会影响电路的转换精度,yinci可以实现高精度转换。

连续时间ADC的环路滤波器比DT型复杂

2243

2243

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?