sa_double_tail比较器 --Trannoise、pnoise、offset、MC仿真

一、Tran noise:

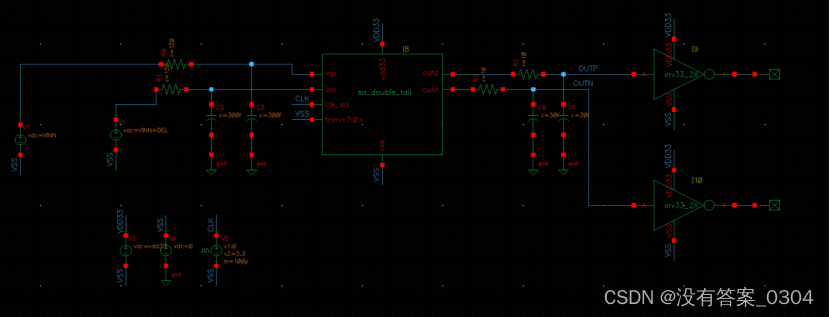

1、在输入端加一个DC的差(比如一端是0.5VDD,另外一端加0.5VDD+DEL mV);

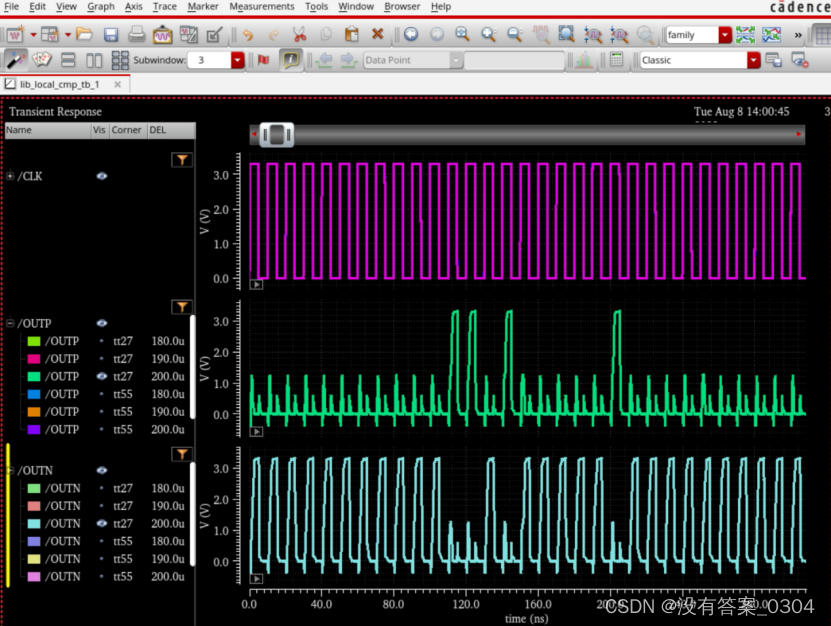

2、计算仿真时间内的counting number,和实际的correct counting number(本例中时钟频率是100MHz,仿真时间是10us,那么应该是1000个counts;用calculator计算实际的counts);

3、扫描不同的输入DC差之下,正确的counts的数量(输入差是0.1mV,0.2mV,0.3mV);

当正确的counts数量大约是84%的时候,我们认为此时的input差就是一个sigma(50%+0.5*68%=84%正态分布);可以通过count number数不断将DEL误差减小,获得较为精确的input referred noise。

4、当PVT改变的时候,可以不断重复上面的步骤,来求得对应的sigma;

当input的差别很小的时候(Vip小于Vin),Von全部应该是1。但是由于noise的存在,导致某些错误的输出,用calculator计算出全部和正确的counts数量。当正确counts大概是84%,也就是对于一个input referred noise sigma.

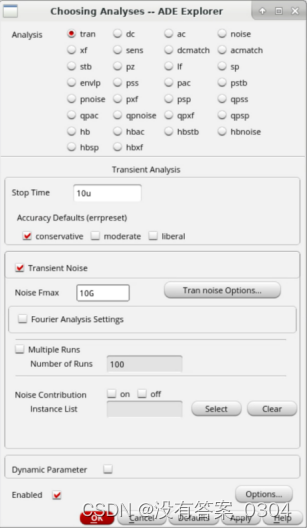

Trannoise设置:Noise Fmax设置的太大如100G,仿真速度会慢,可以设为10G或30G

Noise Fmax设置的值变大,等效输入噪声也会增大

查看count number数

方法一:measur

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5834

5834

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?