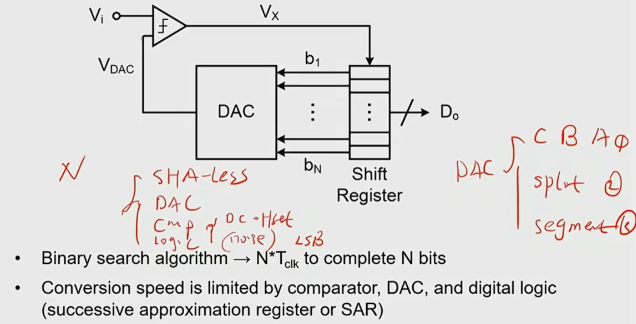

Successive Approximation ADC (SAR ADC)逐次逼近ADC:

用 时间 换取 精度&简单度。

瓶颈(基本上是所有ADC的瓶颈):SHA、DAC、CMP、Logic。

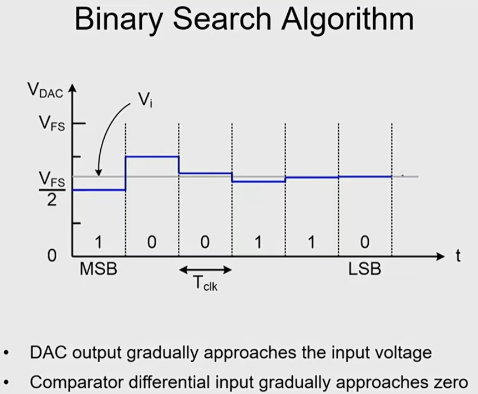

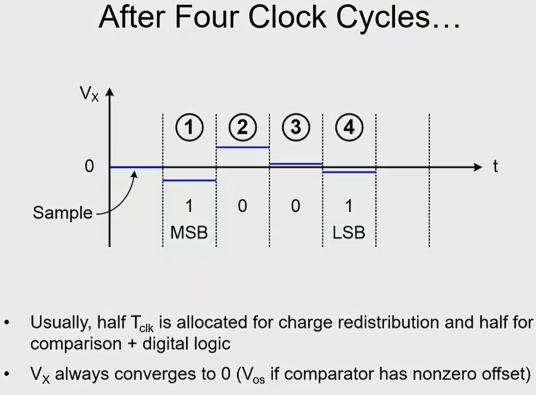

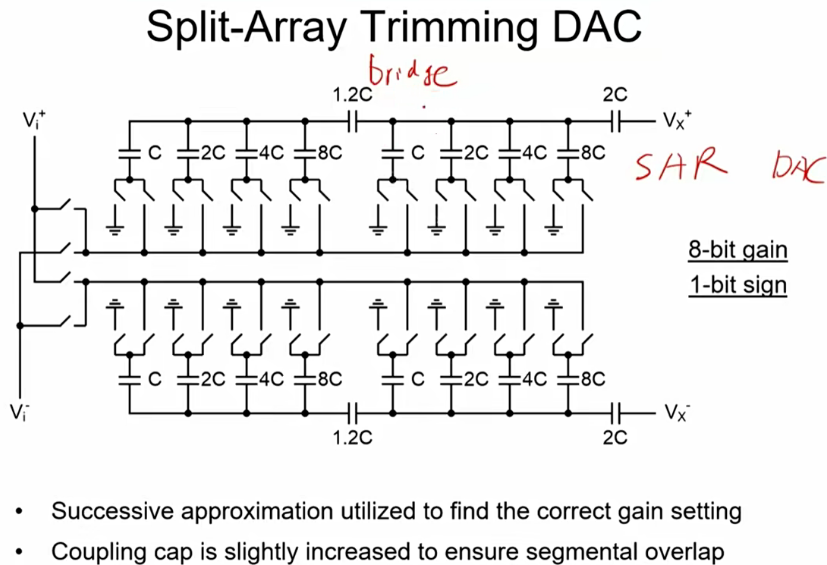

对于SAR来讲:①没有了SHA,可以大大节约功耗。②SAR中只要一个比较器,不存在多个比较器之间带来的误差,可以专门优化一个比较器就行,对CMP_offset不敏感,对CMP_noise敏感。③DAC是SAR中一个主要的优化方向,有传统的二进制DAC,桥接DAC,分段segmentDAC 等。④Logic来说,SAR很简单,根据比较器的结果,反馈回DAC,改变DAC的值,因此对于CMP的gain & speed 提出了要求。

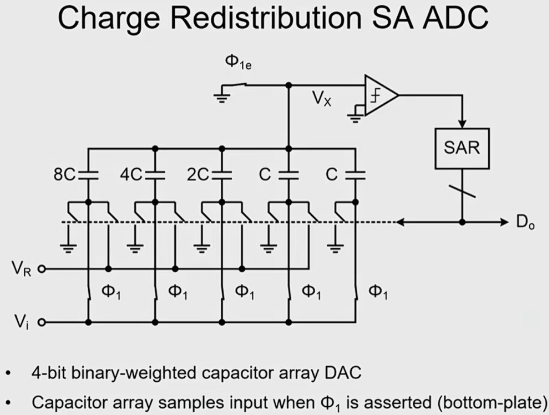

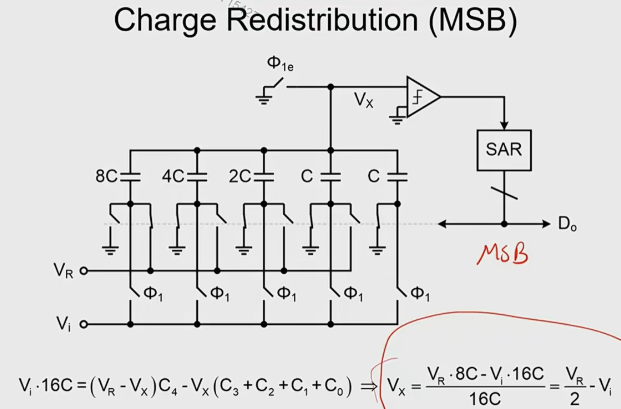

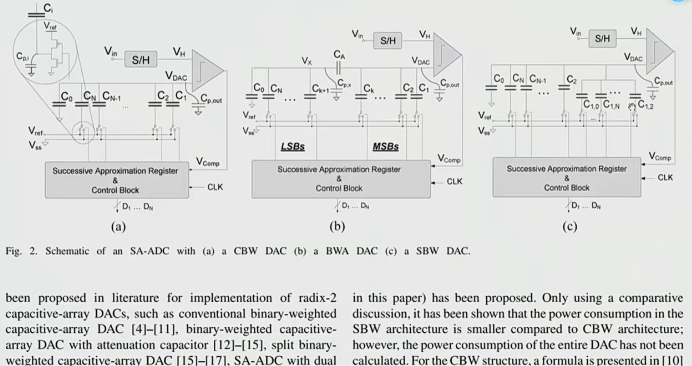

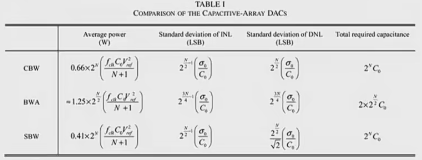

主要讲讲DAC:

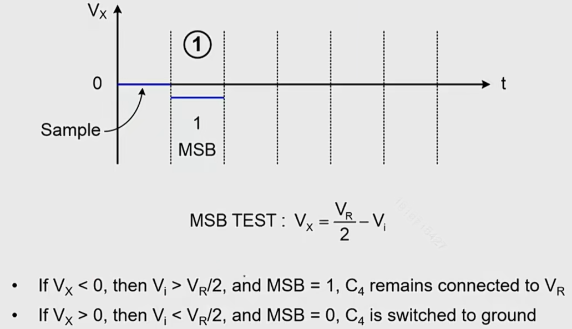

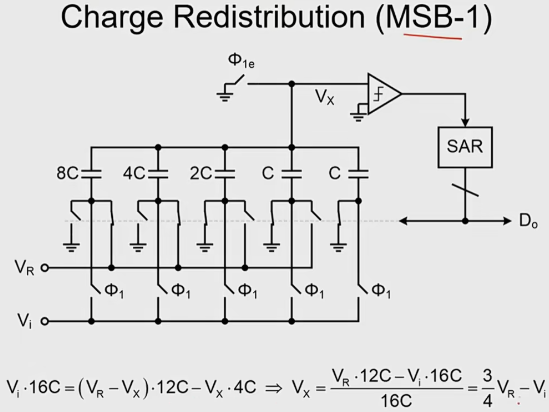

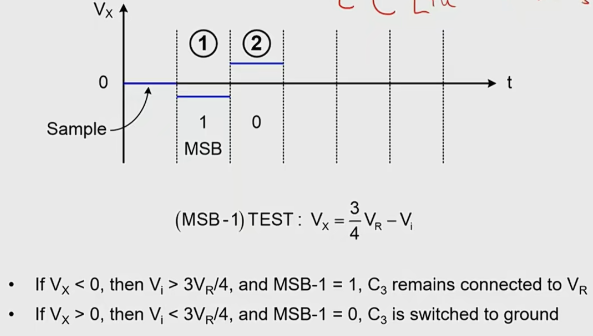

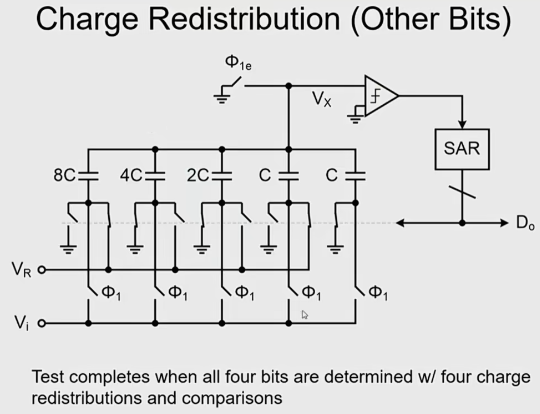

二进制电容,低极板采样(CMP_in 和 Vin 不在一个节点)(跟Vin不相关的一个开关先断开就叫低极板采样)。

sar 电容的翻转,本质是一个 try-correct 的过程,比较费功耗,所以很多研究怎样使得切换更智能一些,节省功耗。

带冗余位的DAC,(非二进制,sub二进制,redundant)_wenbo liu 的paper。

前面已经讲得比较清楚了。

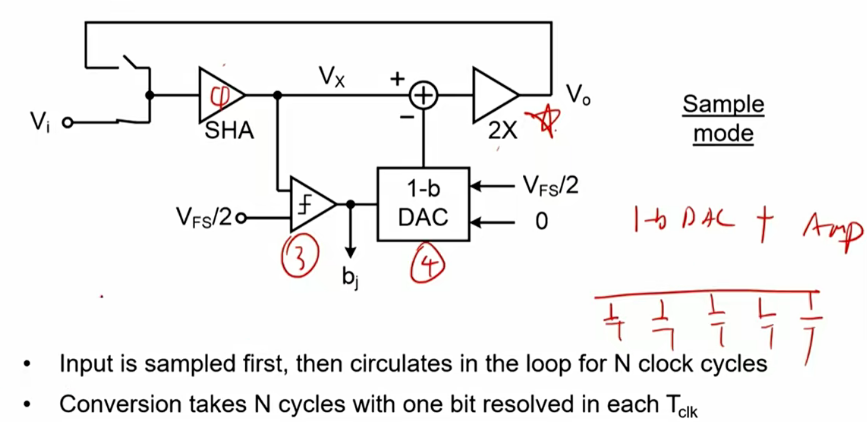

Algorithmic (Cyclic) ADC(算法ADC)

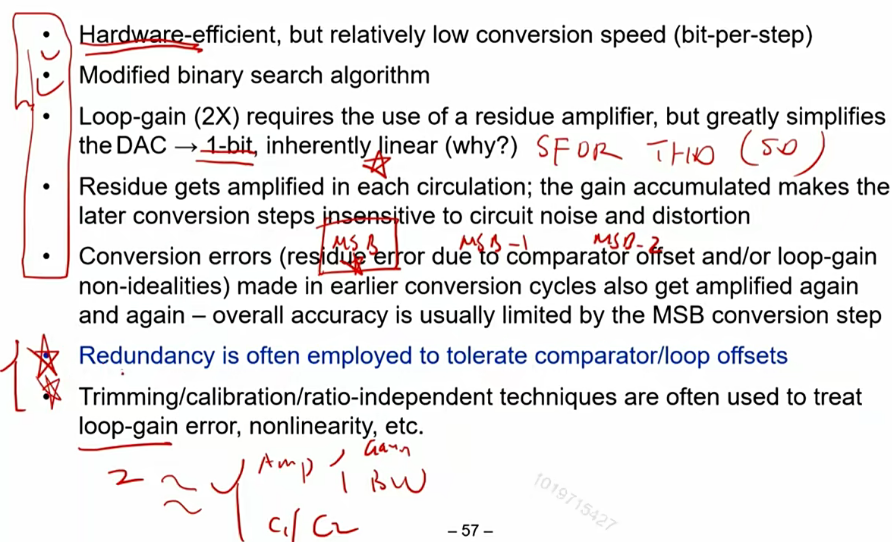

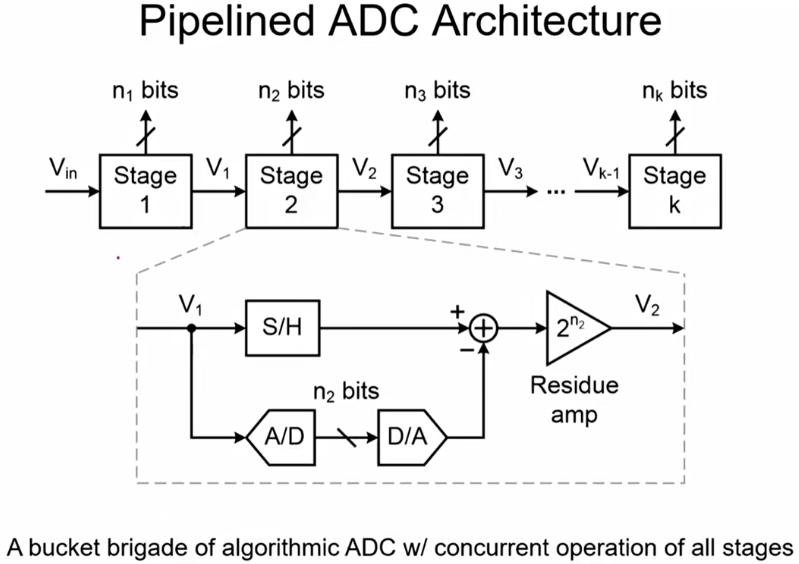

虽然Cyclic ADC用的少,但是是pipline ADC的基础。

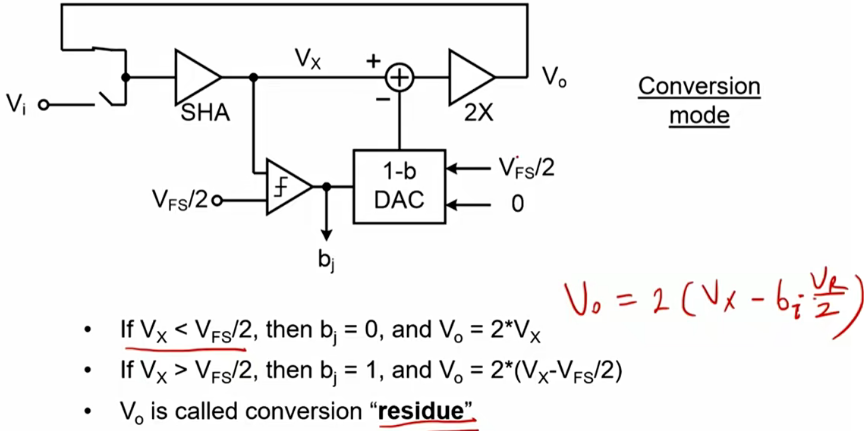

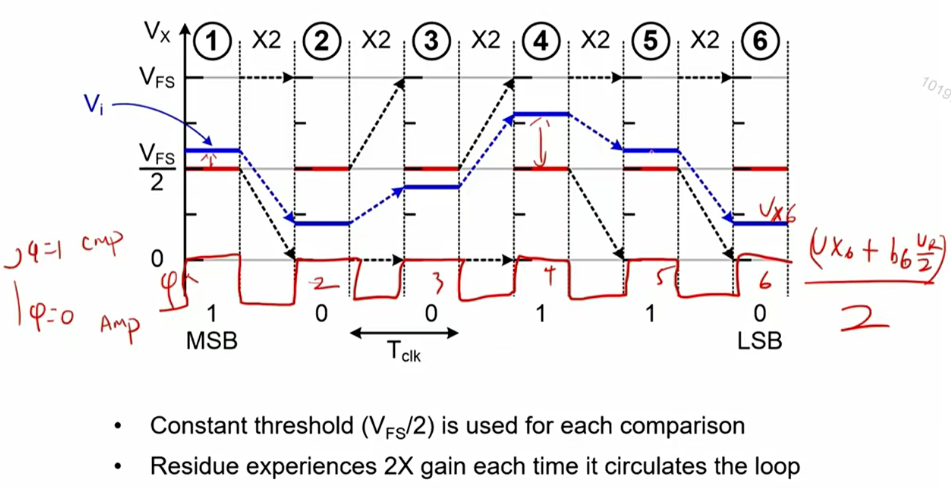

工作原理:

用一个1-bit DAC + 2X AMP 代替了sar中的电容阵列。每次比较后对输入信号进行 ± Vfs/2 。

![]()

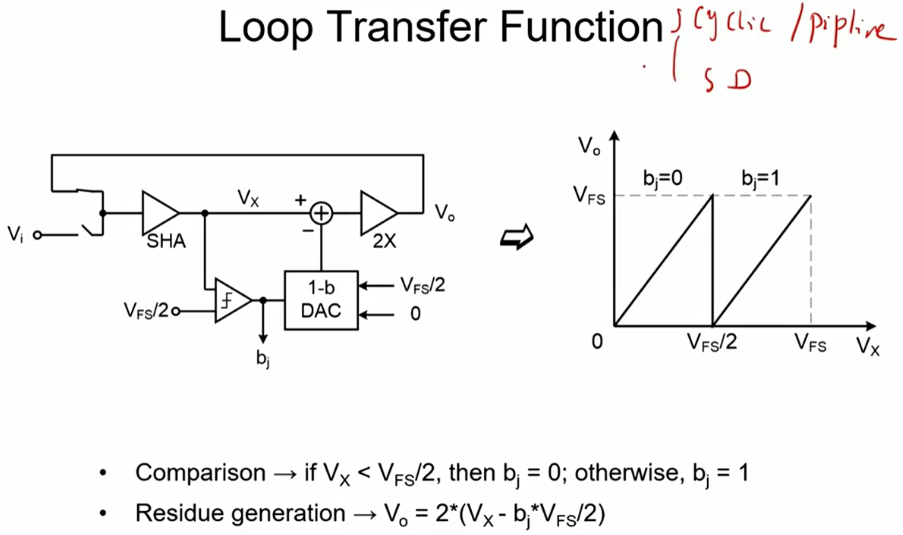

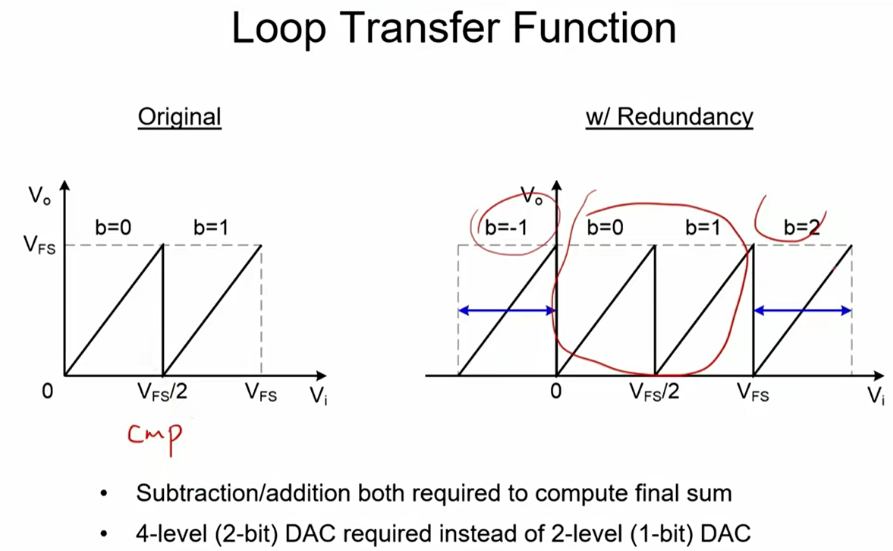

环路传递函数:![]()

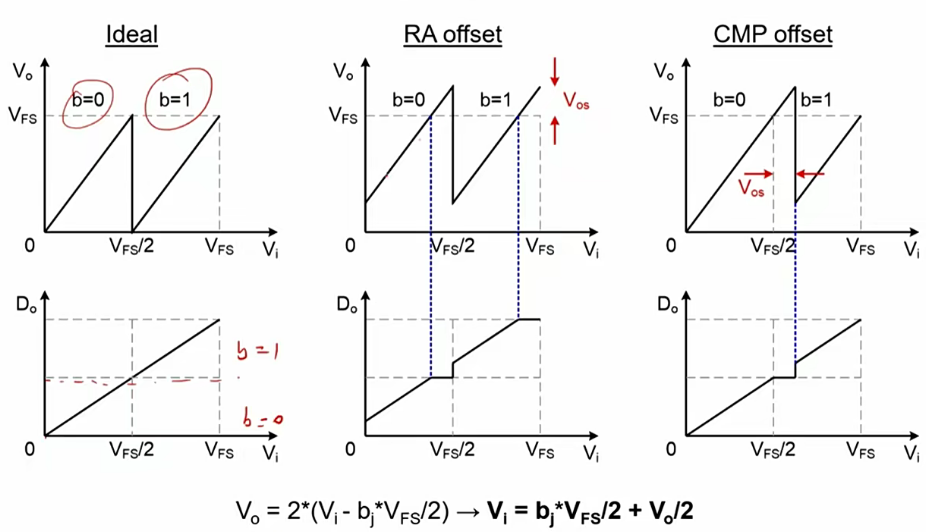

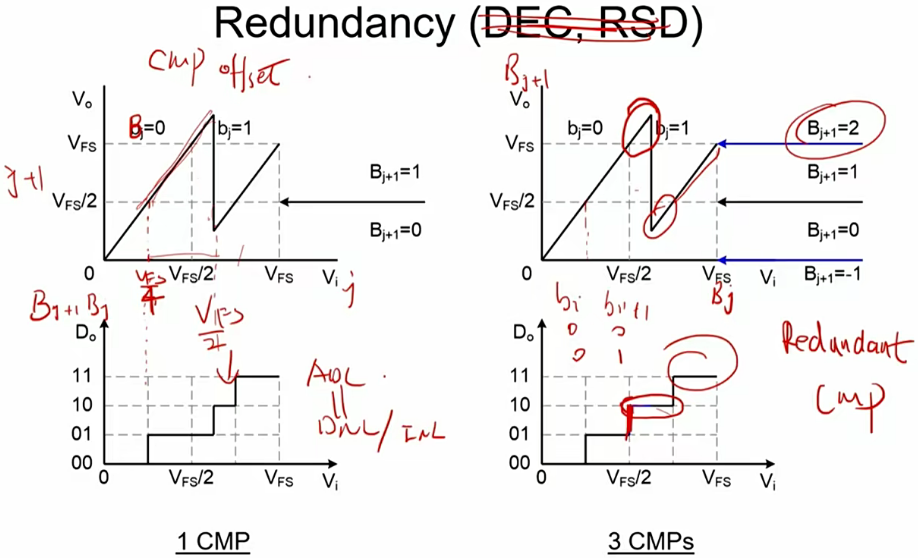

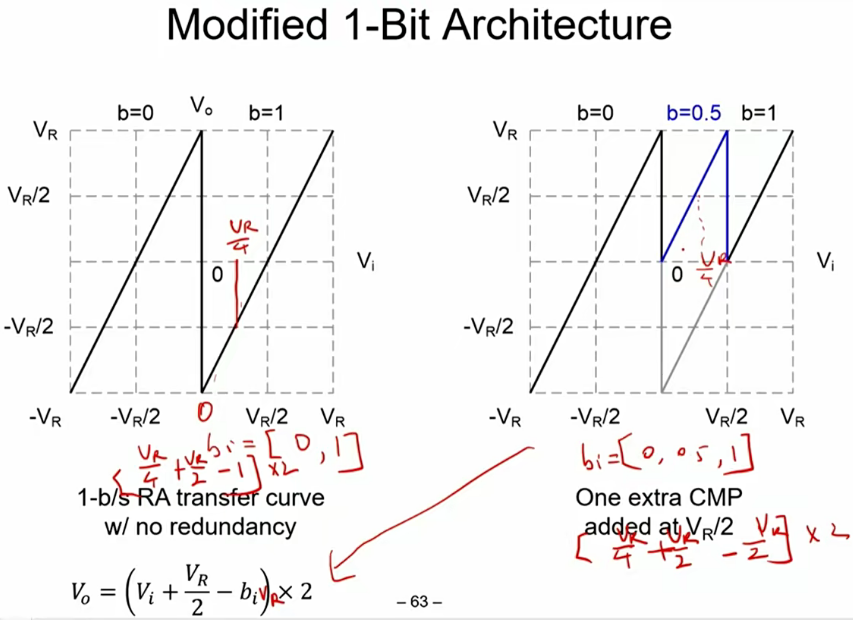

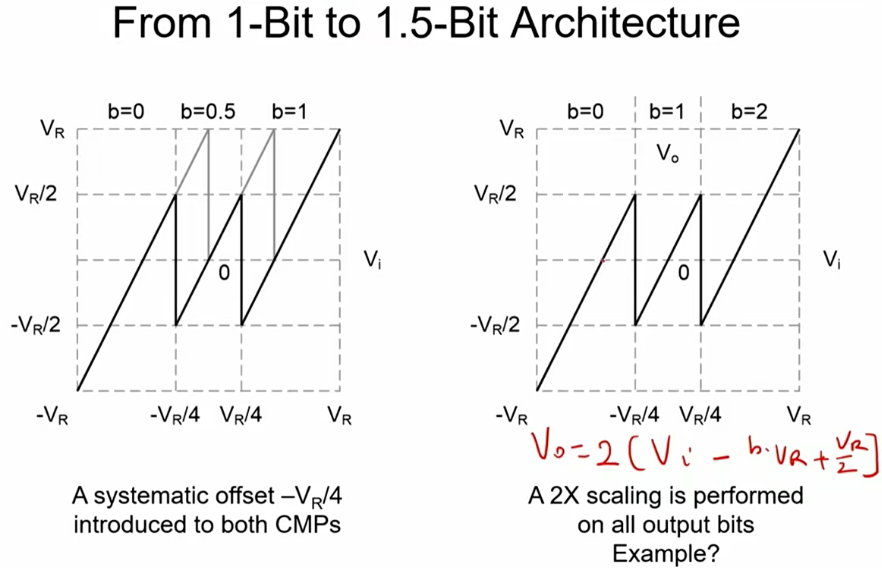

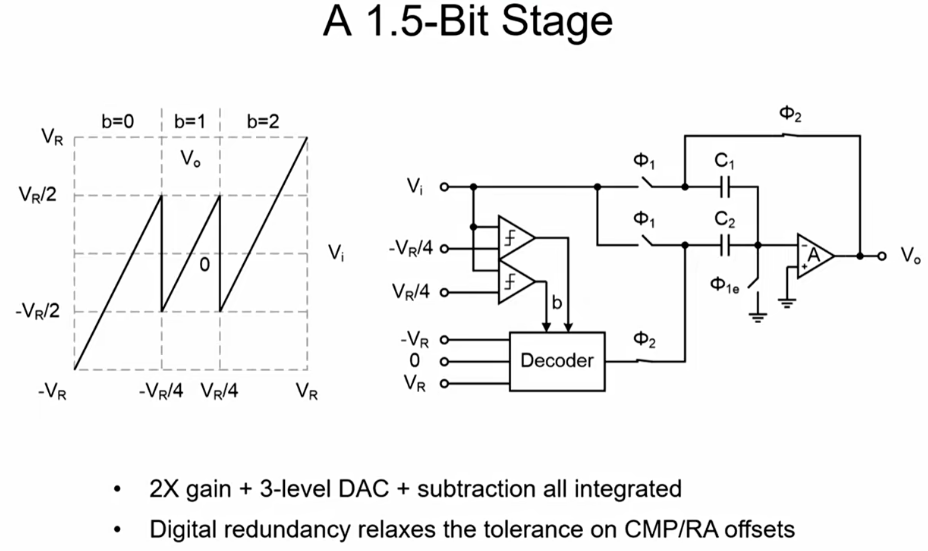

折一下代表比较器,比较器的非线性 导致了 传输函数曲线 上的非线性。每个bit 周期内,增益为2,( 每次对Vx进行减,区别在于是 -Vfs/2 还是 -0 )。每这一下就代码一个新的bit周期。

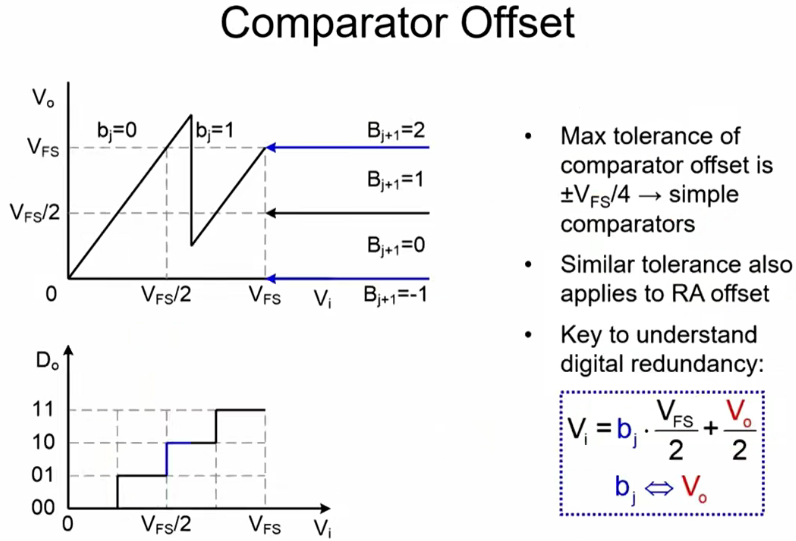

Offset anf Redundancy

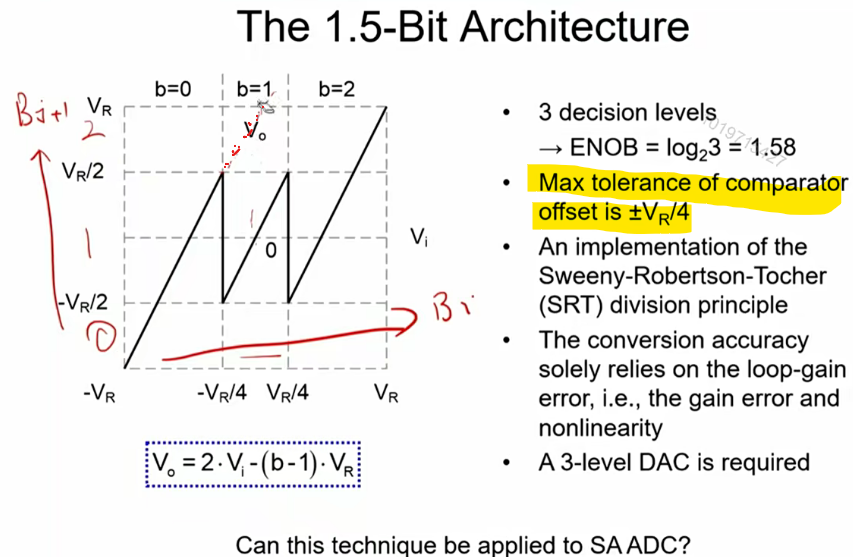

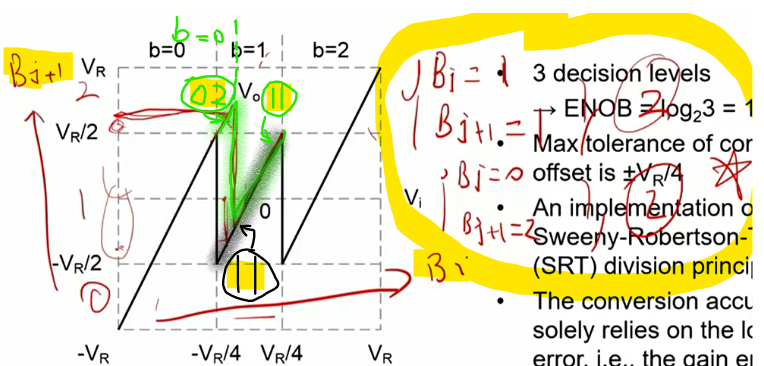

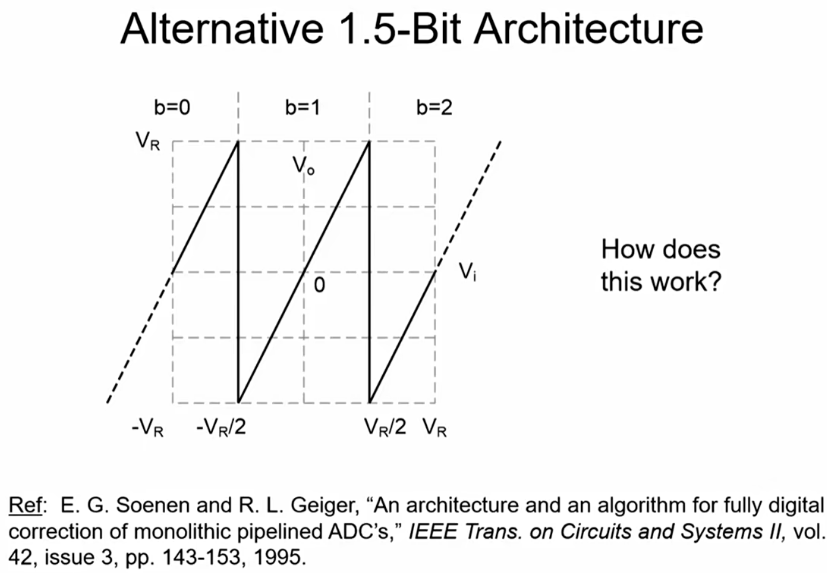

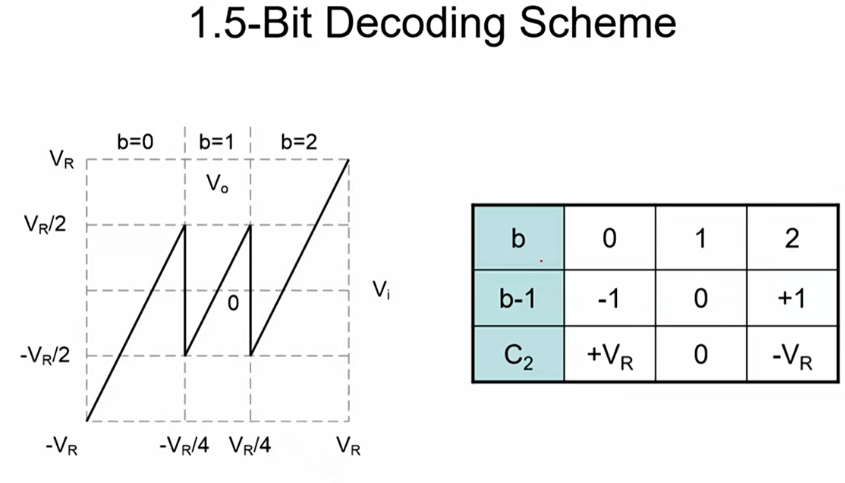

1.5bit 是因为:log_2(3)=1.58。然后数字信号处理是 错位相加。给出一个3bit的code

我们知道,error主要有:①CMP,②gain(cap,op-amp),③BW。通过加冗余比较器可以消除CMP_offset。cap_mismatch可以trim,op-amp可以gainboosting,2-stage,BW可以用功耗换。

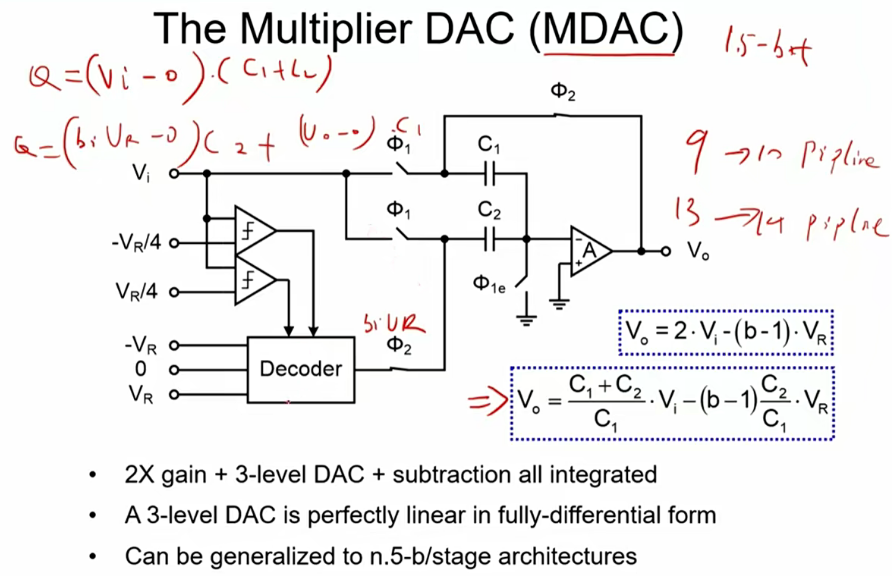

The Multiplier DAC (MDAC)

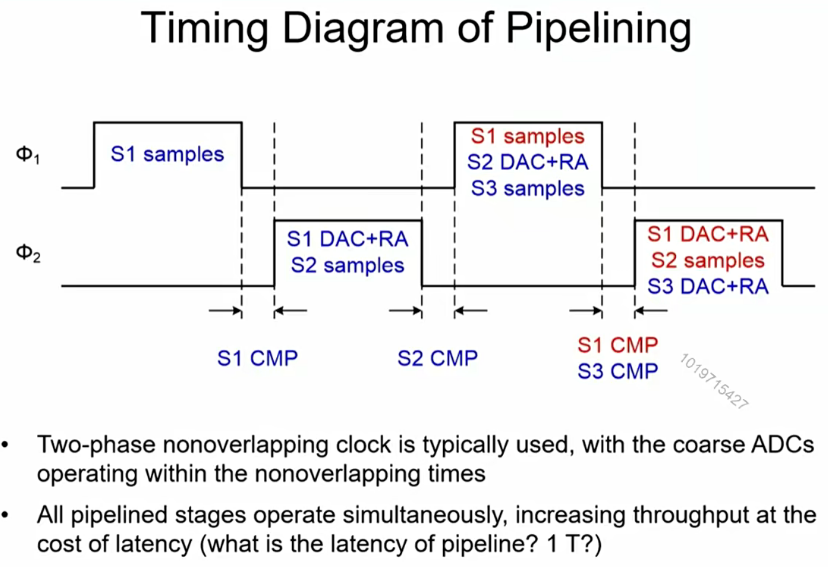

Pipline 就是多个MDAC串联。9个MDAC串联就是10-bit DAC。

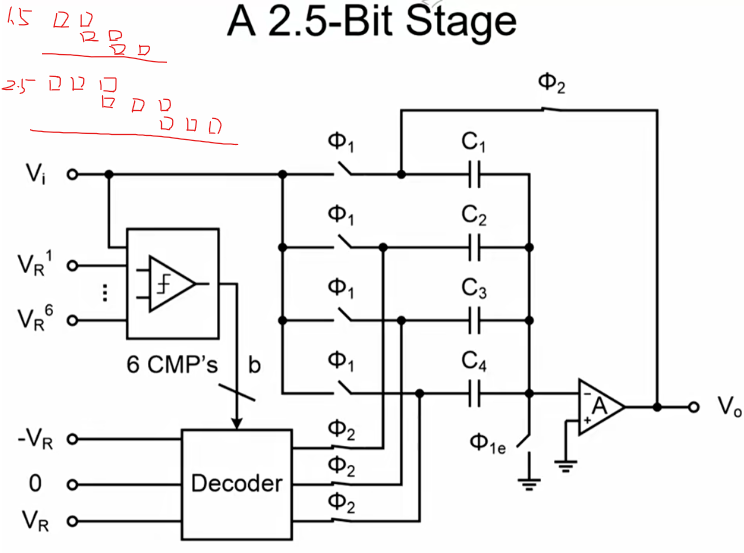

光看划线部分,是一个开关电容电路。工作过程如下:

φ1=1:C1&C2一端接Vi,另一端接ac_gnd。Q1=(Vi - 0)(C1+C2)。

φ1e先断开,然后φ1断开。φ1e断开瞬间,注入的是共模信号相关的,和是一个和Vin无关的误差,我们称其为低极板采样。

φ2=1:电荷重分配。(decoder输出是 bi*Vr) Q2=(bi*Vr - 0)C2 +(Vo - 0)C1

电荷守恒:Q1=Q2。(Vi - 0)(C1+C2) = (bi*Vr - 0)C2 +(Vo - 0)C1 然后令C1=C2。

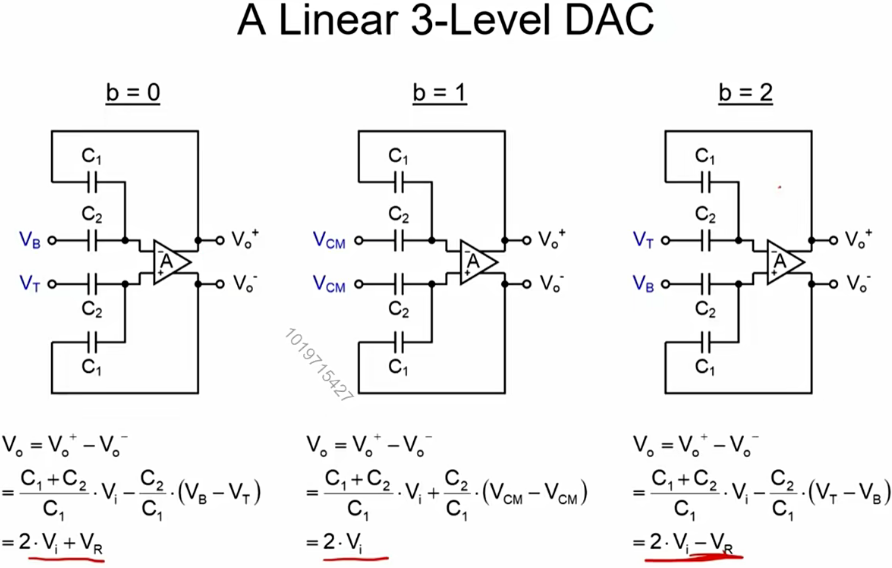

三个level,理论上来说需要一个2-bit-DAC,使用全差分,将三个level设置成 Vr,0,-Vr。就可以回归到 1-bit-DAC。(1-bit-DAC没有非线性问题)

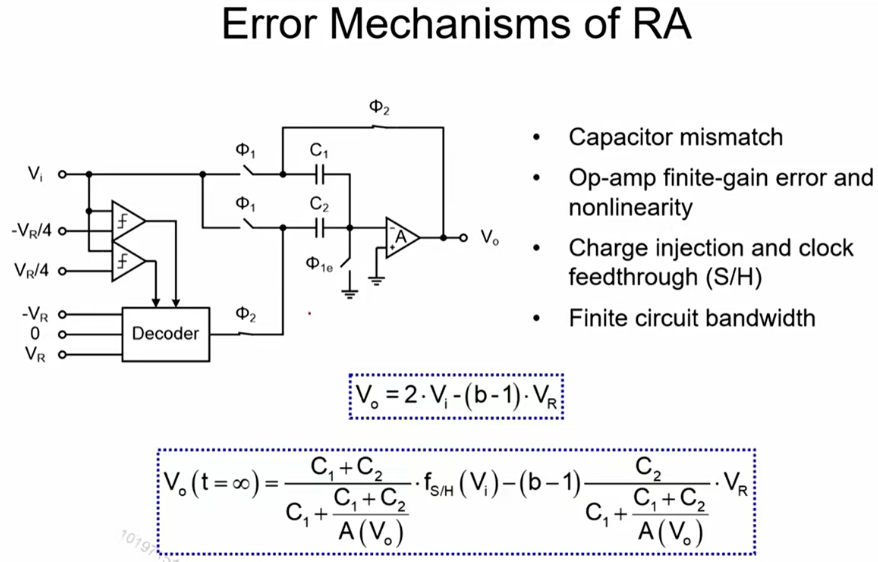

error主要有:①Cap mismatch——可以trim;②op-amp-gain——各种结构,gainboosting,2-stage;③S/H——低极板+全差分;④BW——用功耗换。

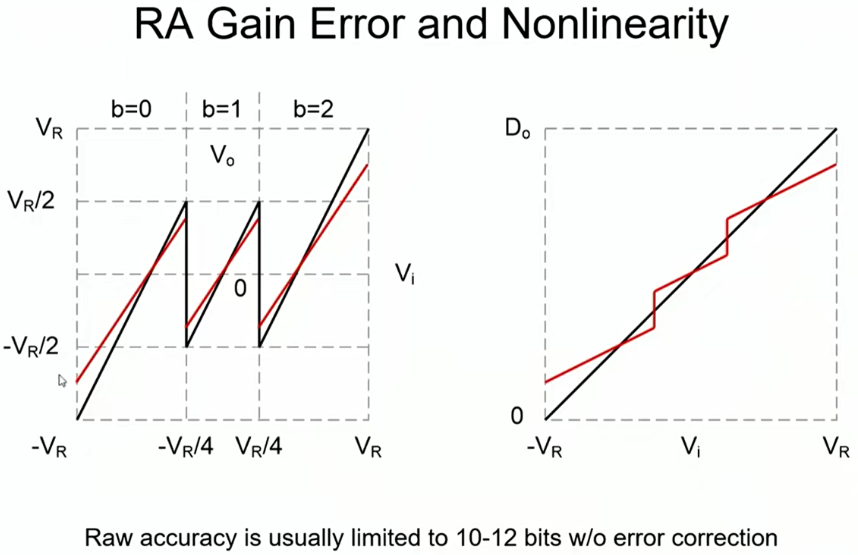

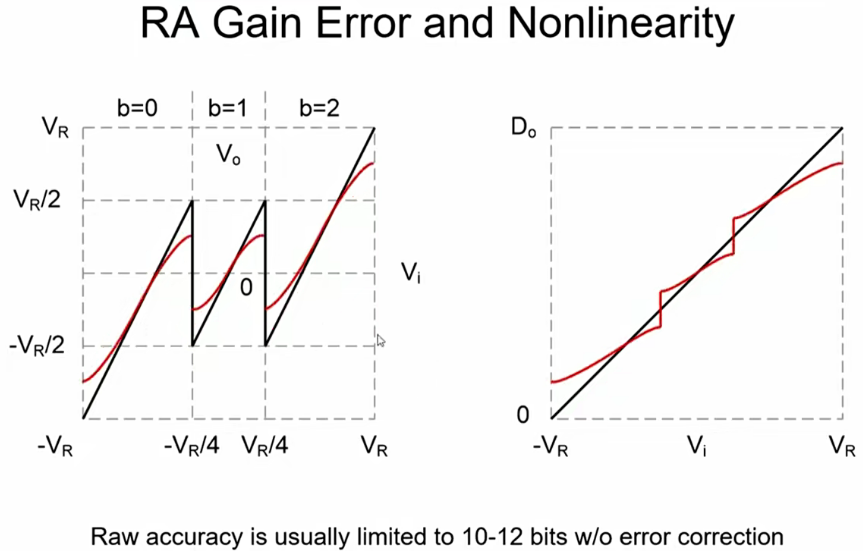

左下Gain error的影响,主要是cap_mismatch。右下是有限BW的影响,

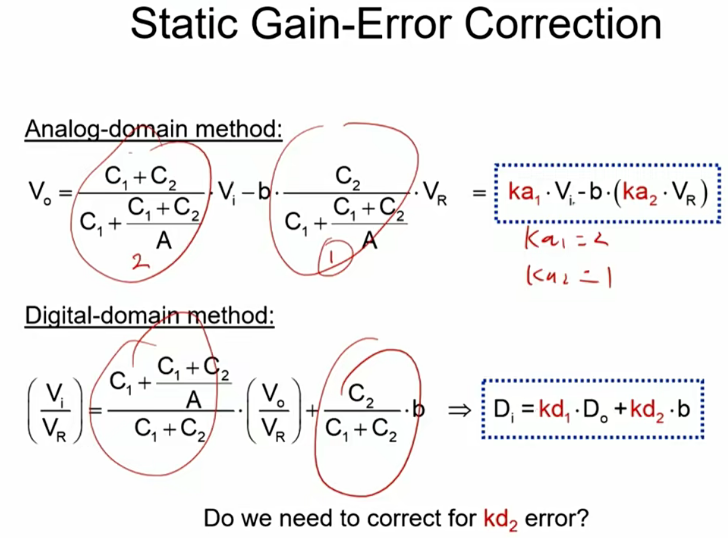

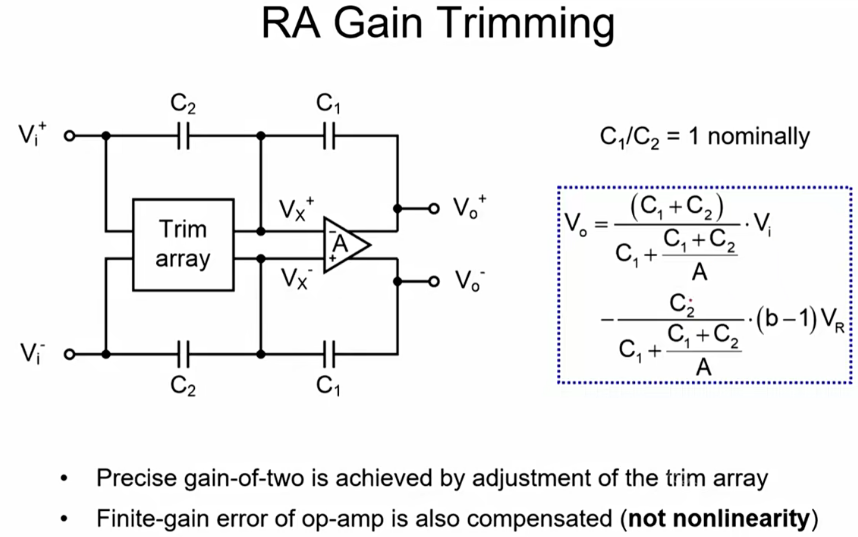

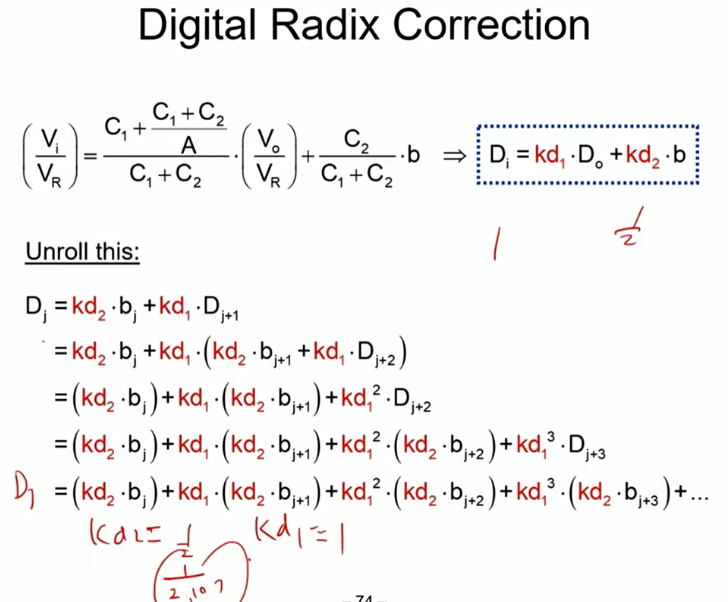

Gain-error 校准,模拟域trimC1&C2使得Ka1=2 & Ka2=1,数字域要知道确切的Kd1&Kd2

Analog-Trim:将Ka1和Ka2校准到我们需要的认为的理想值

Digital:表达式本身没错,不需要将Kd1和Kd2校准到理想值,我们只要知道实际值带入公式。

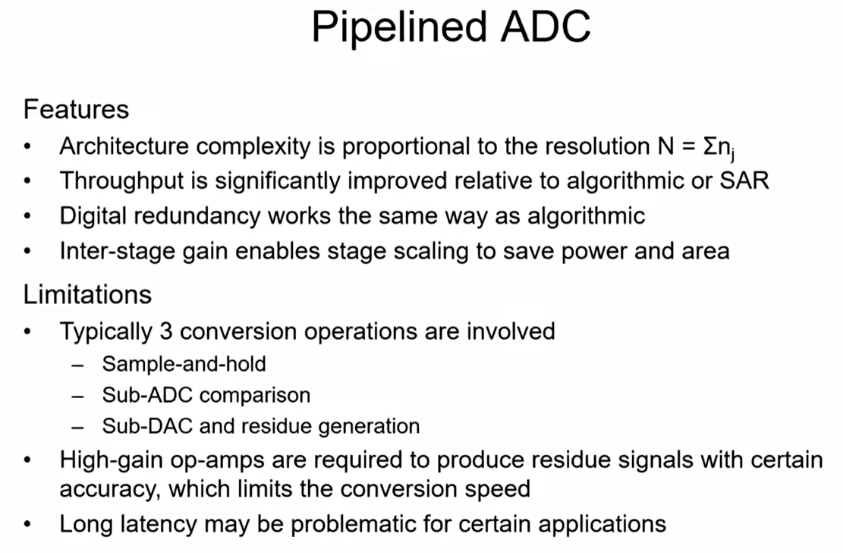

Pipline ADC 流水线ADC

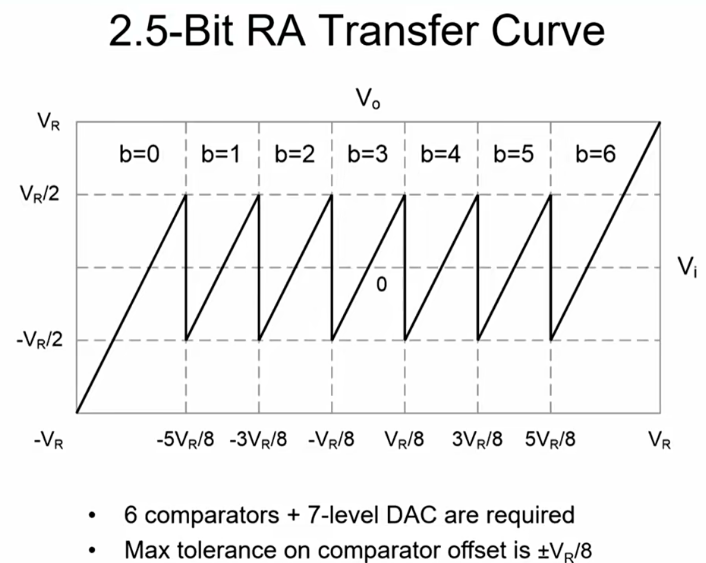

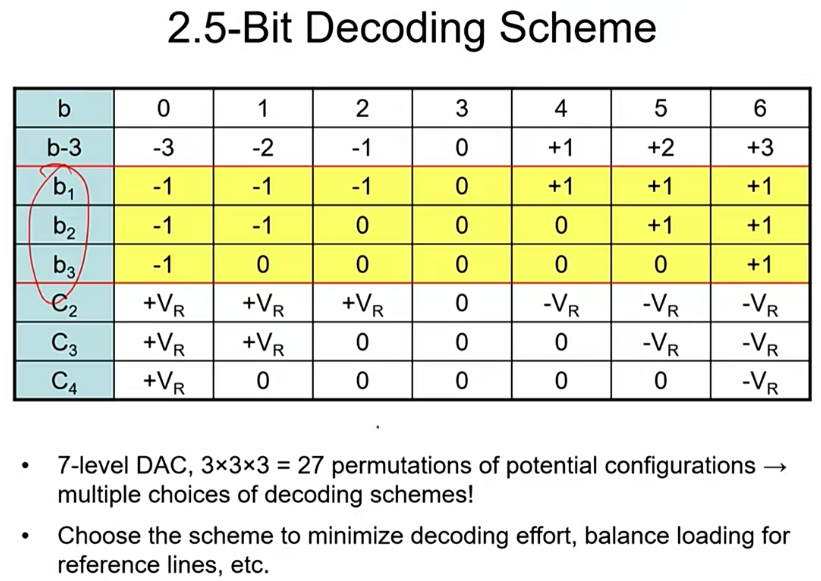

如果是1.5bit的话,N位需要N-1个MDAC,每个MDAC里面是有运放的,功耗大,所以有了2.5bit。

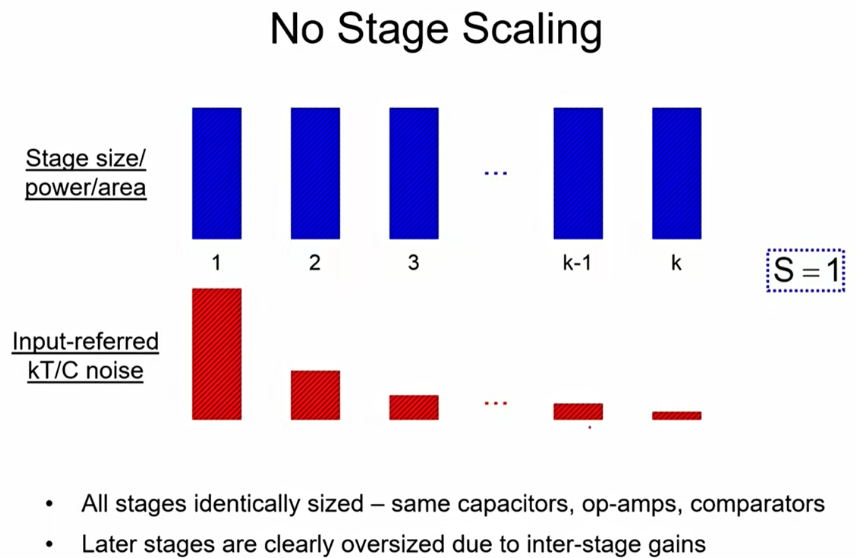

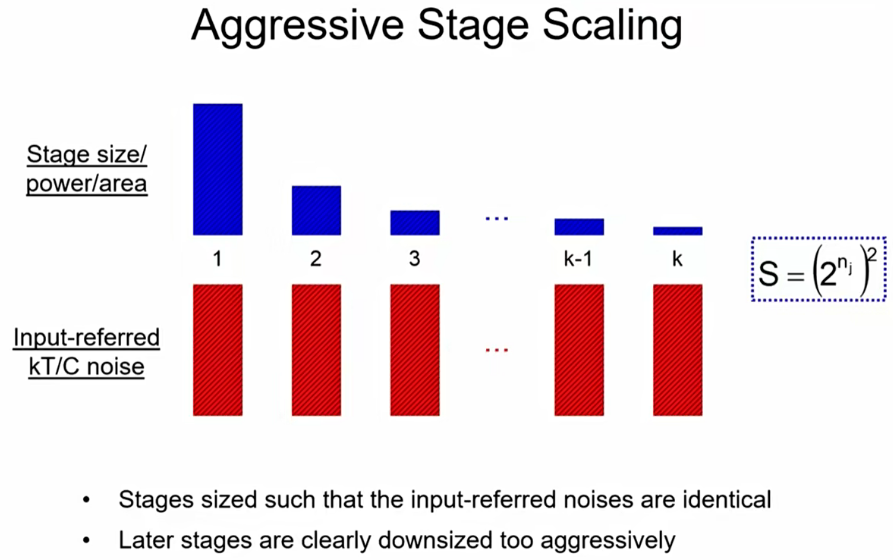

优点是:省面积,省功耗,速度更快。

缺点是:比较器更过了,电容更多了,mismatch风险更大。

着重优化MSB和MSB-1,第一级和第二级。

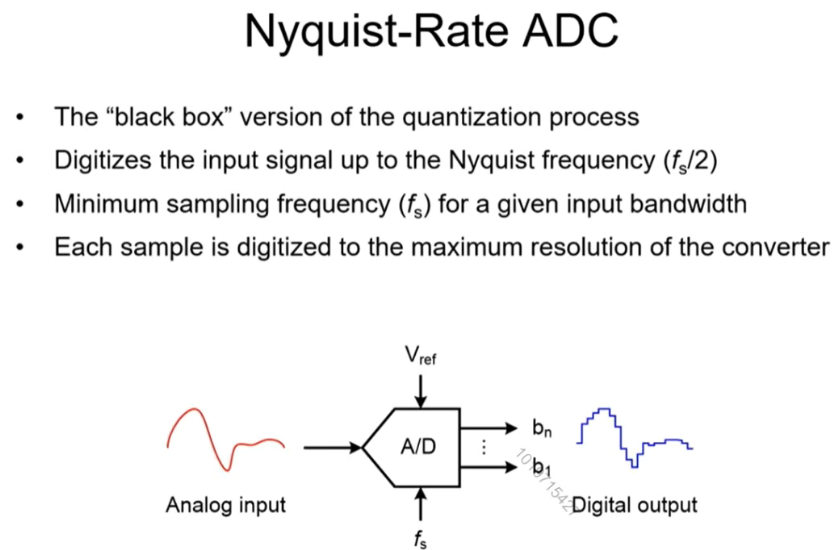

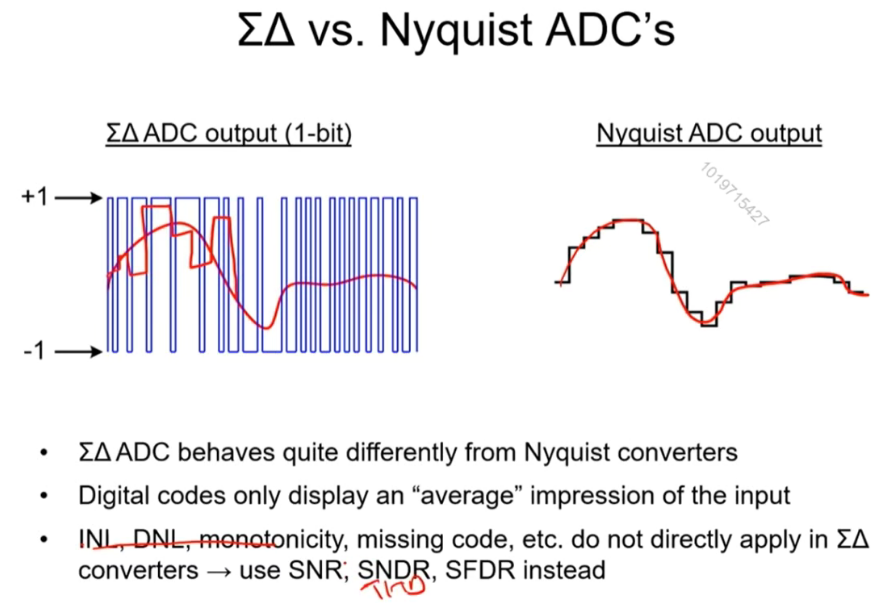

Oversampling ADC

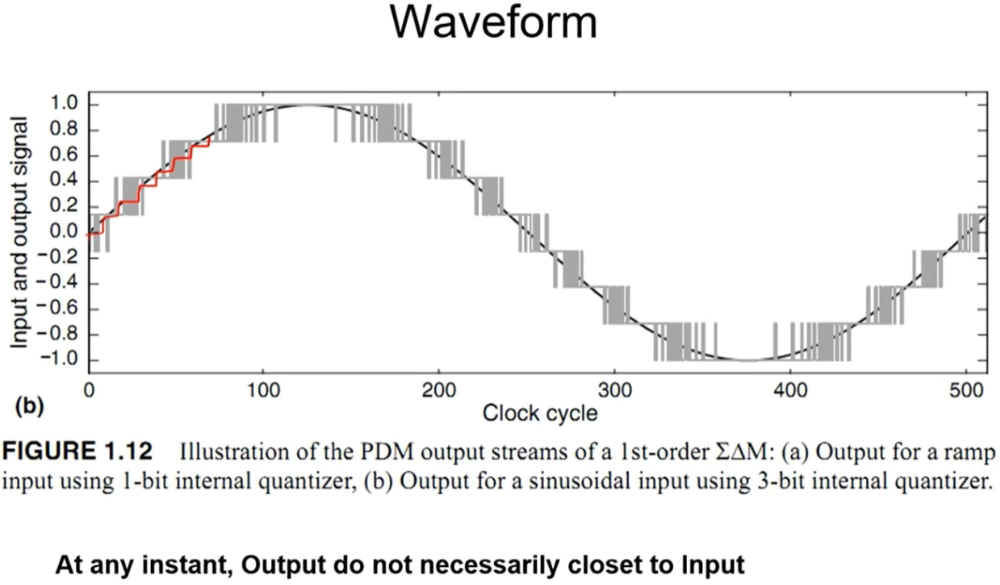

Review:Nyquist ADC,SD ADC区别: 一个是奈奎斯特频率,一个是sd 的静态指标基本不考虑的,只能给出输入信号波形的动态性能。sd ADC是延迟输出的,想要知道当前时刻输入信号的具体值需要一段时间之后才能获得,因此,实时的输入信号和输出信号差别较大,因为不是实时对应的。

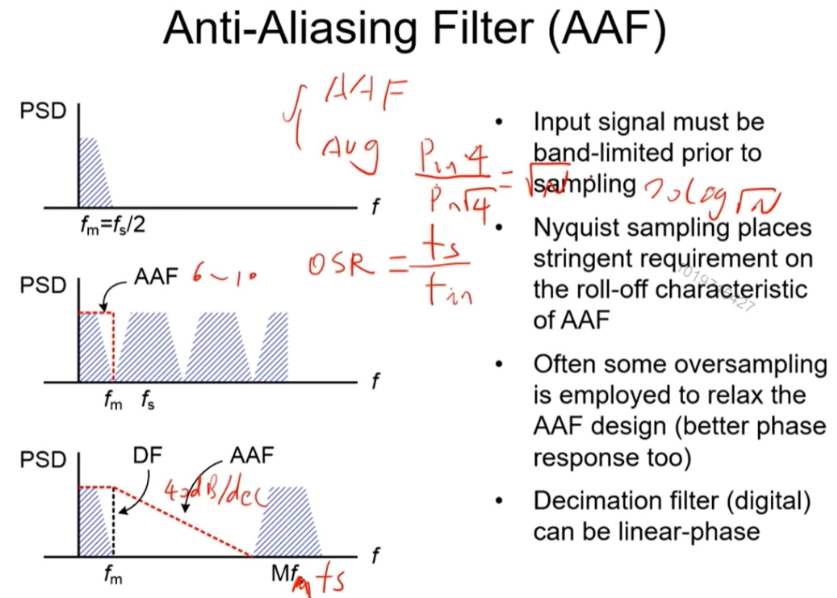

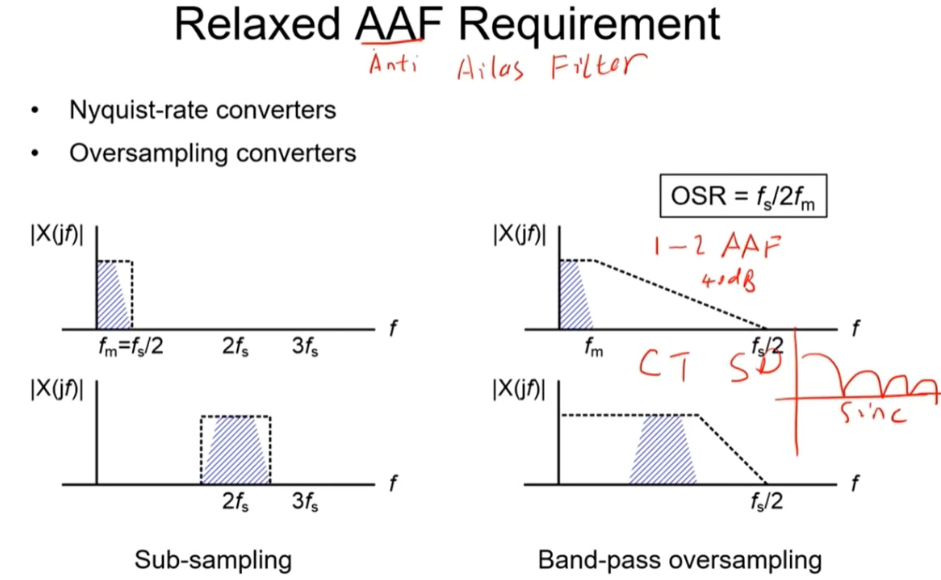

改善性能:①抗混叠滤波,做一个陡峭的高阶滤波器很困难,因此当输入信号频率和采样频率相差很大的时候,可以做一个不那么陡峭的滤波器(前文讲了,还要再做数字滤波)。②多次测量取平均,SNR来说,多次测量信号能量线性叠加,噪声能量开平方叠加,总的SNR就会改善。

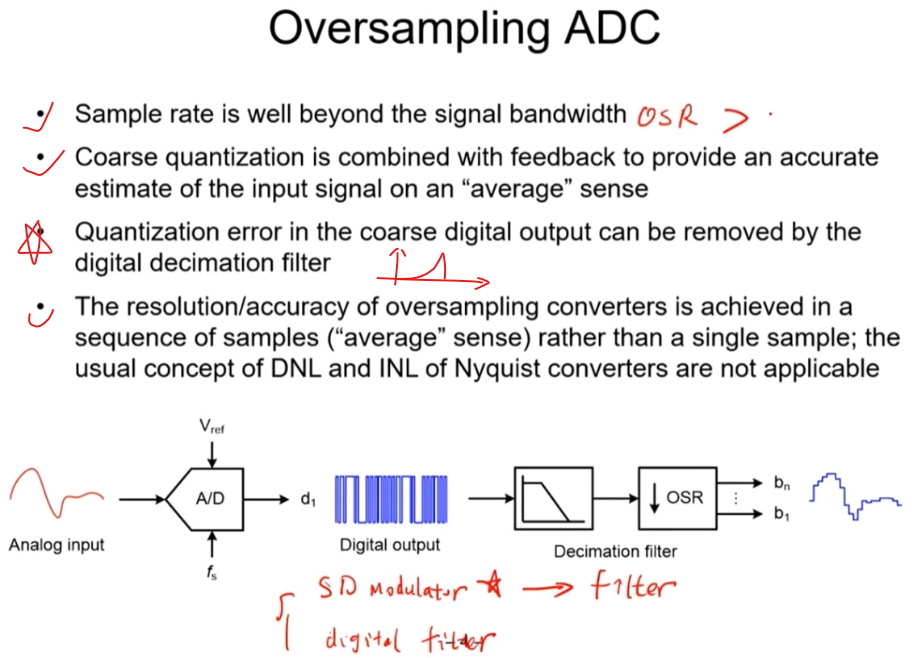

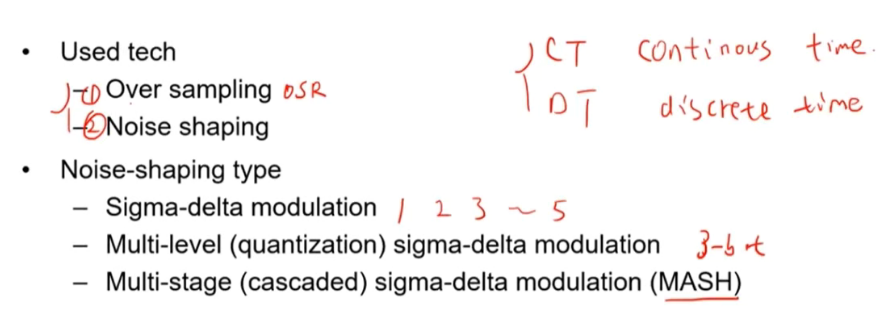

SD ADC主要应用:过采样+噪声整形。(这两个是独立的)

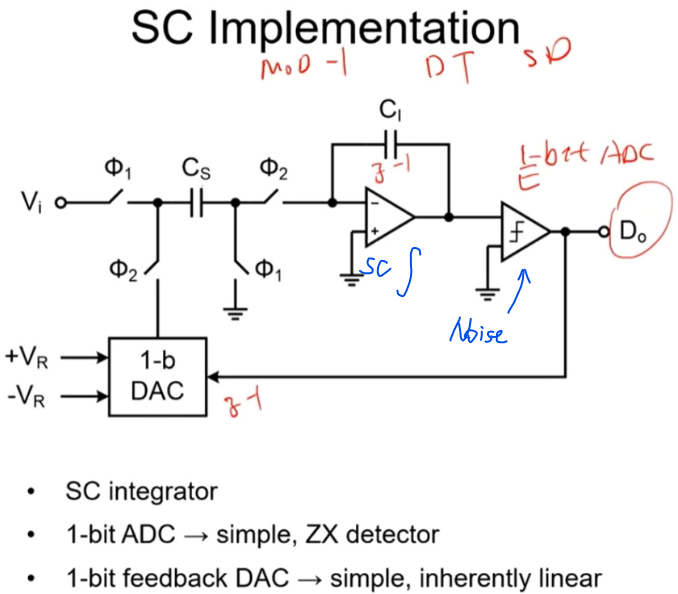

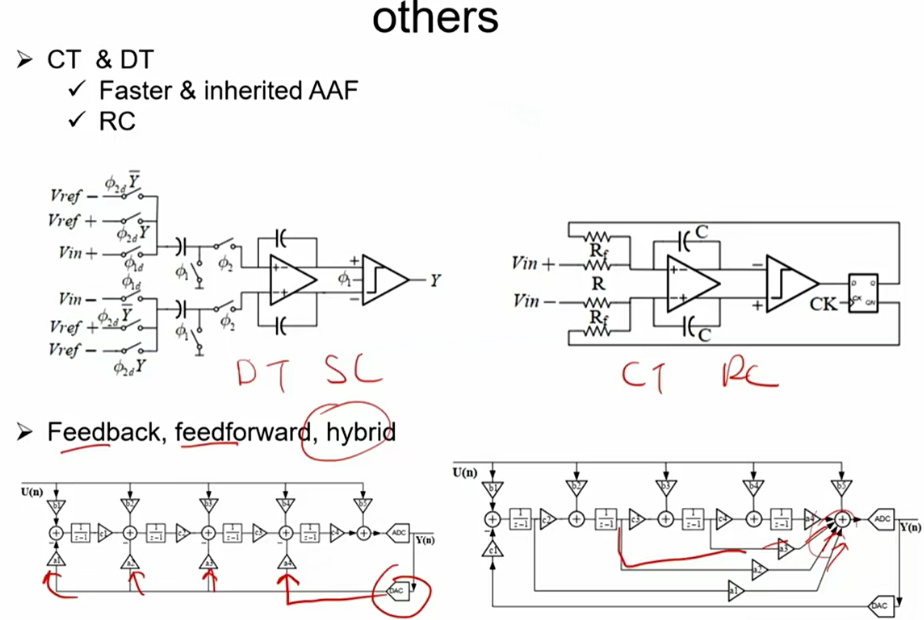

分为:CT——主要用RC滤波;DT——主要用SC(开关电容)滤波。

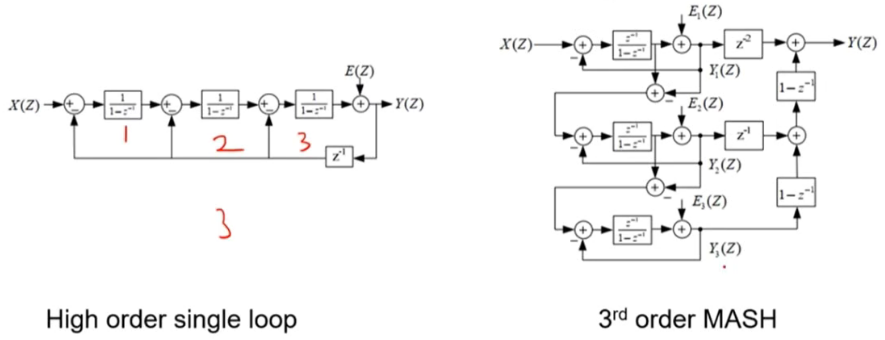

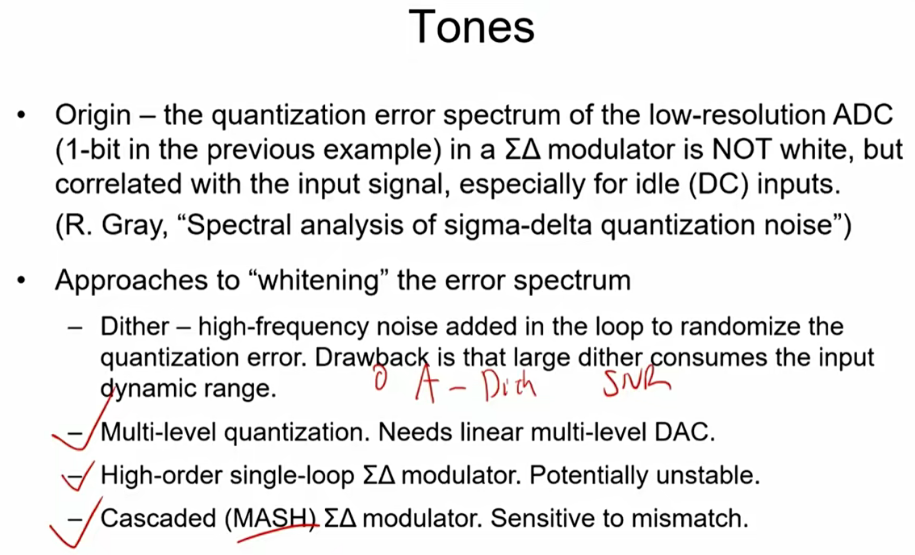

噪声整形分类:sd modulation阶数(稳定性问题);多比特;级联(mismatch问题)。排列组合。

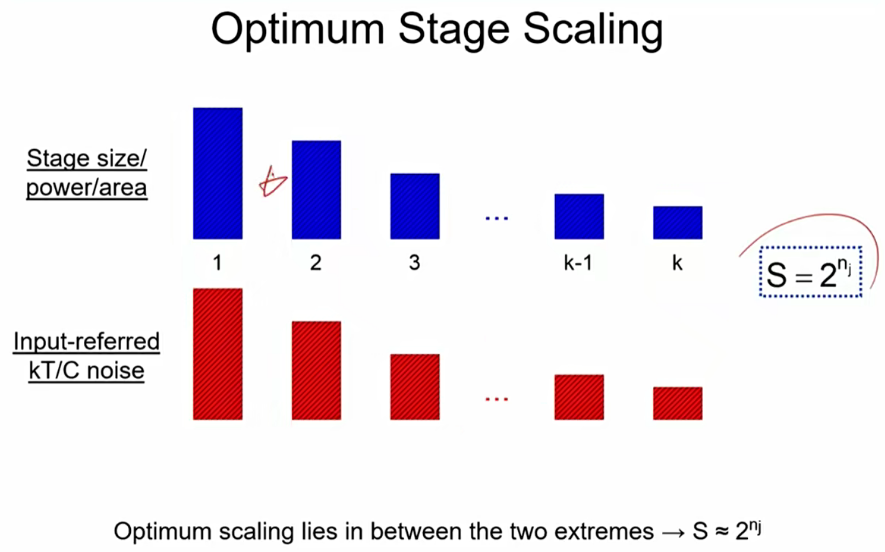

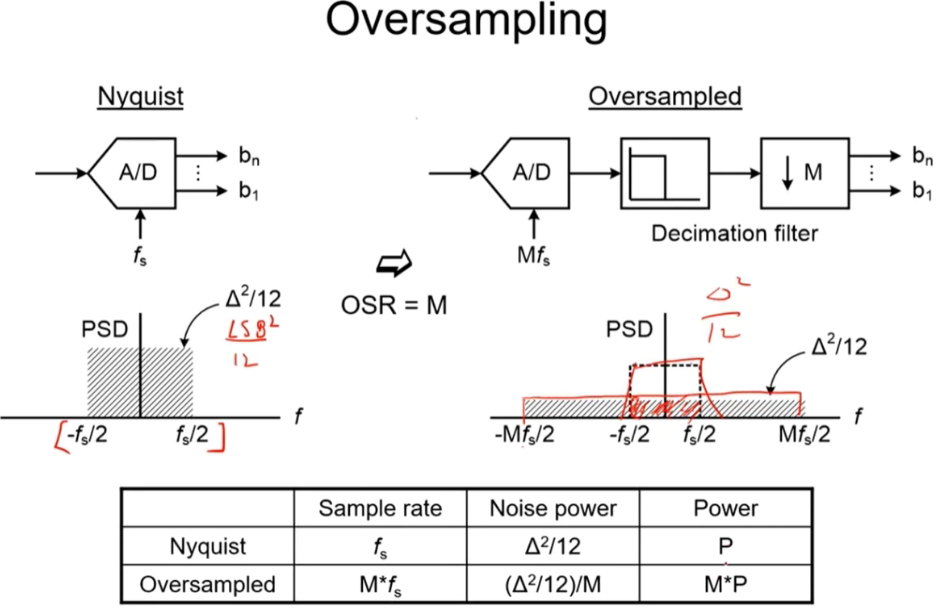

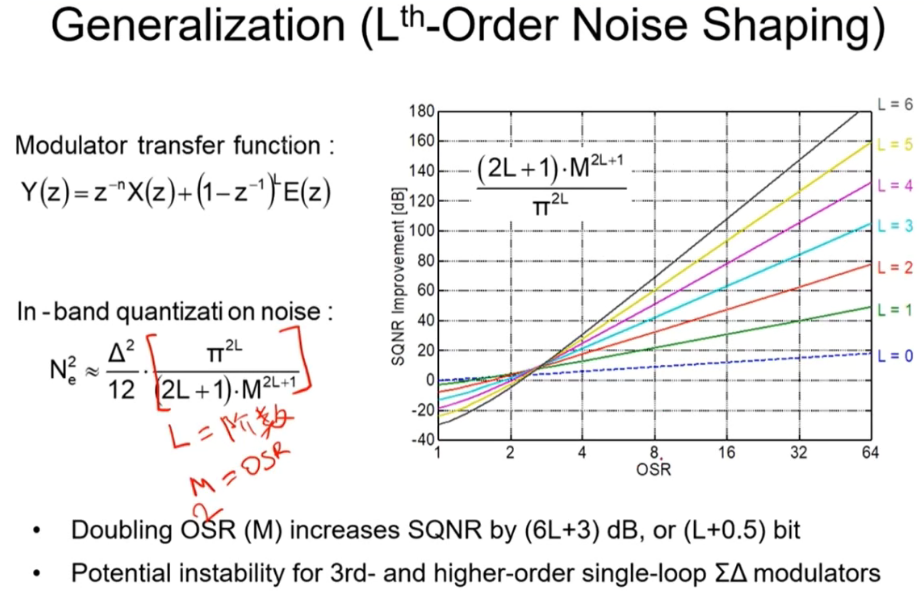

Oversampling 过采样:

过采样改善信噪比,代价是功耗增大了,本来的采样频率是fs,过采样后是M*fs,对放大器&比较器等带宽提出了更高的要求。同时还需要做 数字滤波器。

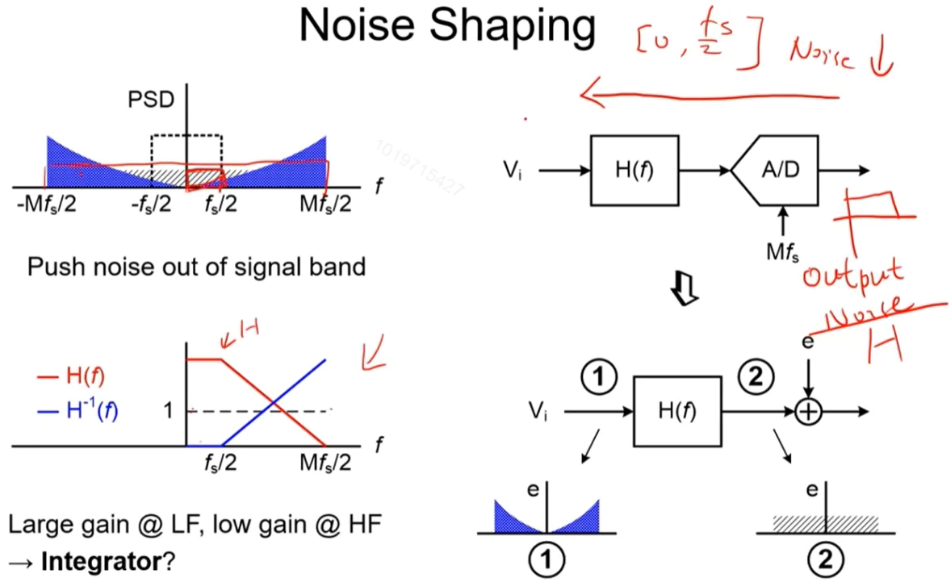

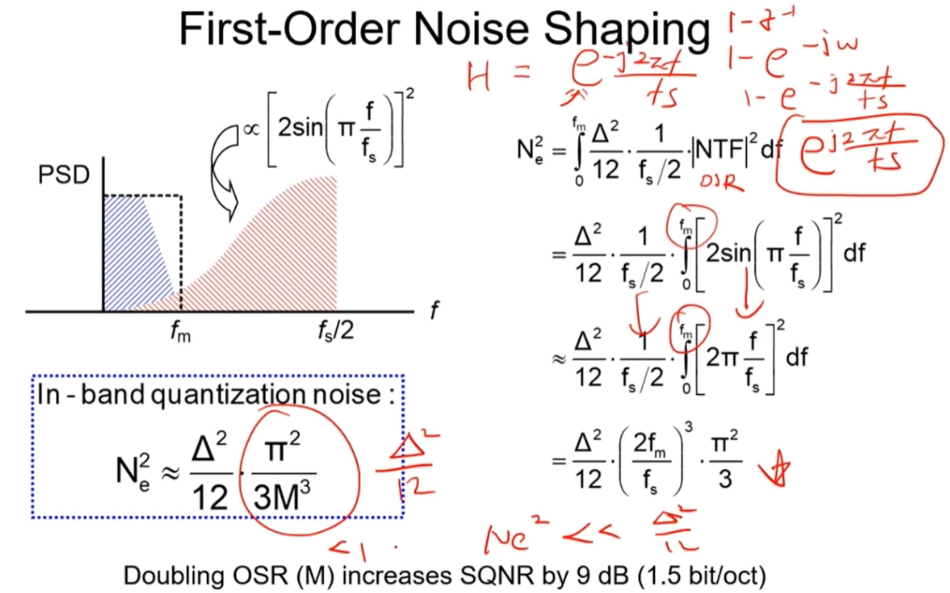

Noise Shaping:噪声整形

输出端的量化噪声是均匀的白噪声,对于H这种传递函数,output_noise 折回到 input_noise 后,Noise / H(f) ,这样等效到输入后低频噪声就被衰减了,noise shaping,相当于把低频处的噪声能量搬移到高频出,总的噪声能量不变。

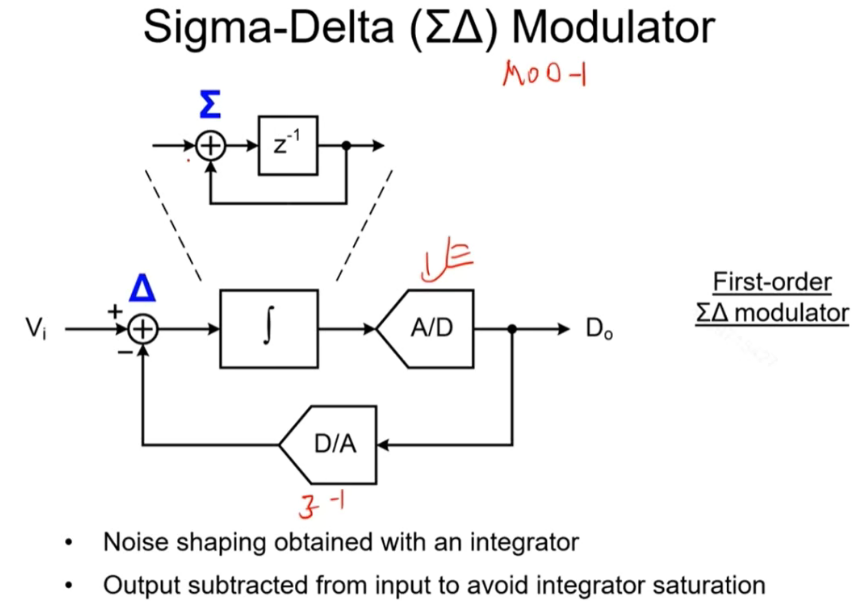

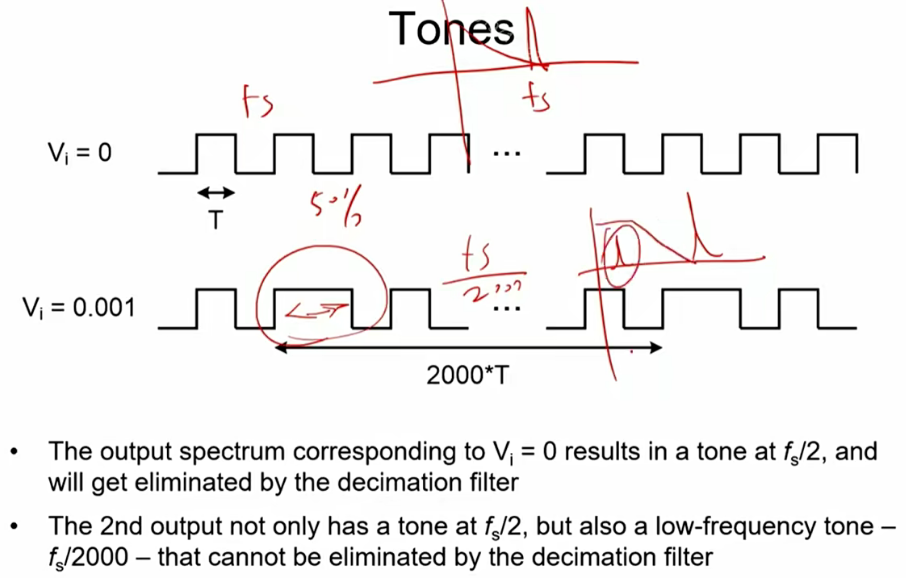

SD modulator

时域:类似PWM调制,信号幅值越高,输出高电平的时间越长。因此输出高电平的概率和输入信号相关。数字降采样滤波器:将高电平出现的概率,进行一个模拟和数字的转换(即用一个N-bit-Codes表征高电平出现的概率)。

频率:噪声整形。

反馈系统:Delta-差分,Sigma-积分。只要环路增益足够大,输入信号就可以近乎无损的传到输出,噪声会被抑制环路(1+H)倍。

Sigma-Delta ADC Modulator

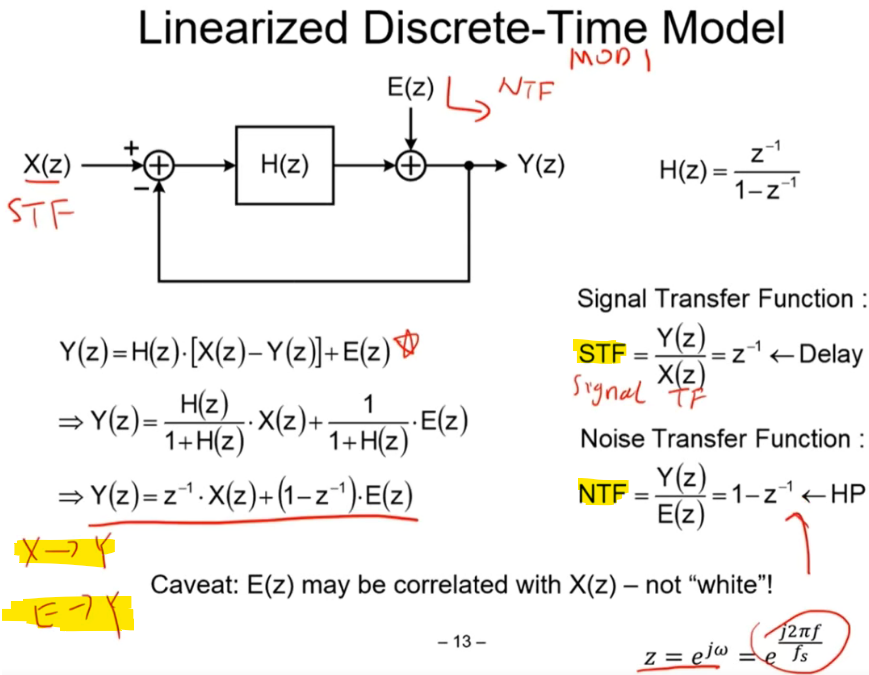

为什么说1-z^(-1)是高通滤波器呢?![]()

过采样率增加一倍,SNR增加9dB。

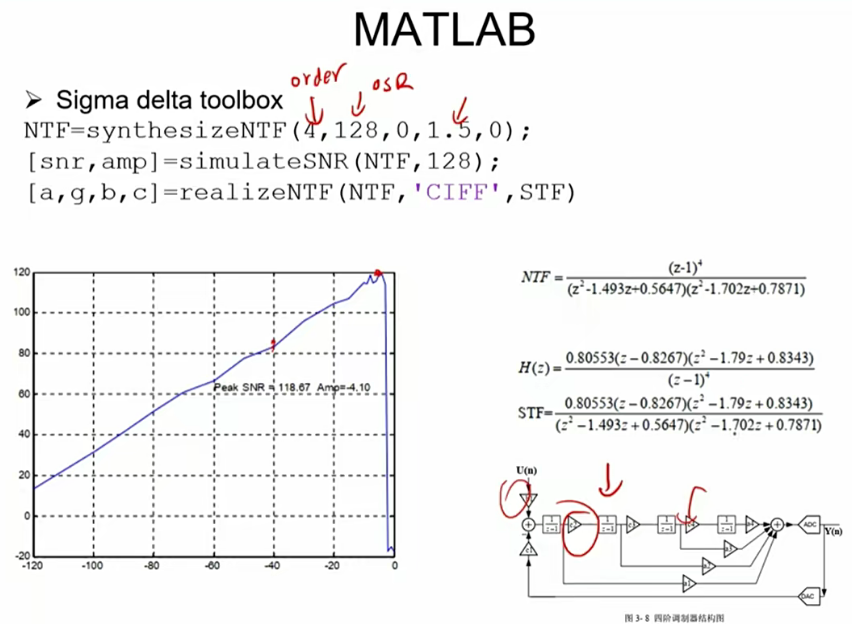

电路实现:

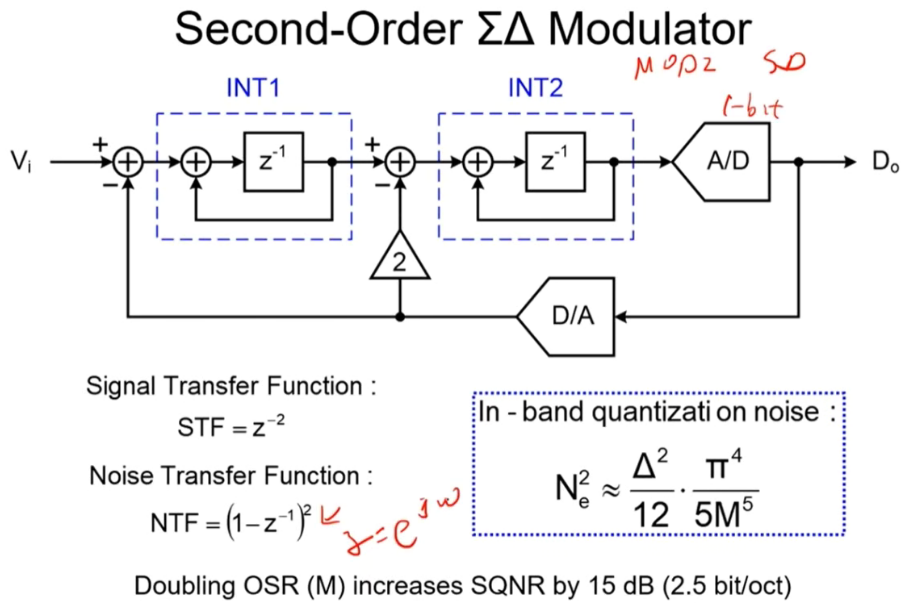

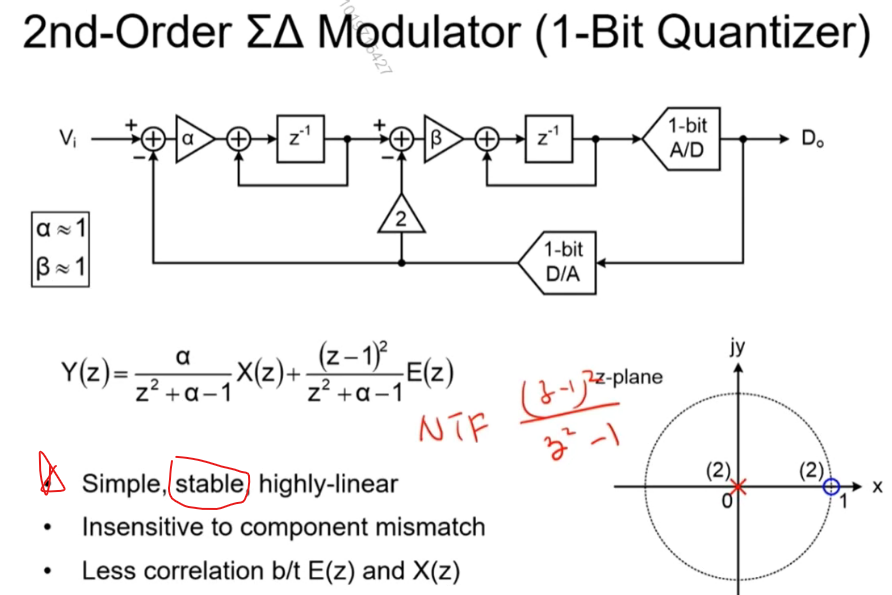

二阶Sigma-Delta Modulator

S-D ADC的缺点:

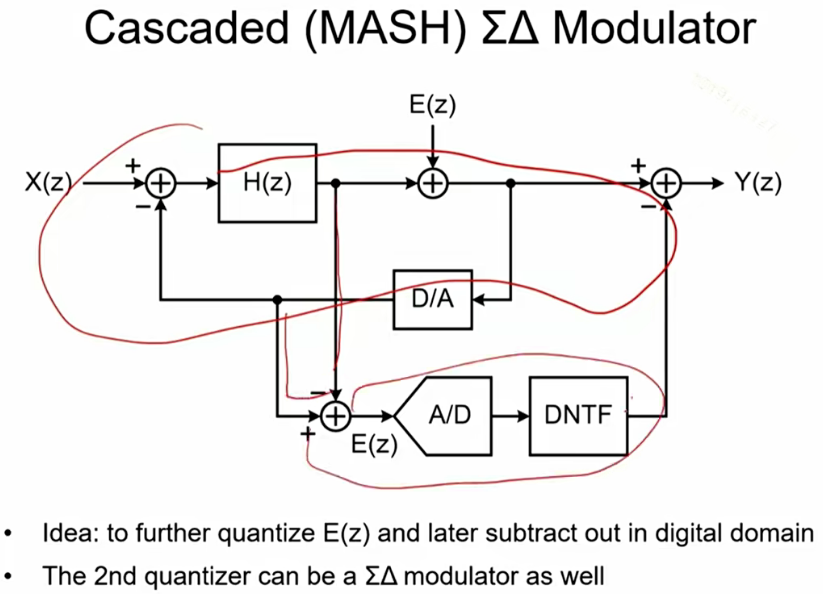

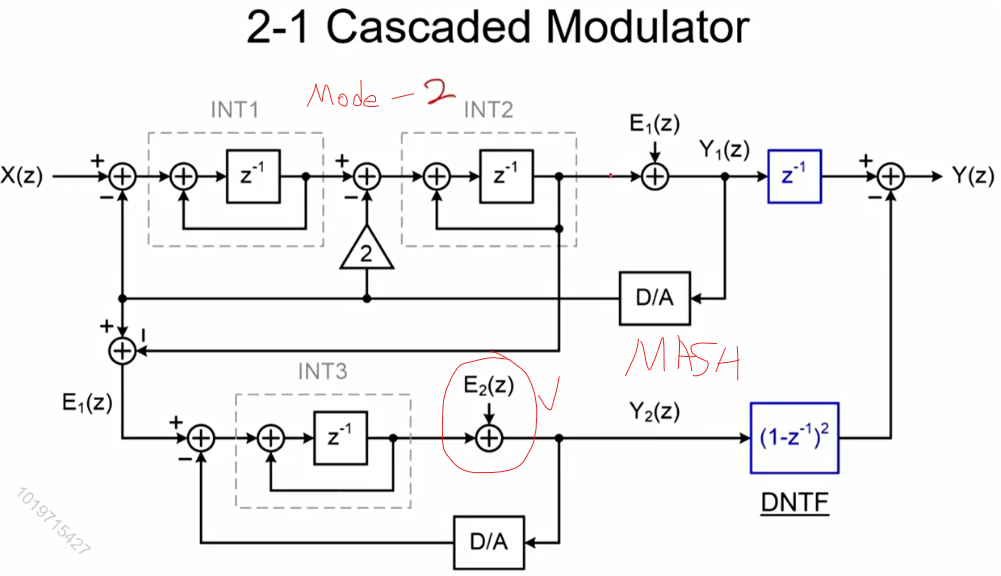

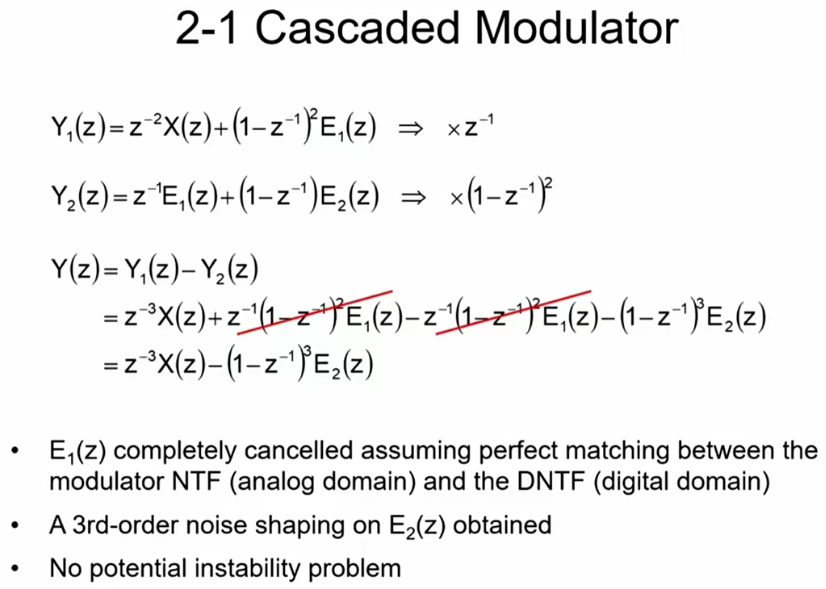

Cascode (MASH)S=D Modulator

对噪声再做一次积分量化。

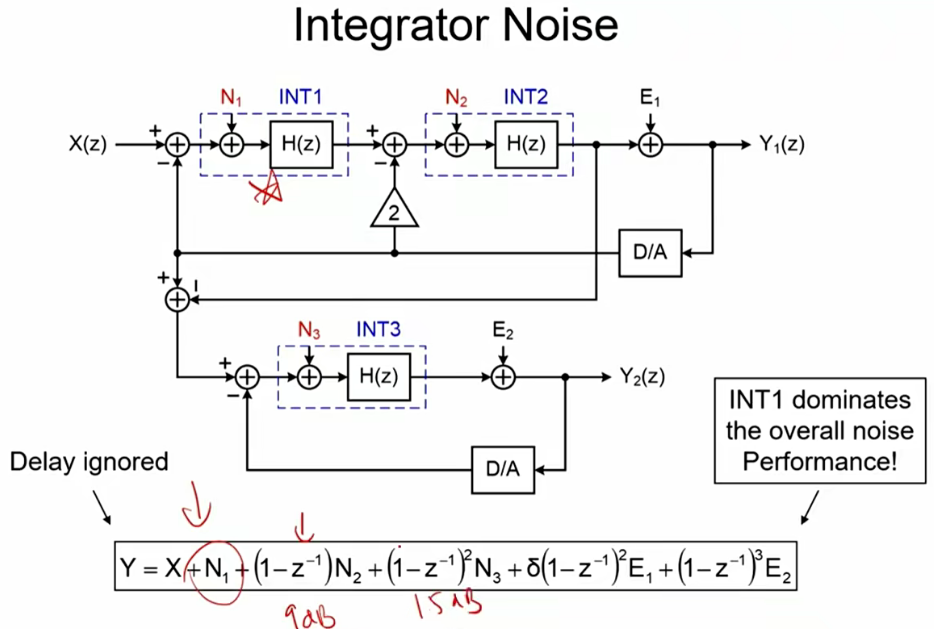

积分器的噪声:

其他:

308

308

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?