FPGA 10G UDP工程源码

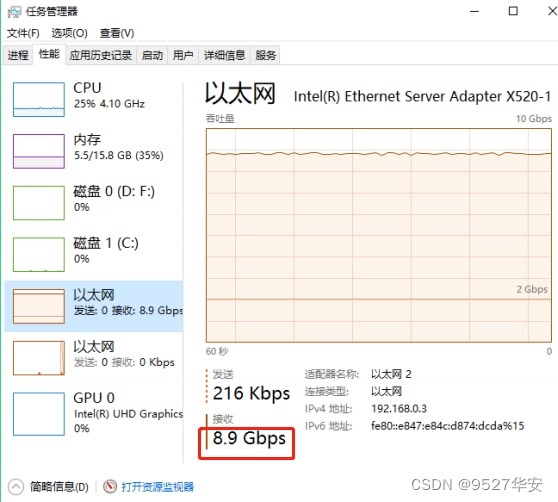

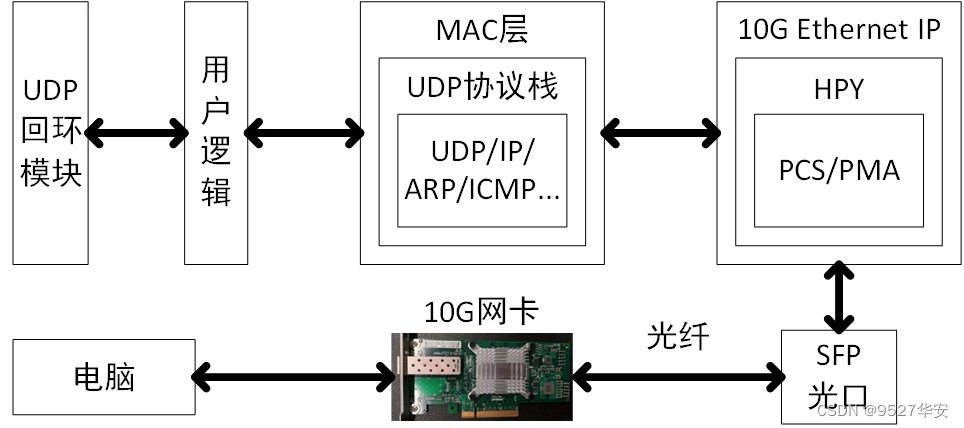

可实现动态ARP,ping,udp数据收发,速率10G,没有用到10G phy,而是用Xilinx的FPGA纯逻辑资源搭建实现。

ID:49300715102539418

FPGA小白

FPGA 10G UDP工程源码是一种基于FPGA的网络传输方案,它在实现动态ARP、ping、以及UDP数据的收发上具备了出色的性能。这个方案能够在10Gbps的数据传输速率下运行,并且独特之处在于它并未使用10G物理层接口,而是纯粹利用Xilinx FPGA的逻辑资源来构建和实现。

FPGA(Field-Programmable Gate Array)作为一种可编程的硬件,具备了高度的灵活性和可定制性,适用于各种应用场景。而在网络传输方面,FPGA能够发挥其强大的并行处理能力,以及低延迟、高吞吐量的特性,使得其成为实现高速数据传输的理想选择。

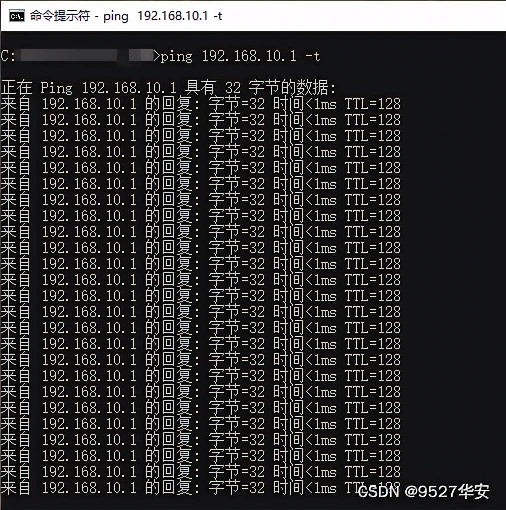

在这个工程源码中,动态ARP(Address Resolution Protocol)是其中一个重要的功能。ARP是一种用于将IP地址映射到MAC地址的协议,它在局域网中起到了非常关键的作用。而动态ARP则允许网络设备在通信过程中动态地将IP地址与MAC地址进行绑定,从而提高整体的网络通信效率。通过合理的设计和优化,这个工程源码能够实现快速而准确的动态ARP功能,从而为网络通信提供了可靠的基础支持。

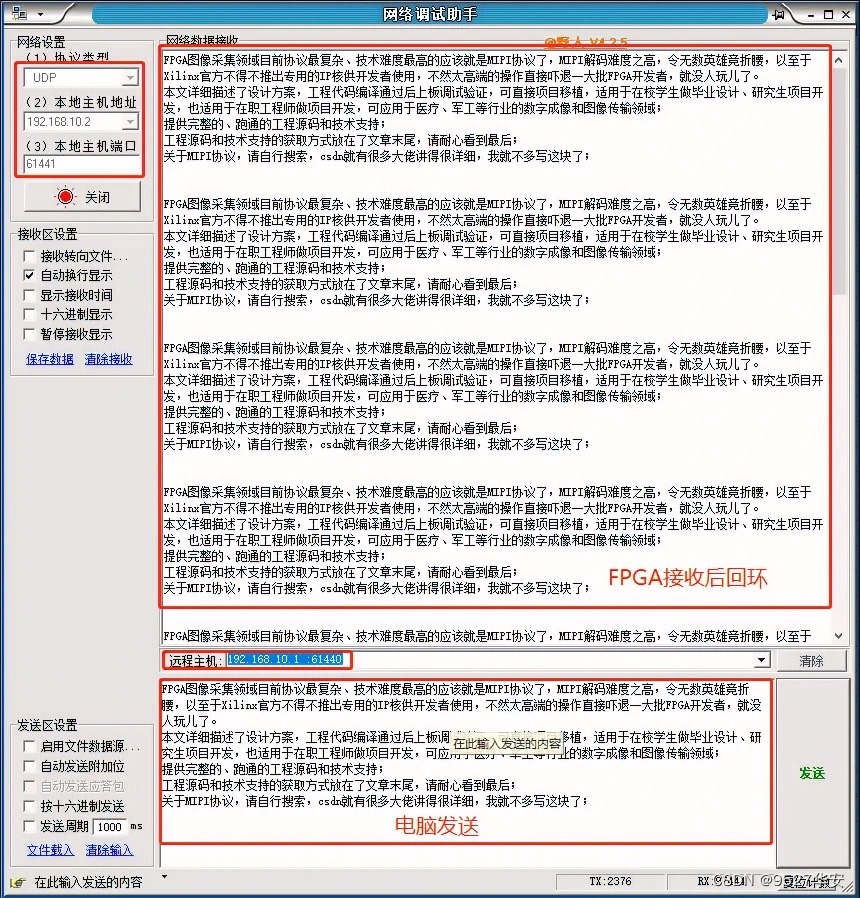

此外,ping是网络中常用的一种命令和工具,用于测试两台设备之间的连通性。这个工程源码中实现了对ping命令的支持,能够准确地判断网络设备之间是否可达,并给出相应的回应。通过对ping命令的处理,可以及时地检测和排除网络中的故障,保证网络的可靠性和稳定性。

在数据传输方面,UDP(User Datagram Protocol)是一种面向无连接的传输协议,其特点是传输速度快,但不保证数据的可靠性和顺序性。这个工程源码实现了对UDP数据的接收和发送功能,能够在10Gbps的速率下高效地完成数据的传输。通过对FPGA逻辑资源的充分利用,这个工程源码实现了高速而稳定的UDP数据通信,为网络应用提供了强有力的支持。

需要注意的是,这个工程源码并未使用10G物理层接口来实现10Gbps的数据传输速率,而是完全依靠FPGA的逻辑资源进行构建。这样的设计使得整个方案更加灵活和可扩展,能够适应不同的硬件平台和应用需求。同时,它也突显了FPGA作为一种可定制的硬件的独特优势,为网络传输的发展带来了新的可能性。

综上所述,FPGA 10G UDP工程源码是一种利用FPGA逻辑资源实现高速网络传输的方案。它通过动态ARP、ping、和UDP数据收发功能,为网络通信提供了高效、稳定的支持。其独特的设计和实现方式,使得这个方案具备了出色的灵活性和可定制性,为未来网络传输的发展带来了新的机遇。随着FPGA技术的不断进步和网络应用的不断发展,相信这样的方案将在实际应用中发挥出更加重要的作用。

【相关代码,程序地址】:http://fansik.cn/715102539418.html

673

673

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?