硬件:Zedboard

软件:Vivado2018.2 + Win10

本文参考了http://blog.chinaaet.com/cuter521/p/35946,原文代码有错误,已更正。

1 设计

功能:PL流水灯

语言:verilog

流程:建立工程->代码编辑->功能仿真->综合、实现->生成Bitstream->烧写进板子,观察现象

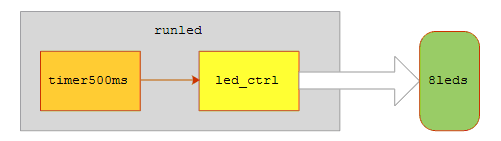

功能图:

timer500ms模块:

产生2hz的时钟,为led_ctrl模块提供时钟。

led_ctrl模块:

实现循环移位,在硬件上的体现就是流水灯。输入时钟为2hz,时钟上升沿进行一次移位操作,每个led点亮0.5s。

2 代码

runled_top.v

`timescale 1ns / 1ps

module runled_top(

input iClk,

input iRst_n,

output [7:0] oLed

);

wire clk2hz_sig;

timer500ms timer500ms_inst(

.iClk100mhz(iClk),

.iRst_n(~iRst_n),

.oClk2hz(clk2hz_sig)

);

led_ctrl led_ctrl_inst(

.iClk(clk2hz_sig),

.iRst_n(~iRst_n),

.oLed(oLed)

);

endmodule

timer500ms.v

`timescale 1ns / 1ps

/*

oFreq = iFreq/(2*N)

N = iFreq/(2*oFreq) = 100,000,000/(2*2) = 25,000,000 = 0x17d7840

*/

module timer500ms(

input iClk100mhz,

input iRst_n,

output reg oClk2hz // period = 1/2s

);

reg [31:0] cnt2hz;

always @(posedge iClk100mhz)

begin

if(iRst_n==1'b0)

begin

oClk2hz <= 1'b0;

cnt2hz <= 32'b0;

end

else

begin

if(cnt2hz==32'd25000000)

begin

cnt2hz <= 32'b0;

oClk2hz <= ~oClk2hz;

end

else

begin

cnt2hz <= cnt2hz + 1'b1;

oClk2hz <= oClk2hz;

end

end

end

endmodule

led_ctrl.v

`timescale 1ns / 1ps

module led_ctrl(

input iClk,

input iRst_n,

output [7:0] oLed

);

reg [7:0] led;

always @(posedge iClk)

begin

if(iRst_n == 1'b0)

led <= 8'b1;

else

//实现循环左移

led <= {led[6:0], led[7]};

end

assig

使用Vivado2018.2在ZedBoard上实现PL流水灯功能,详细步骤包括创建工程、添加源文件、行为级仿真、综合、实现、生成Bitstream及烧写。通过verilog语言编写timer500ms和led_ctrl模块,仿真验证分频和流水灯逻辑的正确性。

使用Vivado2018.2在ZedBoard上实现PL流水灯功能,详细步骤包括创建工程、添加源文件、行为级仿真、综合、实现、生成Bitstream及烧写。通过verilog语言编写timer500ms和led_ctrl模块,仿真验证分频和流水灯逻辑的正确性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

258

258

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?