目录

5.6.5 cfg_1080p_30fps_336M_mipi

5.6.6 cfg_1080p_30fps_336M_1lane_mipi

1. 简介

1.1 要点

基于 KV260 + PCAM_5C 构建视频通路,通过 PYNQ 可视化图像,用以进一步处理图像数据,从 MIPI 至图像数据,包括如下要点:

- 在 PYNQ 下通过 IIC 配置 OV5640

- 配置 MIPI CSI-2 Rx subsystem 经验汇总

- AXI4-Stream 基础设施

- 配置 Sensor Demosaic 经验汇总

- 配置 AXI VDMA 经验汇总

- Sensor OV5640 时钟树

- 图像数据流波形抓取

1.2 背景

直接使用 KV260 Base Overlay 构建视频通路,初始化 OV5640 时,会陷入了循环或者无法初始化。如下是官方论坛的问题汇总:

1.2.1 Got stuck

I am trying to connect the Diligent PCam5C with my Kria KV260 board and use the supplied notebook mipi_to_displayport 4, but it seemed to get stuck in a loop at this point

“frame = mipi.readframe()”

1.2.2 Can't be Initialized

2. Overlay

2.1 参考 Overlay

2.1.1 KV260 Base

https://github.com/Xilinx/Kria-PYNQ/tree/main/kv260/basehttps://github.com/Xilinx/Kria-PYNQ/tree/main/kv260/base该 Overlay 支持 KV260 的 Raspberry Pi 摄像头和 PMOD 接口。可以将 Digilent Pcam 5C 摄像头连接到 KV260,并通过 Jupyter 笔记本进行控制。此外,PMOD 接口上支持多种 Grove 和 PMOD设备,所有这些设备都可以通过可编程逻辑中的 Xilinx Microblaze 处理器进行控制。

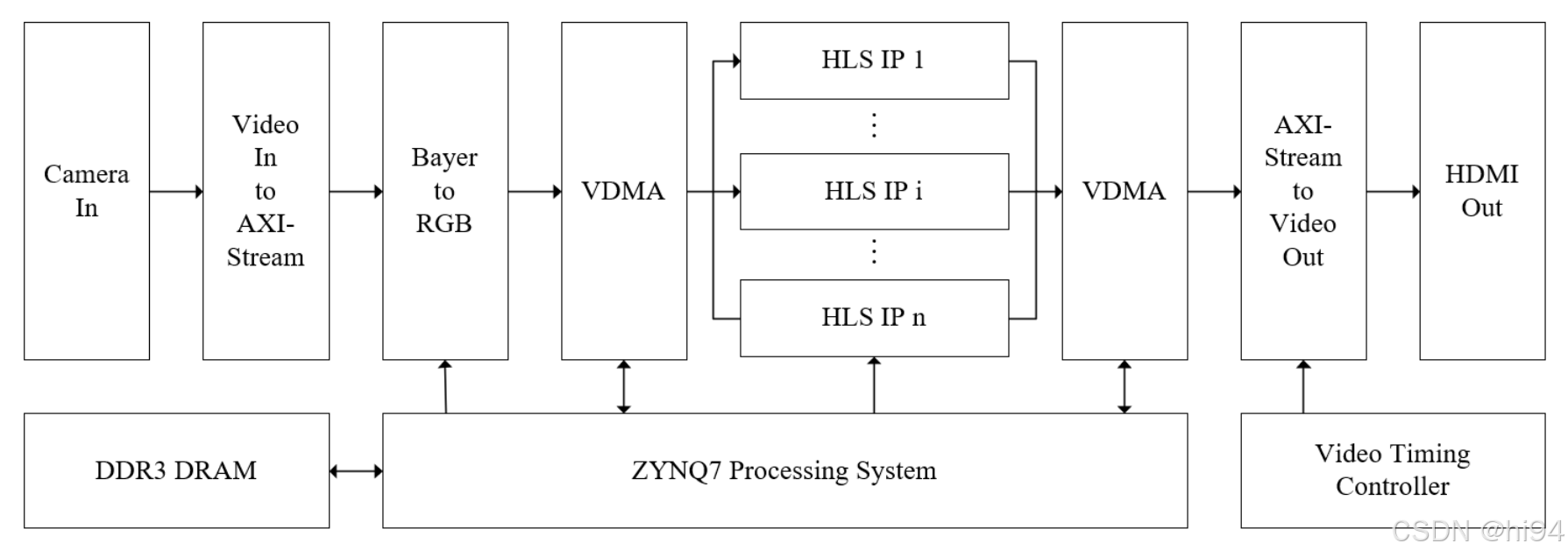

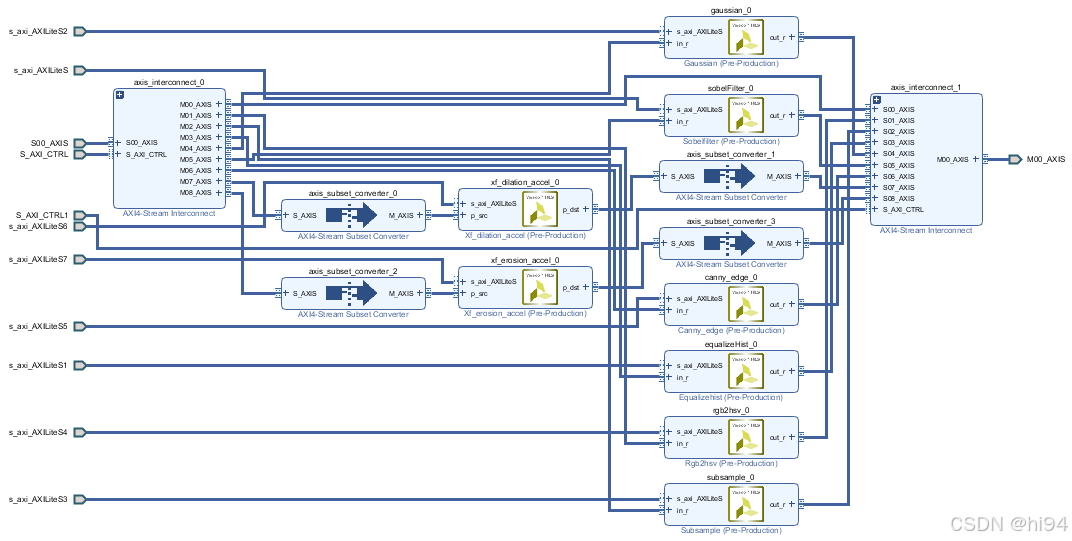

2.1.2 Pynq-CV-OV5640

在这个 Overlay 中,图像是从连接到 PL 侧的 OV5640 摄像头捕获的,并且该覆盖层包含了几种加速的图像处理算法,可以选择启用哪种算法,而无需下载新的比特流。在示例应用程序 Notebook 中,可以配置 OV5640 摄像头,获取捕获的图像并在笔记本上显示。处理后的视频流将显示在连接到 PL 侧的 HDMI 显示器上。

这个 Overlay 包含以下加速的图像处理算法:

- rgb2hsv(RGB 转 HSV)

- subsample(子采样)

- equalizehist(直方图均衡化)

- gaussianBlur(高斯模糊)

- sobel(Sobel 边缘检测)

- canny(Canny 边缘检测)

- dilation(膨胀)

- erosion(腐蚀)

2.2 自建 Overlay

以上提到的两个 Overlay:

- KV260 Base Overlay 无法使用 Pcam 5C(无法完成初始化)。

- Pynq-CV-OV5640 仅支持 Pynq-Z2 板卡。

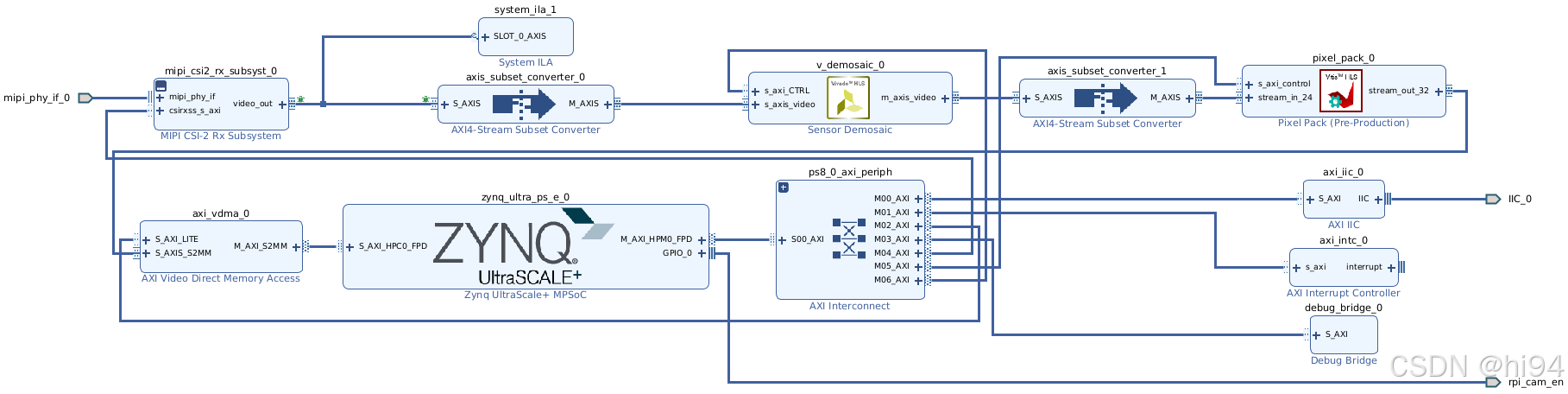

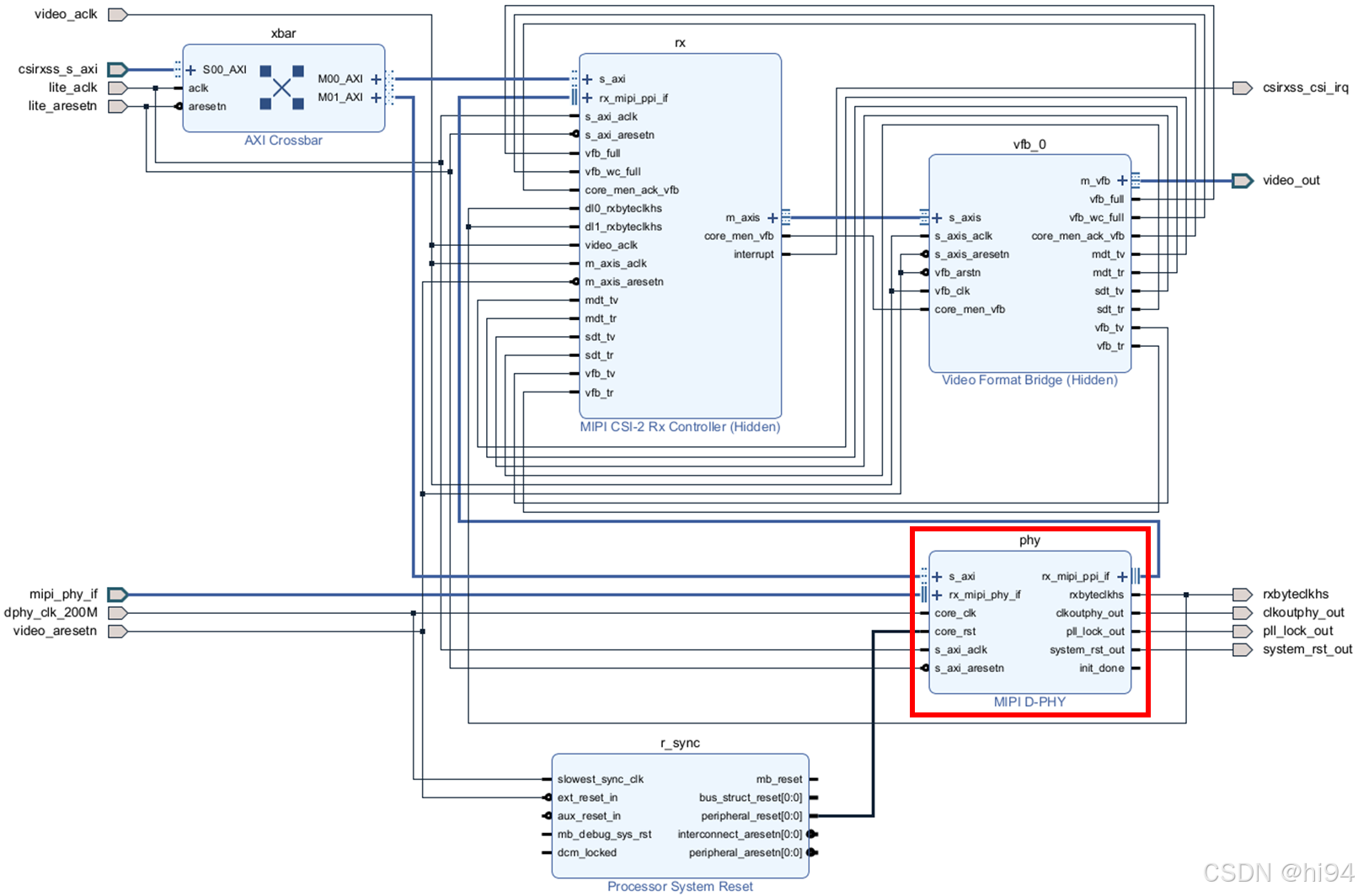

因此自建一个极简的 MIPI 调试平台如下:

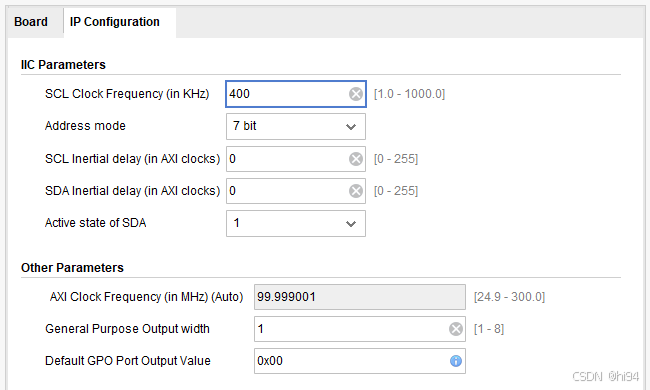

2.2.1 IIC IP

在 Base 中,axi_iic 模块使用了 100kHz 的总线频率,需要修改至 400kHz,否则会导致初始化失败。

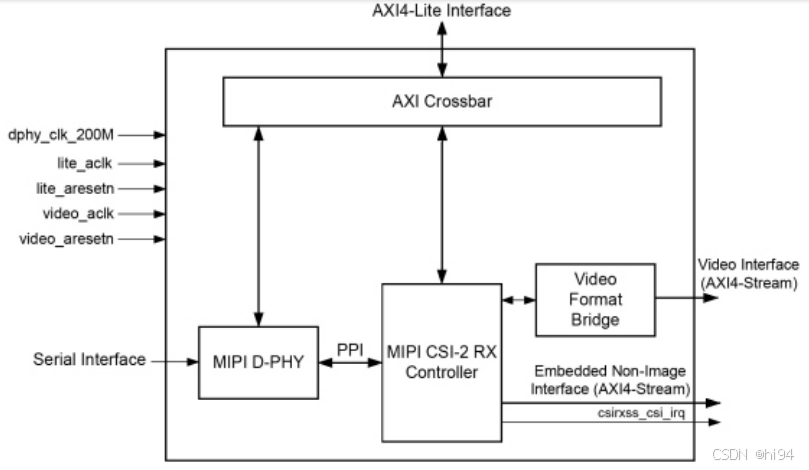

2.2.2 MIPI CSI-2 Rx

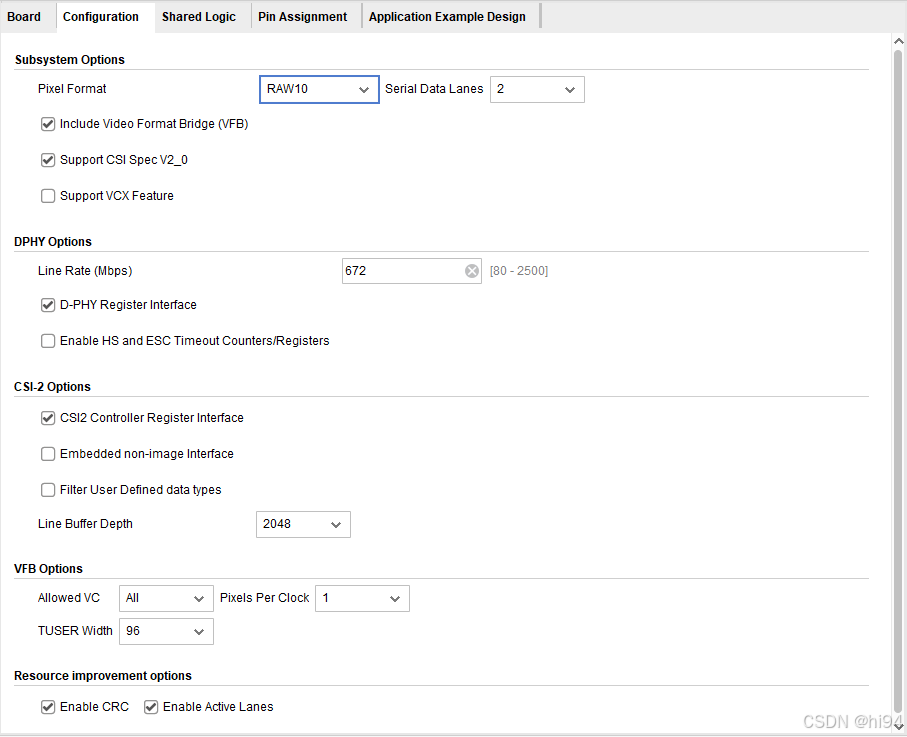

MIPI CSI-2 Rx Subsystem v5.1

MIPI CSI-2 RX Subsystem 通过 PPI(Pixel Parallel Interface)从 MIPI D-PHY 核心接收每个通道 8 位数据,支持最多 4 个通道。通过 PPI 接收到的字节数据随后由低级协议模块处理,以提取真实的图像信息。最终提取的图像通过使用 AXI4-Stream 协议,被提供给用户/处理器接口。无论通道数量如何,通道管理块始终处理从 PPI 接收的 32 位数据。

IP 的主要参数如下:

参数说明

- Pixel Format,由 sensor 决定,参考 4.4 Pixel 格式。

- 启用 CRC:当设置此选项时,将对数据包的有效载荷进行 CRC 校验。

-

启用活动通道:当设置此选项时,内核支持动态配置活动通道的数量,该数量可从内核生成时选择的最大通道数中调整,使用参数 Serial Data Lanes。例如,当 Serial Data Lanes 设置为 3 时,可以通过协议配置寄存器将活动通道的数量设置为 1、2 或 3。当活动通道设置大于串行通道设置时,内核会通过中断状态寄存器的第 21 位报告错误。

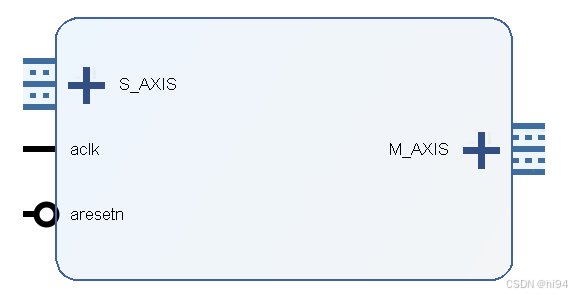

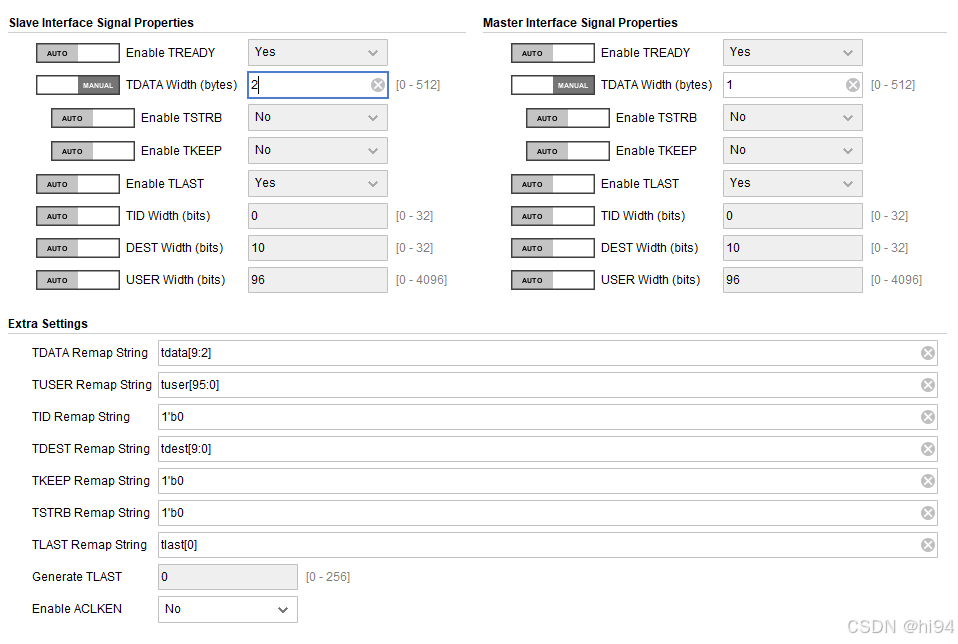

2.2.3 AXI4-S Subset

AXI4-Stream Subset Converter v1.1

属于 AXI4-Stream Infrastructure IP Suite (PG085) 的一个子 IP。

1)AXI4-Stream Subset Converter 参数配置

一般情况下,选择自动就可以,工具会自动推断前后级是否需要该信号。例如 TSTRB,工具发现前级没有此信号,后级也不需要,因此属性都是“No”。

Extra Settings(重映射字符串)

重映射用户参数的格式遵循类似于 Verilog 向量连接的语法。

- 直接传递:对于 TUSER,字符串 tuser[95:0] 表示将 SI 所有信号不加修改地传递给 MI。

- 位切片元素:对于 TDATA,字符串 tdata[9:2] 表示将 SI 的数据(16位)截取其中 [9:2] 的8位传递给 MI。

- 常量补充:如果 MI 的 TDATA 信号为24位而 SI 的 TDATA 信号为16位,重映射字符串8'b00000000,tdata[15:0] 将常量0分配给 MI 信号的高8位,并在低16位传递 SI 的 TDATA。

- 重复补充:字符串 tdata[7:0], tdata[7:0] 将 SI 的 TDATA 最低有效字节在 MI 信号上重复两次。

- 重映射字符串可以引用相应 SI 信号的位或其他可重映射SI信号的位。例如,TDATA 的重映射字符串可以引用 TUSER SI 信号的位。

- 仅支持二进制格式的常量元素。不支持 h 格式。

2)AXI4-Stream 基础设施套件

AXI4-Stream Infrastructure IP Suite (PG085) 提供了如下 IP:

- AXI4-Stream Broadcaster

- AXI4-Stream Clock Converter

- AXI4-Stream Combiner

- AXI4-Stream Data FIFO

- AXI4-Stream Data Width Converter

- AXI4-Stream Register Slice

- AXI4-Stream Subset Converter

- AXI4-Stream Switch

- AXI4-Stream Interconnect

这些集合能够执行数据切换/路由、数据宽度转换、流水线、时钟转换和数据缓冲。

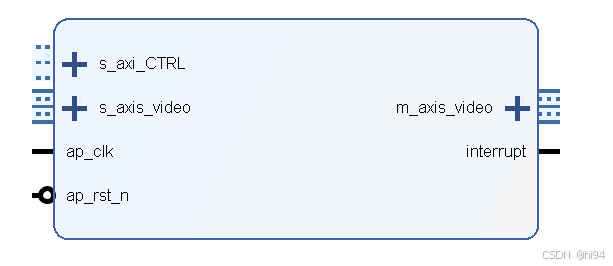

2.2.4 Demosaic

Sensor Demosaic v1.1

- 最大列/行数:指定 IP 核心在运行时可以处理的最大视频列/行数。任何小于该数值的视频宽度都可以通过 AXI4-Lite 控制接口进行配置,而无需重新生成 IP 核。

- 插值方法:

- Fringe Tolerant Interpolation(边缘容忍插值):生成的图像较为柔和,并抑制边缘伪影。对于可能引入颜色边缘伪影的低成本光学器件,建议使用此选项。

- High Resolution Interpolation(高分辨率插值):适用于高质量光学器件以及高分辨率的应用。此方法会使用更多的 BRAM 和 slice,并大约使 DSP48 的数量增加一倍。

- Horizontal Zipper Artifact Removal(水平拉链伪影去除):此选项添加一个后处理平滑滤波器,以去除水平拉链伪影。后处理滤波器会使输出图像变得柔和,并消耗一些额外的 Slice 资源。

- Use UltraRAM for Line Buffers(使用 UltraRAM 作为行缓冲):在 UltraScale+ 器件中,用于像素插值的行缓冲可以存储在 UltraRAM 中,而不是块 RAM。

1)基础地址空间

该 IP 核由 HLS 生成,所以其基础寄存器空间与 HLS IP 一致。

// ==============================================================

// control

// 0x0 : Control signals

// bit 0 - ap_start (Read/Write/COH)

// bit 1 - ap_done (Read/COR)

// bit 2 - ap_idle (Read)

// bit 3 - ap_ready (Read/COR)

// bit 7 - auto_restart (Read/Write)

// bit 9 - interrupt (Read)

// others - reserved

// 0x4 : Global Interrupt Enable Register

// bit 0 - Global Interrupt Enable (Read/Write)

// others - reserved

// 0x8 : IP Interrupt Enable Register (Read/Write)

// bit 0 - enable ap_done interrupt (Read/Write)

// bit 1 - enable ap_ready interrupt (Read/Write)

// others - reserved

// 0xc : IP Interrupt Status Register (Read/COR)

// bit 0 - ap_done (Read/COR)

// bit 1 - ap_ready (Read/COR)

// others - reserved

// (SC = Self Clear, COR = Clear on Read, TOW = Toggle on Write, COH = Clear on Handshake)2)额外的寄存器

| Address | Register Name | Access Type | Register Description |

|----------|---------------|-------------|-------------------------------------------------|

| 0x0010 | Active Width | R/W | Number of Active Pixels per Scanline |

| 0x0018 | Active Height | R/W | Number of Active Lines per Frame |

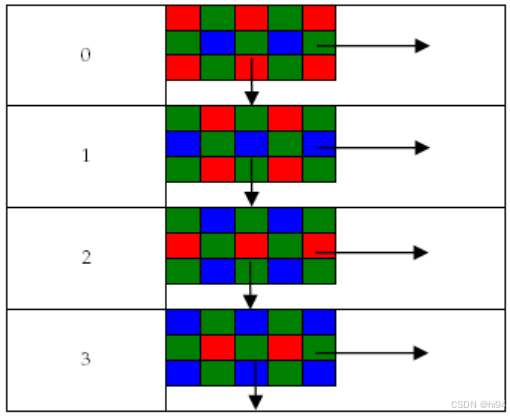

| 0x0028 | Bayer Phase | R/W | Bits 1-0: Bayer sampling grid starting position |3)Bayer Phase

Bayer Phase Register Combination Definitions

该 IP 核支持所有四种可能的拜耳相位(Bayer Phase)组合。

可以参照章节 4.4 Pixel 格式,对应关系如下:

IP OV5640(0x4300[3:0])

--------------------

3 -> 0x0: BGBG...

GRGR...

2 -> 0x1: GBGB...

RGRG...

1 -> 0x2: GRGR...

BGBG...

0 -> 0x3: RGRG...

GBGB...4)吞吐量

传感器去马赛克核心的像素吞吐量由 ap_clk 与 Sample per clock 设置的乘积定义。

例如,在 ap_clk 时钟频率为 300 MHz 且 Sample per clock = 2 的情况下,传感器去马赛克能够实现600万像素的吞吐率,可以以处理 60Hz 的 4K 分辨率。

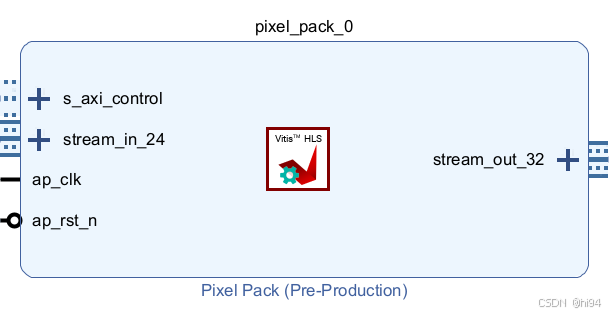

2.2.5 Pixel Pack

输入 Demosaic 为 8bit RGB RAW,输出为 RGB888 24bit 数据,这正是 pixcel_pack 模块输入端接收的数据。

pixel_pack kernel,从一个输入流 stream_in_24 读取24位像素数据,并根据给定的模式 mode 将这些数据转换和打包成32位的数据,然后将转换后的数据写入到输出流 stream_out_32 中。

Kernel 中定义了五种模式:V_24, V_32, V_8, V_16, V_16C,每种模式都有其特定的处理逻辑。

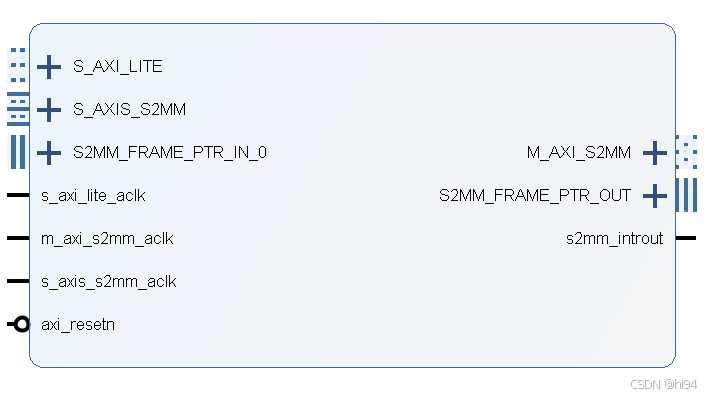

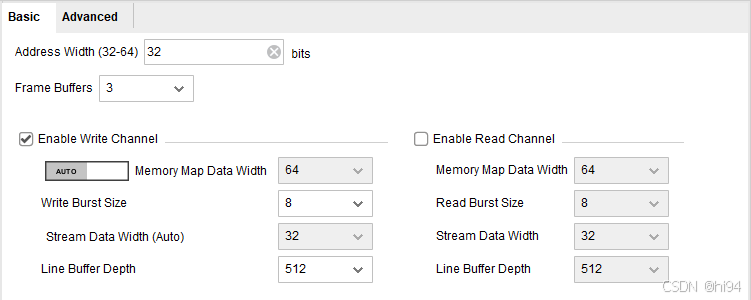

2.2.6 AXI VDMA

AXI Video Direct Memory Access v6.3

1)Basic Options

- Address Width,MAXI 总线的地址位宽,即 VDMA 的寻址范围。

- Frame Buffers,缓存帧的数量。

- Enable Channel,可以单独启用读/写通道。

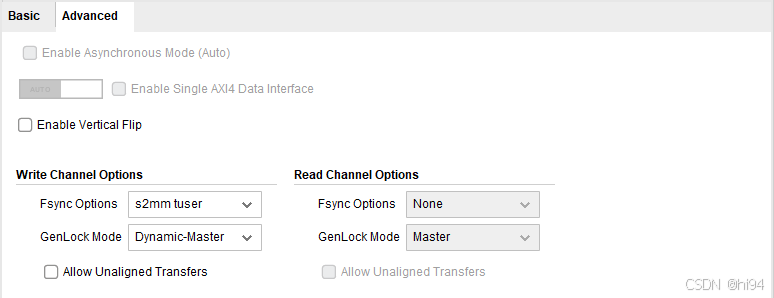

2)Advanced Options

- Enable Asynchronous Mode,启用异步模式,

此设置允许 m_axi_mm2s_aclk、m_axi_s2mm_aclk、s_axi_lite_aclk、m_axis_mm2s_aclk 和 s_axis_s2mm_aclk 互相异步。当禁用异步时钟时,所有时钟必须频率相同且来自同一源头。

- 启用垂直翻转

当选择此选项时,在启用 S2MM 的情况下将图像垂直翻转。

- Fsync 与 Genlock,请参见 IP 详解部分。

2.3 构建 XSA

<ov5640>/Pynq-CV-OV5640-master/boards/Pynq-Z2/ov5640/bitstream

---

build_bitstream.tcl

check_cv_ov5640.tcl

cv_ov5640.bit

cv_ov5640.hwh

cv_ov5640.tcl

cv_ov5640.xdc

__init__.py

makefile

3. IP 详解

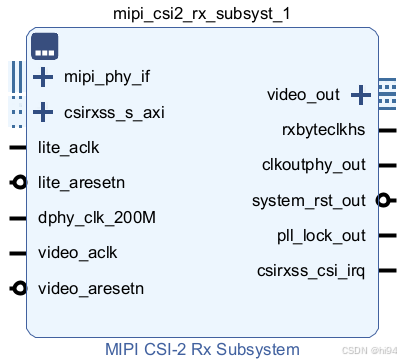

3.1 MIPI CSI-2 Rx Subsystem

3.1.1 IP 基本信息

IP 版本:MIPI CSI-2 Rx Subsystem v5.1

- dphy_clk_200M:Used for control logic and input to MMCM

- video_aclk:视频处理时钟域

- video_aresetn:视频处理时钟域复位

- rxbyteclkhs:PPI high-speed receive byte clock

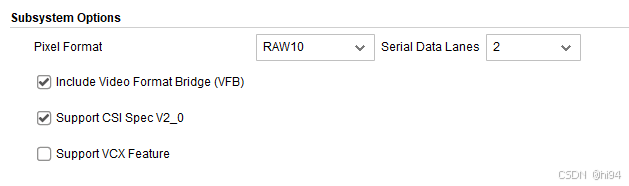

3.1.2 Subsystem Options

- Pixel Format

由传感器设置决定的。以 OV5640 为例, 由以下3个寄存器决定:

[0x3034, 0x1A], #[6:4]=001 PLL charge pump, [3:0]=1010 MIPI 10-bit mode

[0x4300, 0x00], #[7:4]=0x0 Formatter RAW, [3:0]=0x0 BGBG/GRGR

[0x501f, 0x03], #[2:0]=0x3 Format select ISP RAW (DPC)- VFB(Video Format Bridge)

视频格式桥接器,当此选项被禁用时,子系统将不考虑像素格式选择,可以自定义配置流数据宽度 (TDATA)。

- Support CSI Spec V2_0

支持 CSI V2.0 功能(RAW16, RAW20 支持和 VCX 功能支持)。

- Support VCX Feature

MIPI CSI-2 标准的 v2.0 版本中特定的 VCX 支持功能用于将可用虚拟通道的最大数量扩展到 16 个。默认不启用,支持4个 VC。

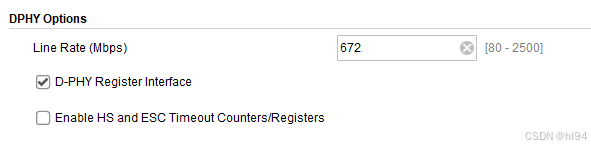

3.1.3 DPHY Options

线速率(Line Rate)要与摄像头 MIPI 输出速率匹配。简易原则如下:

- 1500 Mbps:IP 可以从 TX 接收 600-1500Mbps 的数据速率。

- 599 Mbps:IP 可以从 TX 接收 300-599Mbps 的数据速率。

- 299 Mbps:IP 可以从 TX 接收 150-299Mbps 的数据速率。

- 149 Mbps:IP 可以从 TX 接收 80-149Mbps 的数据速率。

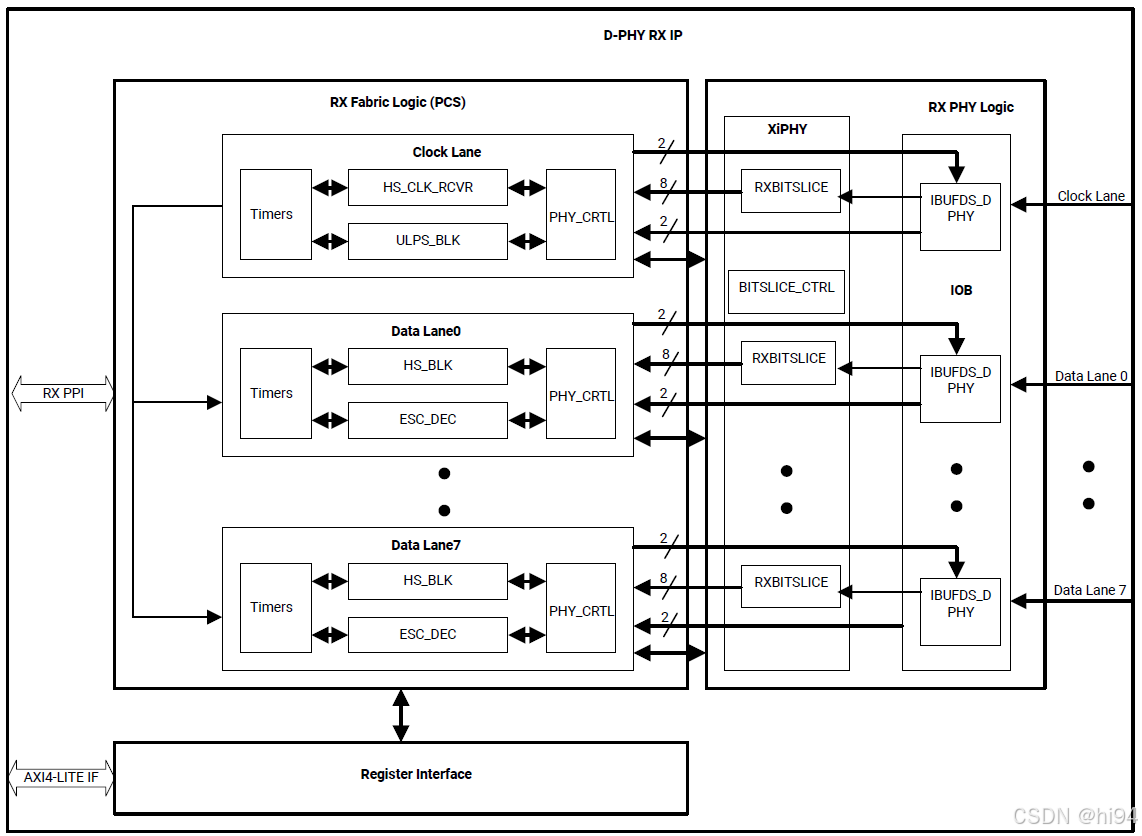

MIPI D-PHY RX (Slave) Core Architecture for UltraScale+ Families

- HS Timeout Counter:用于高速模式下的超时计数。当数据在高速模式下传输时,如果数据在预定时间内没有正确接收,核心会生成超时并进入停止状态。

- ESC Timeout Counter:用于逃逸模式下的超时计数。在逃逸模式下,如果数据在预定时间内没有正确接收,核心会生成超时并进入停止状态。

展开 MIPI CSI-2 Rx Subsystem 可以看到其中包含的 MIPI D-PHY 子模块,也可以查看 PPI 包含的信号,非常多。

3.1.4 CSI-2 Options

- CSI2 Controller Register Interface:AXI4-lite 寄存器接口。禁用此选项可以减少资源使用。

- Embedded non-image Interface:选择此选项以通过单独的 AXI4-Stream 接口处理和卸载嵌入式非图像 CSI-2 数据包(数据类型代码为 0x12)。如果未选择此选项,则此类数据包将不被处理,并被 CSI-2 RX 控制器忽略。

- Filter User Defined data types:选择此选项以过滤用户定义的数据类型(0x30 到 0x37),并且不在图像接口上输出(即使启用了过滤,未支持的 ErrId ISR[8] 也不会被设置)。如果未选择此选项,则此类数据包会被处理并在图像接口上显示。

- Line Buffer Depth:用于适应输出视频接口节流的内部 RAM 深度。可选值为 128、256、512、1024、2048、4096、8192 或 16384。用户可以将其设置为不会导致行缓冲区满状态的最低值。

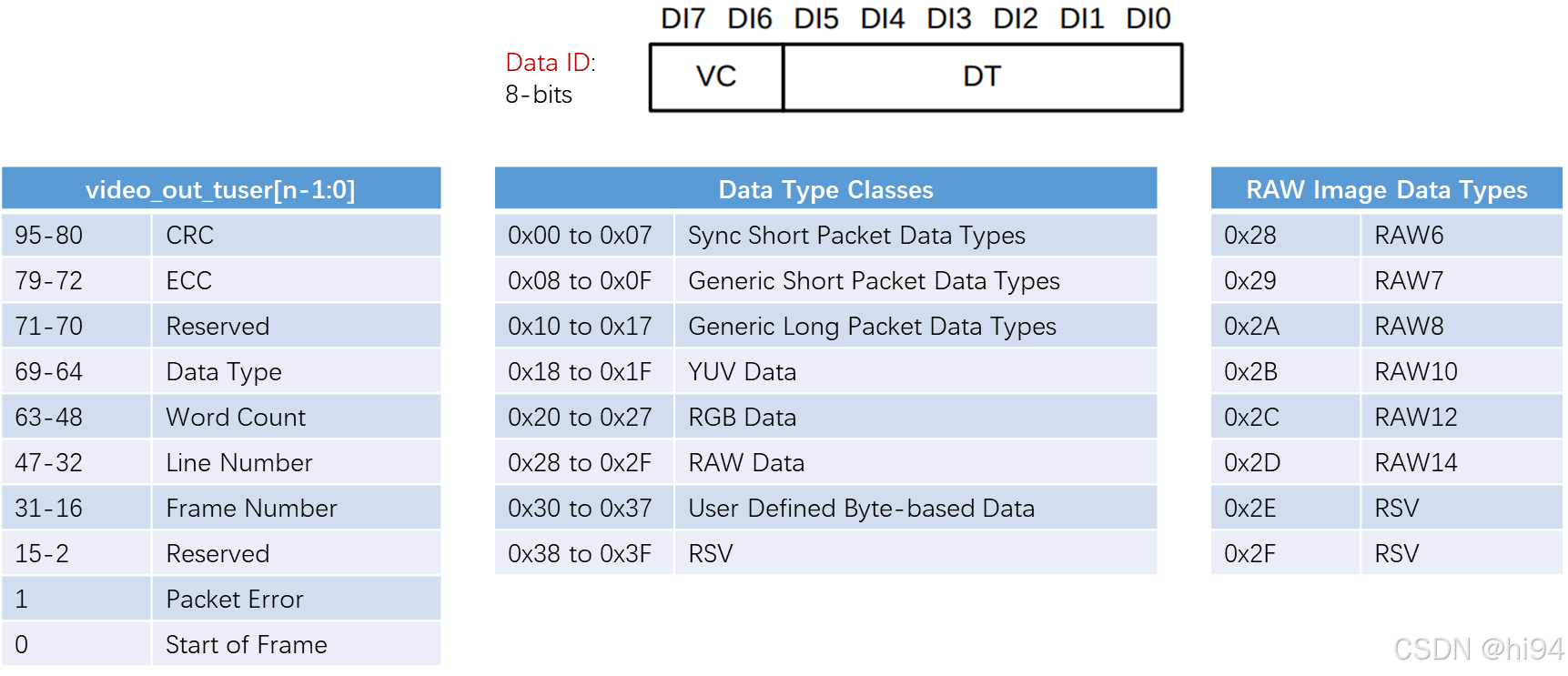

Data Type Classes:

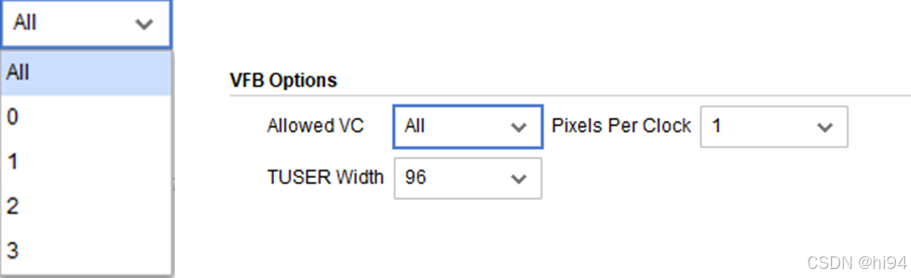

3.1.5 VFB Options

1)Video Format Bridge (VFB) 的主要作用:

- 数据过滤:处理并过滤来自 CSI-2 RX

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

9718

9718

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?