subarray的定义

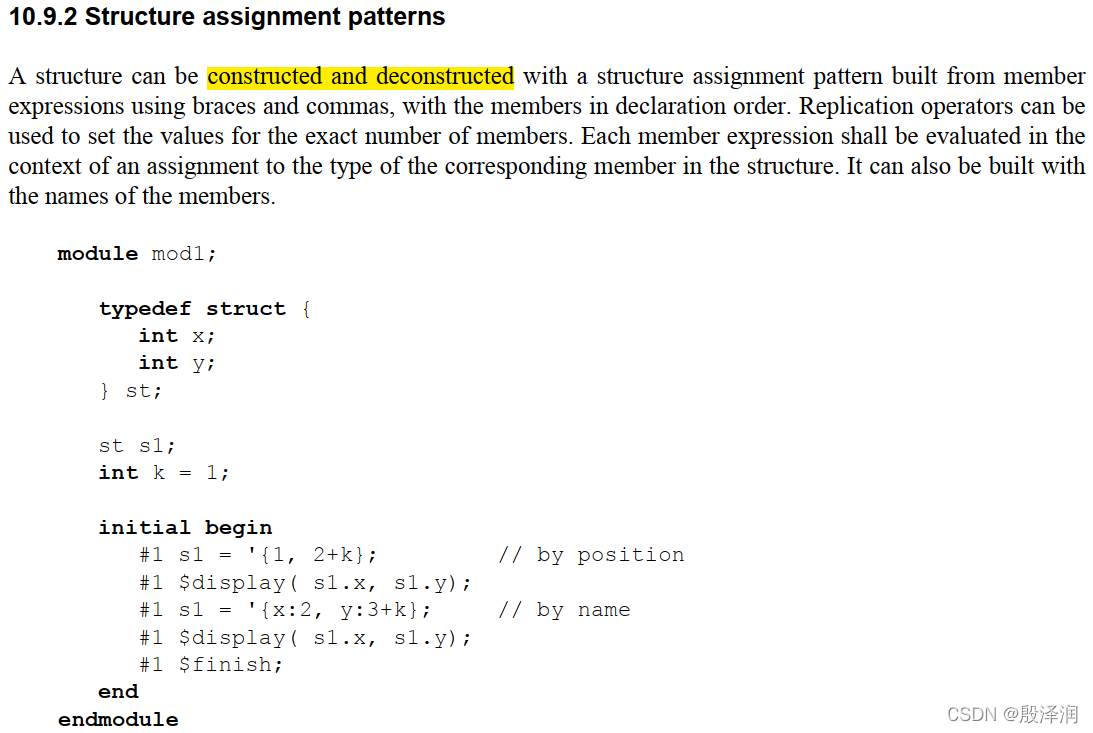

10.9 Assignment patterns

assignment pattern 和 assignment pattern expression不一样, 区别见文法.

- 优先设置index:value显示指定的元素的值.

- array的element type, subarray type就是array的type; 如果显示由type:value指定了, 则设置元素的值.

- 如果没有直接指定array type的value, 递归应用type和default key

- array of array (最终会拆到某个非array type的类型, 如simple bit vector, struct, int, real…)

- array of structure (应用struct的规则)

- 显示指定

- 由type:value设定不同type字段的值

- default:value

- is simple bit vector

- is not array or structure

DC的支持:

DC manual说不支持array pattern keys

281

281

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?