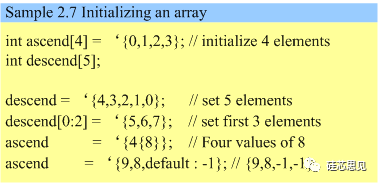

在SystemVerilog中根据数组中元素的存储方式,将数组细分为了packed数组和unpacked数组,packed数组一般使用拼接({})操作实现初始化赋值,unpacked数组则使用数值列表(‘{})的方式实现初始化赋值。根据大家熟知的绿皮书《SystemVerilog For Verification 2nd》中示例Sample 2.7中使用default等方式进行赋值,但是这个示例的仿真可能与我们期望的并不一样,仿真结果如下。

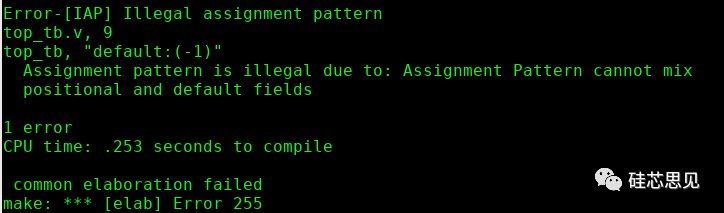

示例的仿真结果如下:

纳尼?为什么编译都不通过。主要是因为书中关于default的用法出现了错误导致的,此时想起了一句老话“尽信书不如无书”。那么下面我们将通过示例来说明如何对unpacked数组使用数值列表的方式进行各种赋值。示例之前,我们先来了解下SystemVerilog中对unpacked数组使用数值列表(value list)方式进行赋值的常见方式。

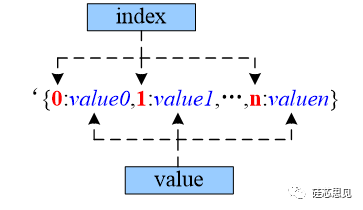

索引方式(index mode):通过数组“索引:数值”的方式对数组中具体元素进行赋值

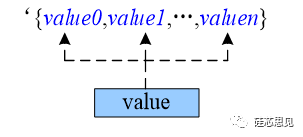

位置方式(positional mode):通过数值列表与数组中元素位置上的对应关系实现对应位置元素的赋值

元素类型方式(type mode):通过制定数组中具体元素类型,实现对特定类型元素的赋值

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3364

3364

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?