文章目录

前言

本文主要介绍TMS320F28335外围电路的设计方法。此设计方法为TI官方提供,实际应用中,可能要结合产品做微调。

本文主要参考资料:

- Hardware Design Guidelines for TMS320F28xx and TMS320F28xxx DSCs

- TMS320F2833x, TMS320F2823x Digital Signal Controllers (DSCs)

- 符晓,朱洪顺.TMS320F28335 DSP原理、开发及应用.清华大学出版社

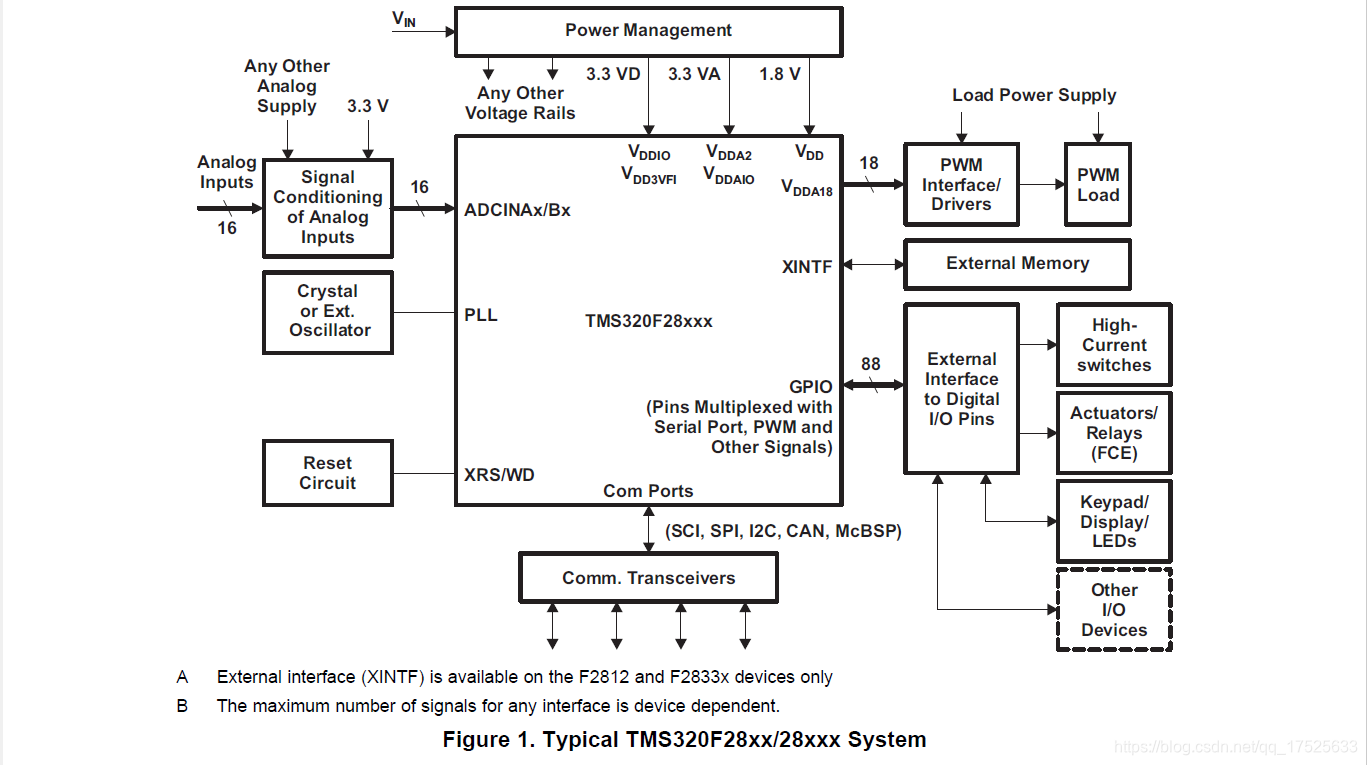

硬件系统总体架构

时钟电路

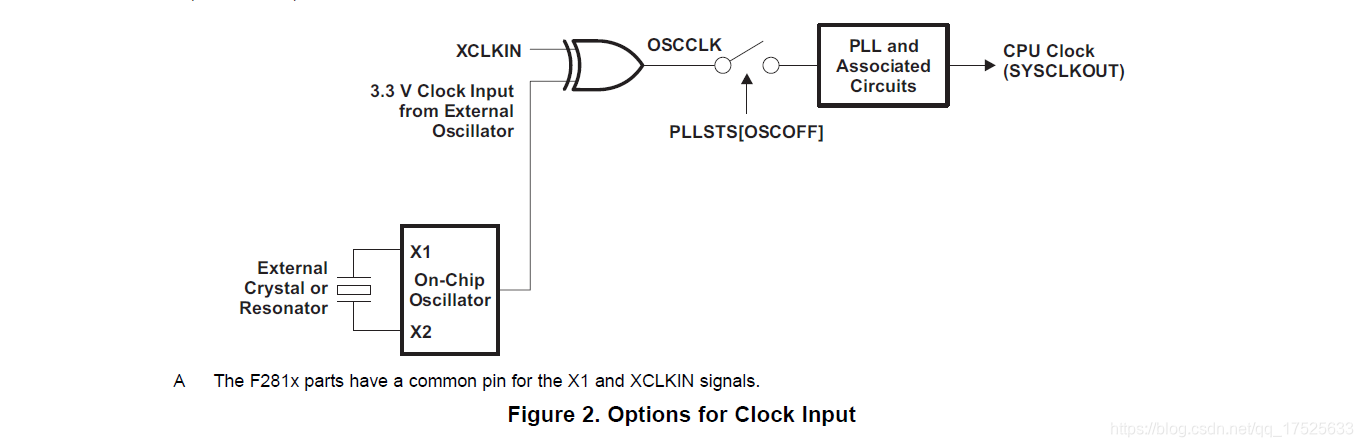

时钟电路可以分成两种情况:

- 使用内部振荡器

- 使用外部振荡器

如下图所示:

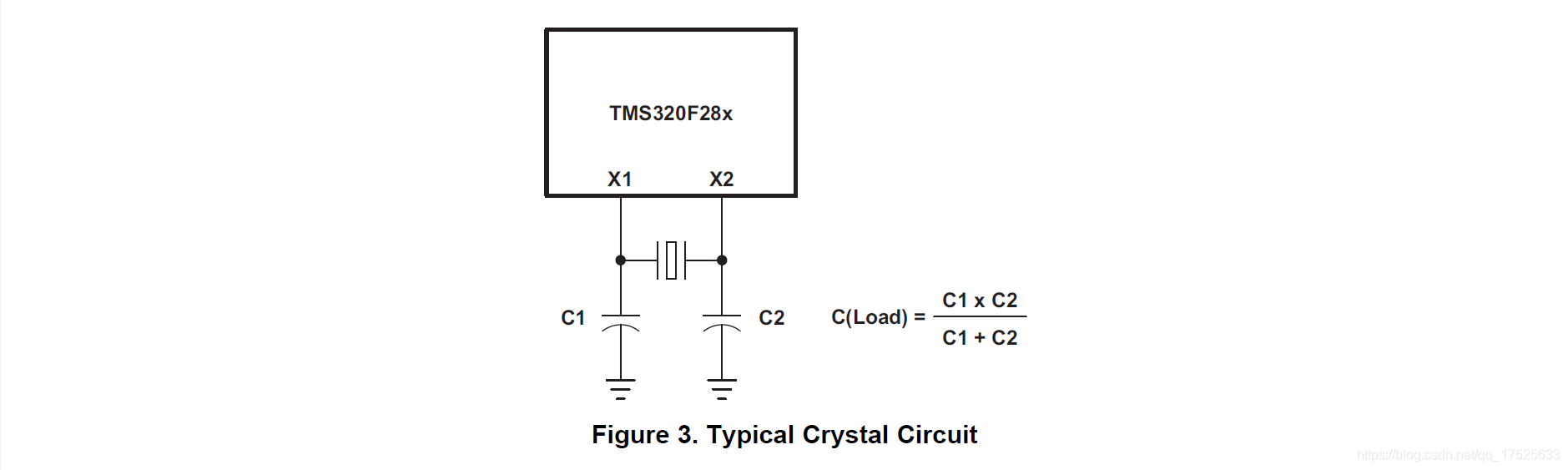

内部振荡器

下图显示使用内部振荡器时,外部晶振的接法:

其中,C(Load)为有效负载电容。推荐使用基模并联谐振型晶体。其有效负载电容为12pF,ESR在30Ω到60Ω左右。其等效于,取C1=C2=24pF.C1和C2所需的实际离散值通常比计算的负载电容低5 pf,这是由于PCB连线和DSC输入引脚的杂散电容造成的。

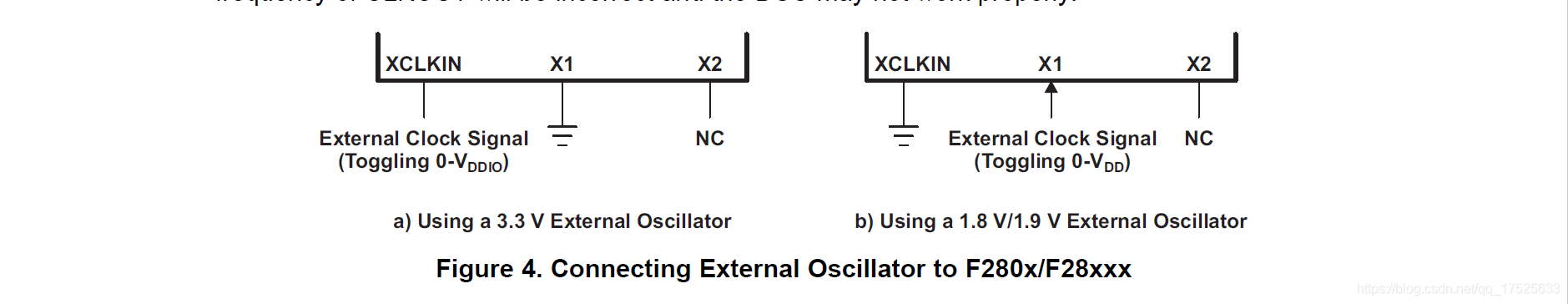

外部振荡器电路

外部振荡器电路如下图所示:

需要注意:当前X1或者XCLKIN不用时,需要将其接地,否则可能造成DSP不能正常工作。对于F28335来说,3.3V的外部振荡器可以直接连接到XCLKIN端,同样的1.9V/1.8V的外部振荡器可以直接连接到X1。

XCLKOUT

DSP输出的时钟信号,可以通过寄存器关闭。此时钟的驱动能力为8mA,可以用作外部通用时钟,可以用于测试CPU主时钟是否正确工作。在初始时,其为主时钟的4分频,其可以被设置为主时钟的2分频。即使不用,这个引脚也不要接地。

复位电路和看门狗电路

引脚 XRS ‾ \overline{\text{XRS}} XRS 是DSP设备复位的输入引脚和看门狗电路的复位输出引脚。

- 对于热复位来说,低电平脉冲宽度需要8个晶振时钟宽度。

- 对于上电复位来说,需要延时100ms以上,以满足系统各种延时。

- 若发生断电,则在VDD达到1.5V之前,许将复位引脚拉低至少8us,以保证Flash的可靠性。

- 若看门狗复位,将会产生512个晶振时钟宽度低电平脉冲。

对于引脚 XRS ‾ \overline{\text{XRS}} XRS,通常来说,普通的RC电路足够了。但是,若用集成芯片,则会提供更好的保护。

调试接口

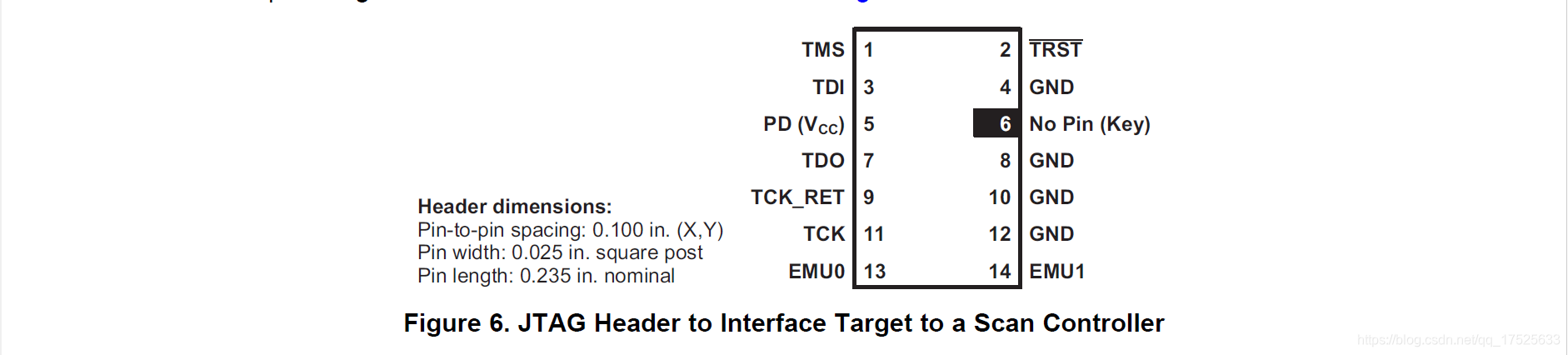

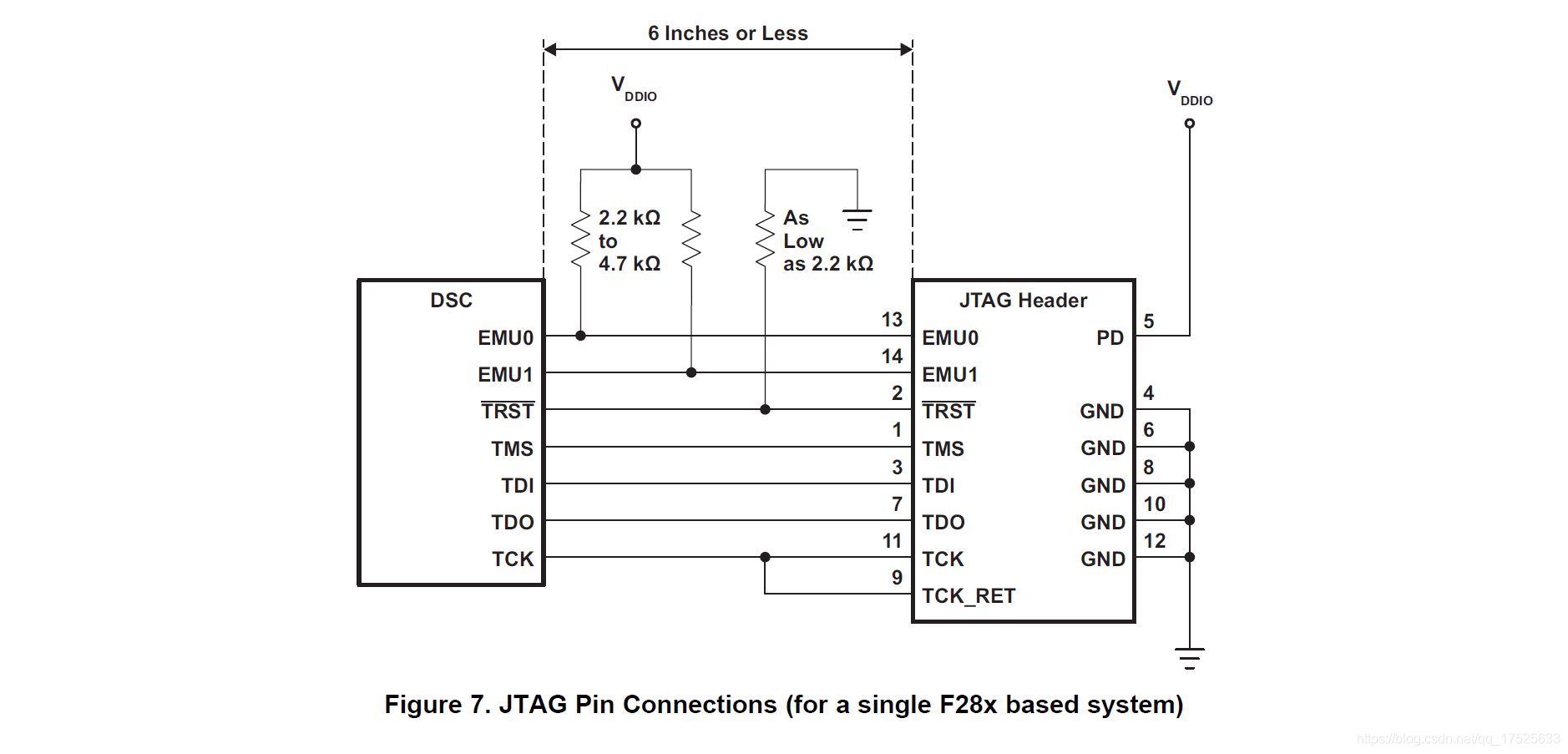

标准的JTAG接口如下图所示:

如图所示,该接口包含了:

- 五个标准IEEE标准信号: T R S T ‾ , T C K , T M S , T D I , T D O \overline{\rm{TRST}},\rm{TCK,TMS,TDI,TDO} TRST,TCK,TMS,TDI,TDO

- 两个TI拓展接口: E M U 0 , E M U 1 \rm{EMU0,EMU1} EMU0,EMU1

- 测试时钟返回信号: T C K _ R E T \rm{TCK\_RET} TCK_RET

- 电源和地

TCK_RET是测试时钟的返回信号,从仿真器输出进入目标系统。若目标系统不提供自身的测试时钟,目标系统将以TCK_RET作为测试时钟,因此,在很多系统中,将不会使用TCK信号。通常,将TCK_RET与TCK连接作为测试时钟。

TDO,EMU0,EMU1的驱动能力为8mA。

JTAG距离目标DSP的距离小于6英寸,最好为2英寸。若大于6英寸,则需要添加信号缓冲区。

| 信号 | 描述 | 仿真器状态 | 目标系统状态 |

|---|---|---|---|

| E M U 0 \rm{EMU0} EMU0 | 仿真引脚0 | 输入 | 输入/输出 |

| E M U 1 \rm{EMU1} EMU1 | 仿真引脚1 | 输入 | 输入/输出 |

| G N D \rm{GND} GND | 地 | ||

| P D ( V C C ) \rm{PD(VCC)} PD(VCC) | 存在检测。这个信号说明仿真器已经插入且目标系统已经上电。连接到VCC。 | 输入 | 输出 |

| T C K \rm{TCK} TCK | 测试时钟。此信号由仿真器产生,可以用于驱动系统测试时钟。 | 输出 | 输入 |

| T C K _ R E T \rm{TCK\_RET} TCK_RET | 测试时钟返回 | 输入 | 输出 |

| T D I \rm{TDI} TDI | 测试数据输入 | 输出 | 输入 |

| T D 0 \rm{TD0} TD0 | 测试数据输出 | 输入 | 输出 |

| T M S \rm{TMS} TMS | 测试模式选择 | 输出 | 输入 |

| T R S T ‾ \overline {\rm{TRST}} TRST | 测试复位 | 输出 | 输出 |

如上图所示,在关键信号EMU0,EMU1,TRST信号上提供了上拉与下拉以抑制噪声。若信号噪声依然干扰比较严重,可以与上拉电阻或者下拉电阻处并联旁路电容(0.01uF)。

至于一个仿真器连接多个目标系统等硬件设计方式,可以参考官方文档。这里不再详述。

中断、GPIO以及外设

GPIO

若无特殊说明,GPIO的驱动能力为4mA。F281X最大的反转频率为20MHz,F280X和F28XXX的为25MHz。默认情况下,GPIO在系统复位时,被重置为输入状态。若GPIO闲置不用时,可以将其配置为输出且空置管脚,或者可以将其设置为输入状态且连接到合适的输入终端。

理论上讲,浮动的输入还是会造成能量的浪费。所以,对于不重要的输入端,可以将其定义为输出且保持浮动,以减少能量的浪费。一个更好的方法是将闲置的输入端连接在一起,并保持默认的输入模式。连接在一起的闲置输入端,可以根据需要配置上拉或者下拉电路。

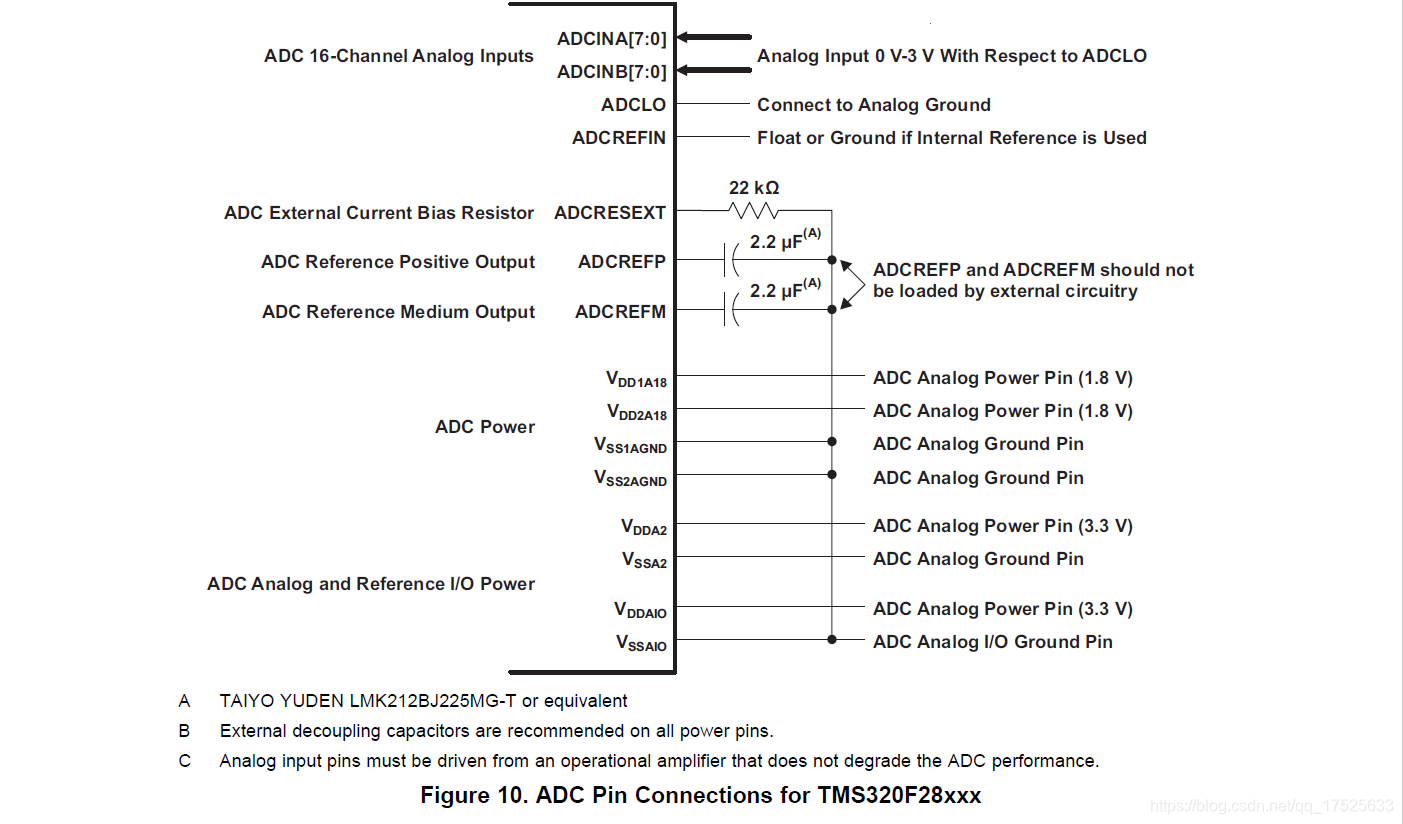

ADC

确认这些组件值正确,且距离对应管脚的距离要小。

8通道的电源输入端可以设计为上图所示。

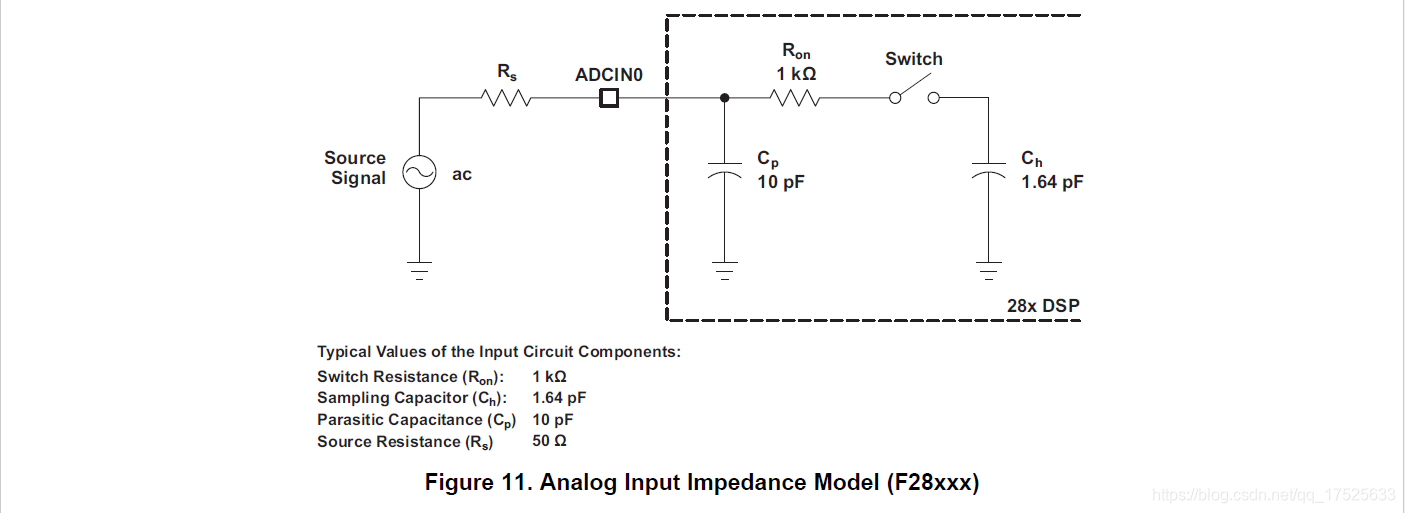

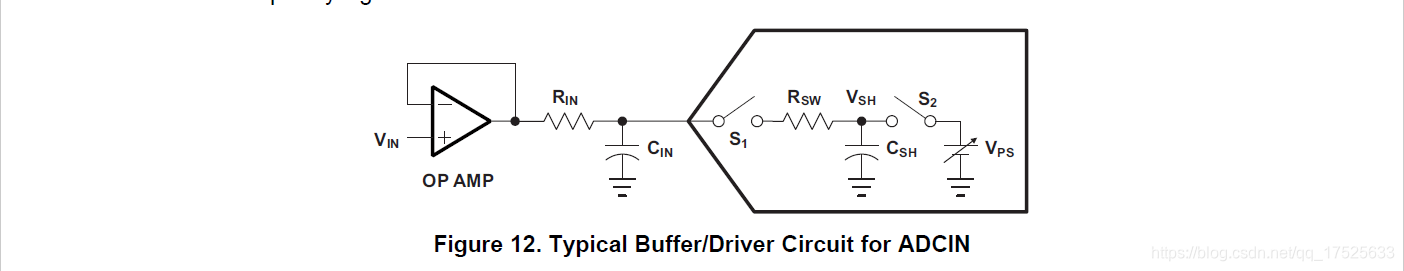

若使用运算放大器作为输入隔离是一个更好的选择。下图展示低频信号或者直流信号常用的ADC驱动电路。

其中,电容最佳值为30pF,电阻值选择与信号的带宽有关,但通常不超过100Ω。

注意:

ADCIN管脚的输入电压的取值范围为0-3V,偏离这个范围,将会获取错误的数字量。

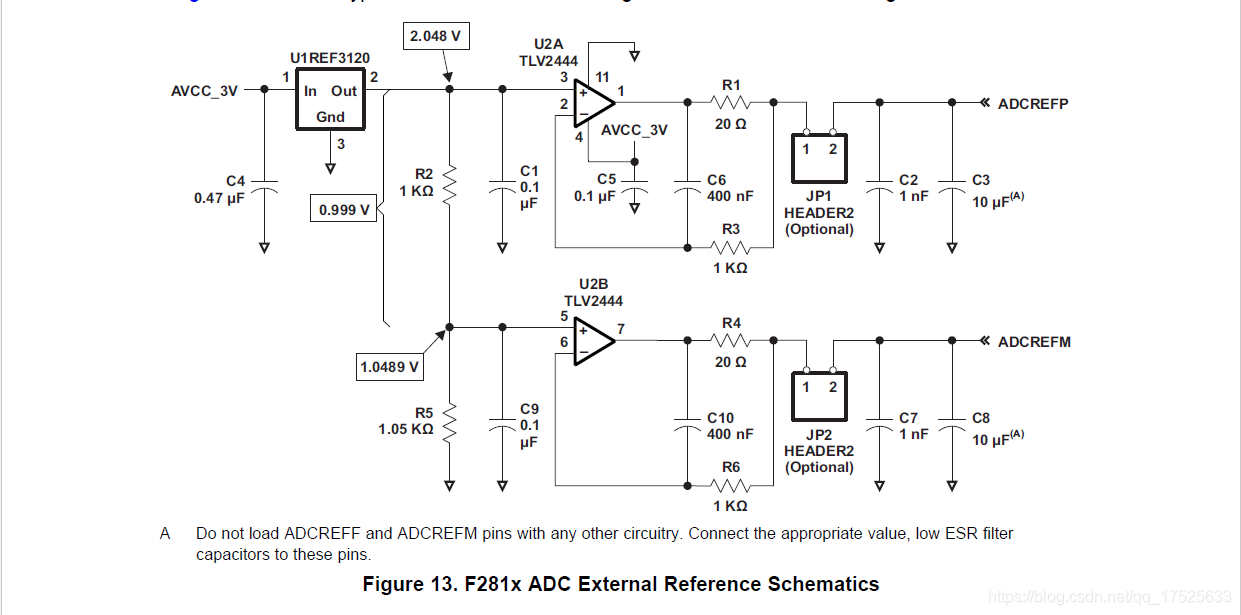

如果想要更好的温度稳定性,就需要使用外部参考电压。其具体电路图如下所示:

若想要了解更多信息,可以参考官方文档。

对于不用的引脚,一定要接入到模拟地。以防止噪声影响到其他组AD的作用。

即使AD模块没有被使用,依然推荐保持AD模拟电源引脚的链接。具体连接方式如下:

- VDD1A18/VDD2A18 – Connect to VDD

- VDDA2, VDDAIO – Connect to VDDIO

- VSS1AGND/VSS2AGND, VSSA2, VSSAIO – Connect to VSS

- ADCLO – Connect to VSS

- ADCREFIN – Connect to VSS

- ADCREFP/ADCREFM – Connect a 100-nF cap to VSS

- ADCRESEXT – Connect a 22-kΩ resistor (very loose tolerance) to VSS

- ADCINAn, ADCINBn - Connect to VSS

若AD模块不用,可以关闭AD的时钟,以节约电源。

控制外设

- 这部分电路一般不需要提供上拉/下拉电阻。

- 这部分电路的频率比较高且电流比较大,布局时需要注意噪声影响。

通信端口

- I2C和SPI通常在板内通信,连接控制器与外设。

- I2C和SPI通常可以直接使用。但是需要注意信号线的长度以及设定的通信频率。

- I2C的SCLA和SDAA管脚需要5kΩ的上拉电阻。

- 串口(SPI)和CAN通常是用于电路板之间通信,需要使用收发器。

XINTF

- 主要用于拓展系统存储,通常是RAM。

- 若与存储器相连接时,需要根据数据手册来判断是否需要添加缓冲器以保持高速访问。

- 若与慢速设备相连接时,需要使用XREADY管脚,以实现速度的协调。

- 使用XINTF连接外设时,需要将外设距离与DSP距离尽可能相近。

电源

F28XX/F28XXX设备包含多个电源供给,包括:

- CPU核心供电(VDD)

- I/O供电(VDDIO)

- ADC 模拟供电管脚(VDDA2,VDDAIO)

- ADC 核心供电(VDD1A18,VDD2A18)

- Flash 程序电压(VDD3VFL)

- 地(VSS,VSSIO)

- ADC模拟地(VSSA2,VSSAIO)

- ADC模拟/核心地(VSS1AGND,VDD2AGND)

所有的电源管脚都连接,DSP才能正常工作。所有I/O相关的管脚电压为3.3V,核心电压为1.8V或者1.9V。

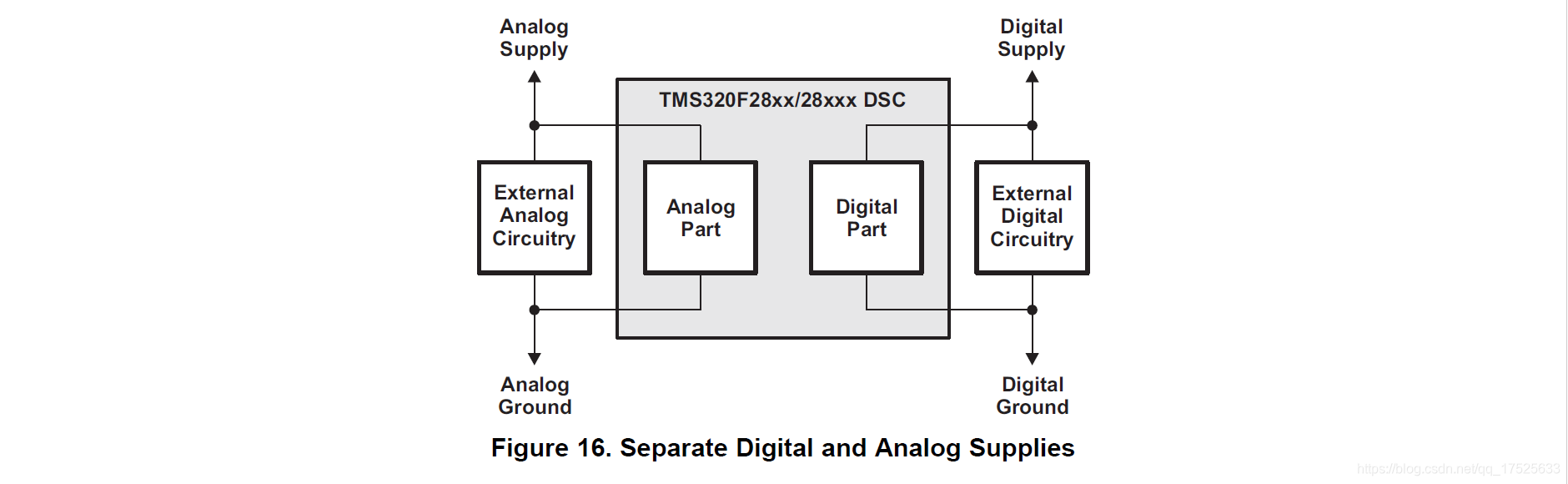

数字电源与模拟电源

如上图所示,为了避免数字信号干扰模拟电源的稳定性,需要将数字电源与模拟电源隔离处理。

对于大多数系统来说,模拟电路消耗的电源远远小于数字电路。因此,两者使用同一个电源供是能够提供足够的电流的。但是,需要将模拟电与噪声比较多的数字电隔离开。最简单的方法就是用电感之类的无源器件,这些器件可以滤除电路中的噪声成分。另一个更好的选择是铁氧体磁珠。其电气特性类似于电感,且其具有可忽略的寄生电容,和很小的直流电阻。在噪声比较严重的环境,可以考虑数字地和模拟地用不同的电源供电,但是此时需要密切注意的是,数字地可能会给模拟地带来耦合噪声。

上电顺序要求

要求VDD管脚通电时间早于或者等于VDDIO通电时间,以确保VDD管脚到达0.7V的时间比VDDIO的时间要早。否则,IO管脚的输出缓冲器可能在DSP内核通电之前导通,引发引脚输出错误。

另外推荐所有输入引脚的导通电压(0.7V)应该施加在DSP上电之后。否则,可能产生不可预知的后果。

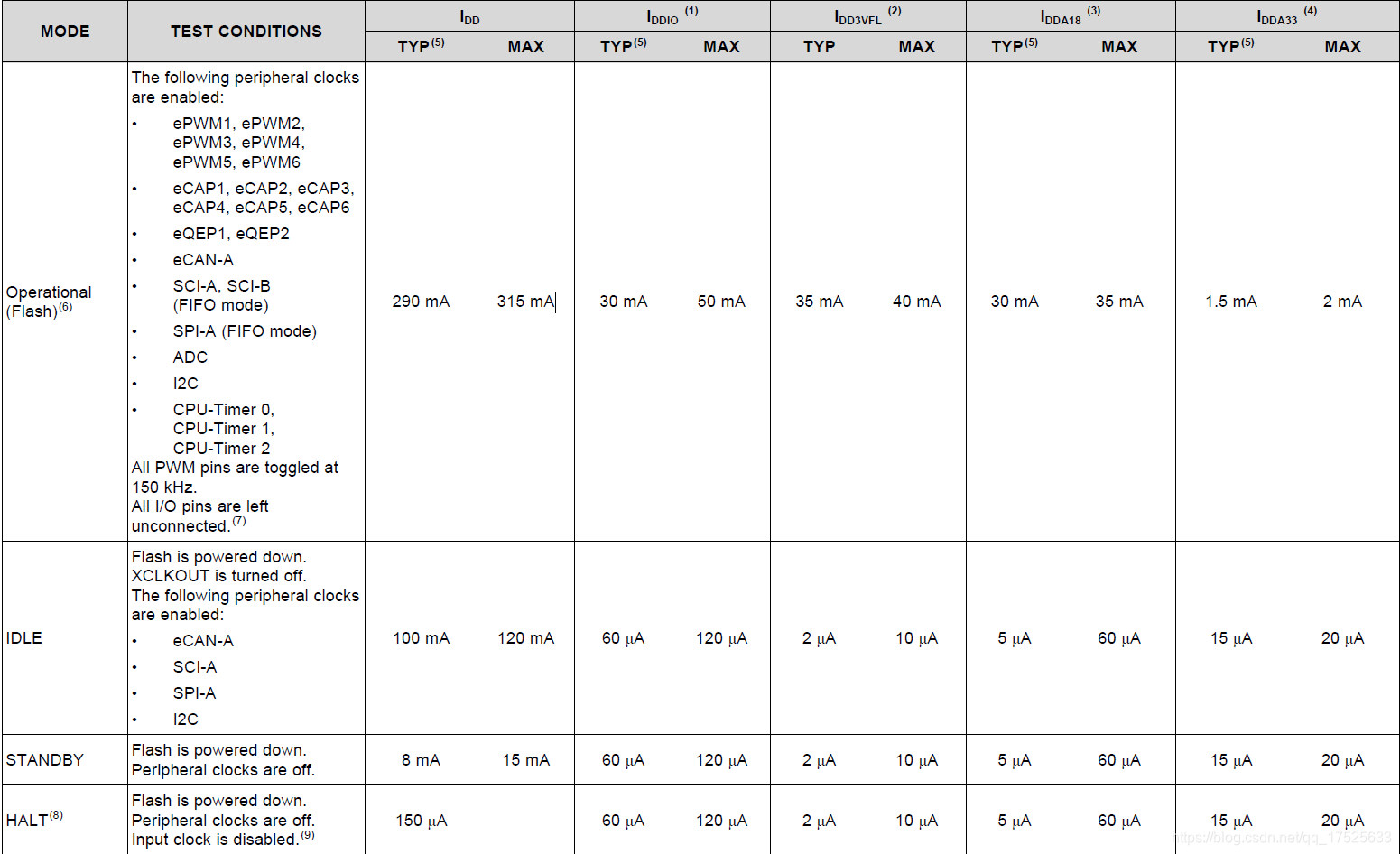

总功率要求和电压调节器选择

计算总功率时注意:

- 上电时由于电容充电,需要额外电流

- PWM切换电平需要更多的电流

- 若是使用内部Flash固化程序,则需要提高多余的电流消耗(大约200mA)。

如要计算总电流,则将数据手册中各个模块的最大电流相加即可。将所有的GPIO视为满载输出。考虑满裕度时的消耗,再将该值乘2来选择我电压调节器

电源调节器的噪声应该很小和更高的电源抑制比。 ADC的电压分辨率为0.732mV。

线性电压调节器(LDO)相比于开关电压调节器(DC-DC)拥有更低的噪声和更高的电源抑制比(PSRR),且对于负载的变化有更快的响应。但是,其效率更低,且若去耦电容过大,系统会不稳定。

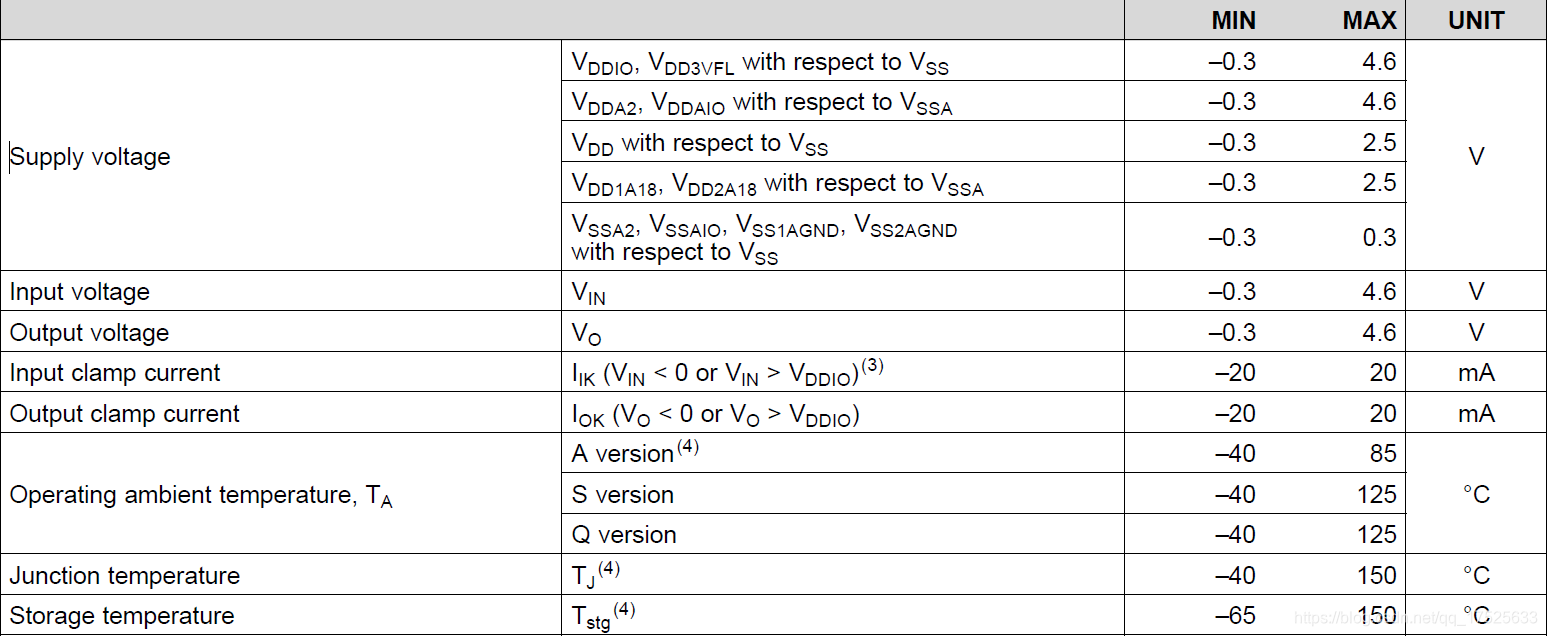

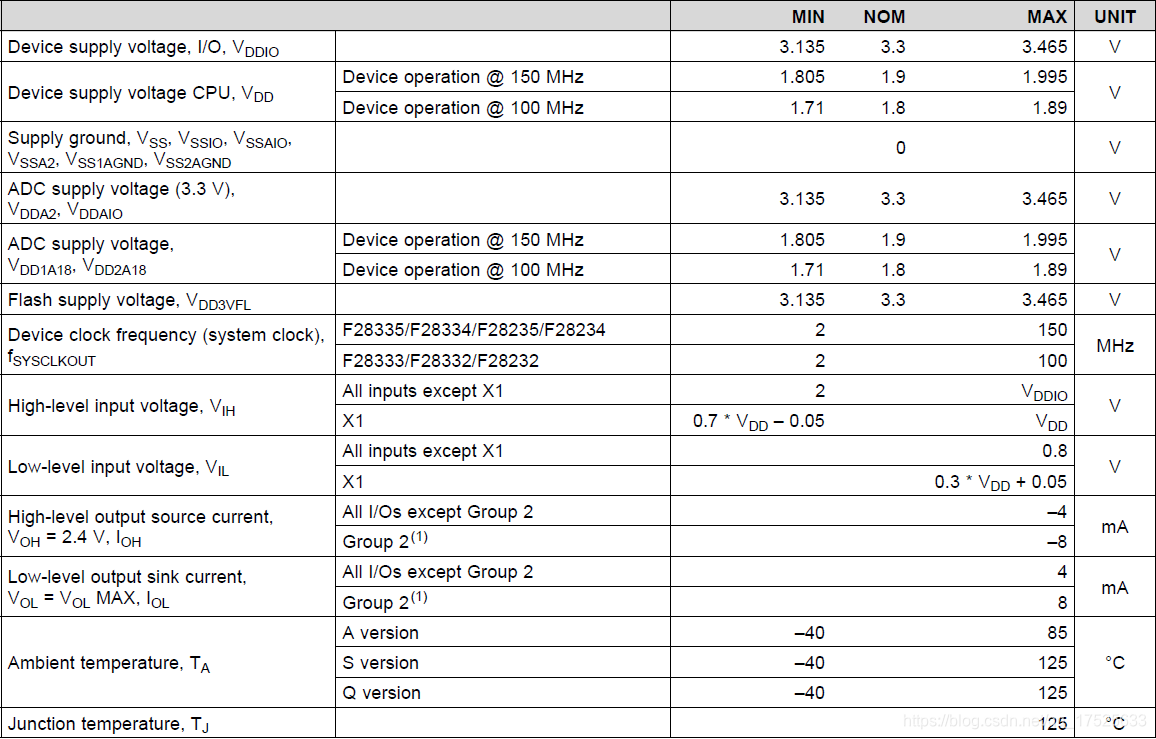

电气规范(F28335)

绝对最大额定值

- 超过表单数据工作,将会损坏元器件。上述数据只是应力额定值,元器件并不可以长时间在额定值下工作。长时间在最大值下工作,将会影响元器件的可靠性。

- 默认情况,所有的数据都是相对于VSS。

- 连续钳位电流为±2mA。包括模拟输入。

- 长时间高温下贮藏或者使用将会影响元器件的寿命。

推荐工作环境

- 组2包括的引脚有:GPIO28, GPIO29, GPIO30, GPIO31, TDO, XCLKOUT, EMU0, EMU1, XINTF pins, GPIO35-87, XRD.

电流消耗汇总

其余更多详细参数,可以参考官方手册<TMS320F2833x, TMS320F2823x Digital Signal Controllers (DSCs)>。由于官方手册名称和链接经常发生变化,所以,手册名称只是参数。链接也不再提供。

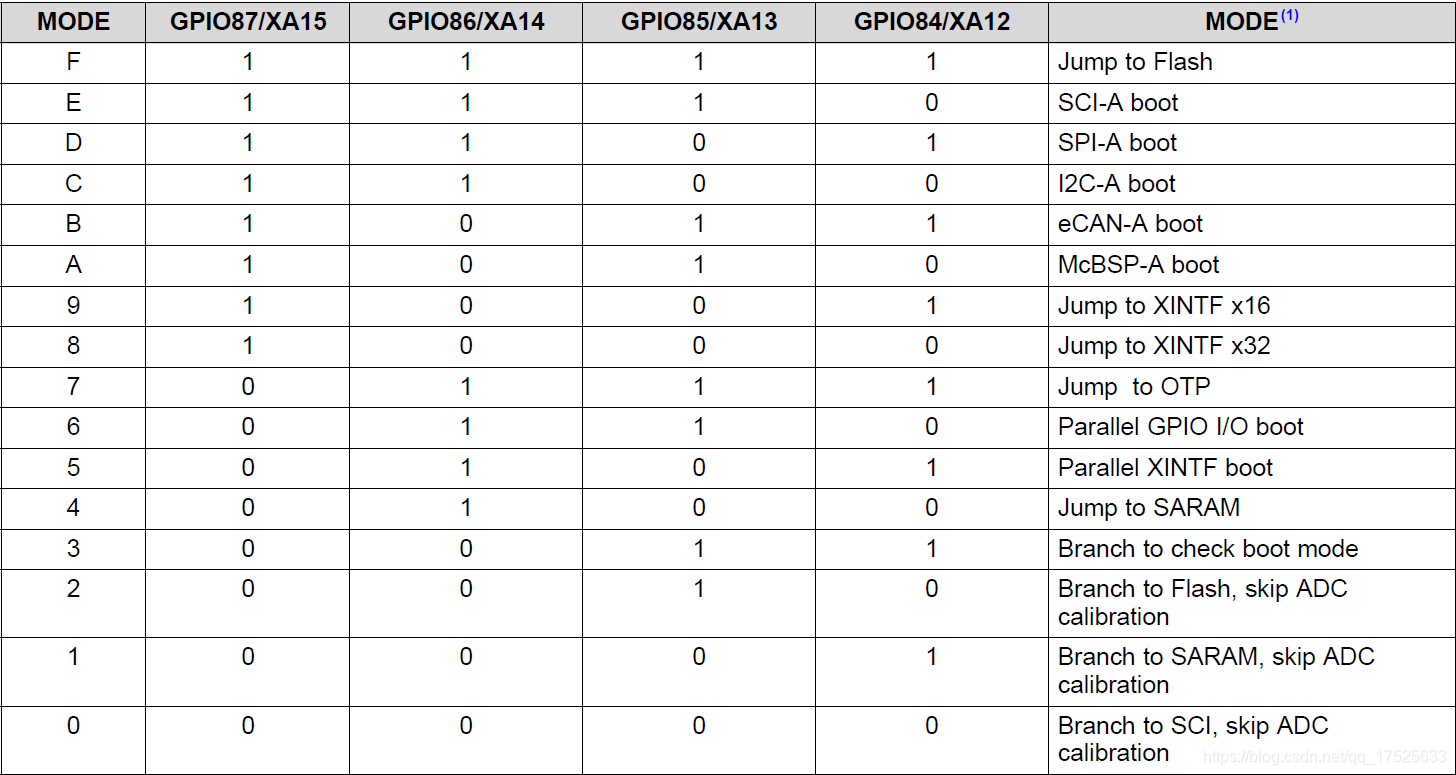

Boot引导

当设备复位时(上电重启或者热重启),在执行设备初始化之后,引导加载程序将会检查GPIO状态从而决定启动模式。

- 上述所有GPIO都有内部上拉,因此,如果选择Boot to Flash引导方式,则无须为四个引脚外接控制电路。

- 调试过程中,可以使用仿真器对引导方式直接配置,无须关注引脚状态。

旁路电容

为了电路的可靠性,需要在尽可能靠近电源管脚的地方放置旁路电容。每一个管脚各放一个电容。旁路电容的典型值很小(10nF-100nF),低low-ESR工艺。

若需要更加精细的设计,可以通过以下公式,计算特定的旁路电容值:

C

b

y

p

a

s

s

=

I

s

u

r

g

e

/

(

2

×

π

×

f

n

o

i

c

e

×

V

r

i

p

p

l

e

)

C_{bypass}=I_{surge}/(2\times \pi \times f_{noice} \times V_{ripple})

Cbypass=Isurge/(2×π×fnoice×Vripple)

其中:

I

s

u

r

g

e

I_{surge}

Isurge:浪涌电流

V

r

i

p

p

l

e

V_{ripple}

Vripple:纹波电压

f

n

o

i

c

e

f_{noice}

fnoice :噪声频率

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?