目录

声明:该文只适用于学习,其内容包含来自书本的摘抄和总结,欢迎大家补充,共同学习进步。

信号完整性简介

如今的PCB设计日趋复杂,高频时钟和快速开关逻辑意味着PCB设计已不仅是放置元器件和布线。网络阻抗、传输延迟、信号质量、反射、串扰和EMC(电磁兼容)是每个设计者必须考虑的因素,因而进行制版前的信号完整性分析更加重要。

AD包含一个高级的信号完整性仿真器,然后分析PCB设计和检查设计参数,测试过冲、下冲、阻抗和信号斜率。不过PCB上任何一个设计要求(设计规则指定)有问题,即可对PCB进行反射或串扰分析,以确定问题的所在。

AD的信号完整性分析与PCB设计过程中无缝连接,该模块提供了极其精确的板级分析,能检查整板的串扰、过冲/下冲、上升/下降时间和阻抗等问题。在PCB制造前,用最小的代价来解决高速电路设计带来的EMC/ EMI(电磁兼容/电磁抗干扰)等问题。

- AD的信号完整性分析模块具有如下特性。

·设置简便,可以和在PCB编辑器中定义设计规则一样,定义设计参数(阻抗等)

·通过运行DRC(设计规则检查),快速定位不符合设计要求的网络。

·无需特殊经验要求,可在PCB中直接进行信号完整性分析。

·提供快速的反射和串扰分析。

·利用I/O缓冲器宏模型,无需额外的spice或模拟仿真知识。

·完整性分析,结果采用示波器显示显示。

·成熟的传输线特性计算和并发仿真算法。

·用电阻和电容参数值对不同的终止策略进行假设分析,并可对逻辑系列快速替换。

2. AD的信号完整性分析模块中的I/O缓冲器模型具有如下特性

·宏模型逼近,使仿真更快更精确。

·提供IC模型库,包括校验模型。

·模型同INCASES EMC-WORKBENCH兼容。

·自动模型连接。

·支持I/O缓冲器模型的IBIS2工业标准子集。

·利用完整性宏模型编辑器可方便、快速的自定义模型。

·引用数据手册或测量值。

信号完整性模型

信号完整性分析是建立在元器件的模型基础之上的,这种模型称为signal integrity模型,简称SI模型。

很多元器件的SI模型与相应的原理图符号、封装模型、仿真模型等一起,被系统存放在集成库文件中,包括IC(集成电路)、 Resister(电阻类元器件)、 Capacitor(电容类元器件), Connector(连接器类元器件)、 Diode(二极管类元器件)、以及BJT(双极性晶体管类元器件)等。需要进行信号完整性分析时,用户应为设计中所用到的每一个元器件设置正确的SI模型。

为了简化设定SI模型的操作,并且在进行反射、串扰、振荡和不匹配阻抗等信号完整性分析时能够保证适当的精度和仿真速度,很多厂商为IC类的元器件提供了现成的引脚模型供设计者选择使用,这就是 IBIS( Input/ Output Buffer Information Specification)模型文件,扩展名为“ibs”。

IBIS模型是反映芯片驱动和接收电气特性的一种国际标准。它采用简单直观的文件格式,提供了直流的电压和电流曲线以及一系列的上升和下降时间、驱动输出电压、封装的寄生参数等信息,但并不泄露电路内部结构的知识产权细节,因而获得了很多芯片生产厂家的支持。此外,由于该模型比较简单,仿真分析时的计算量较少,但仿真精度却与其他模型(如spice模型)相当,这种优势在PCB的密度越来越高、需要仿真分析的设计细节越来越多的趋势下显得尤为重要。

AD系统的信号完整性分析中就采用了IC器件的IBIS模型,通过对信号线路的阻抗计算,得到信号响应及失真等仿真数据来检查设计信号的可靠性.

在系统提供的集成库中已包含了大量的IBIS,用户可对相应的元器件进行添加,必要时还可到元器件生产厂商网站免费下载相关联的IBIS模型文件。对于实在找不到的 IBIS模型文件,设计者还可以采用其他的方法,如依据芯片引脚的功能选用相似的IBIS模型,或通过实验测量建立简单的IBIS模型等。

IBIS模型文件的下载及添加

- 登录Altera公司的网站http://www.Altera.com.cn,在其下载中心处下载相应的ibis模型文件“Max2.zip”。

- 双击所放置的元器件“EPM240F100C4N”,打开“元器件属性”对话框。在“model”栏中,可以看到没有信号完整性模型。单击“Add”按钮,在弹出的“添加新模型”对话框中,选择“signal integrity”。

- 单击“确定”按钮后,打开“signal integrity model”对话框,该对话框显示了元器件的IBIS模型文件有关信息:“Unknown”。

- 单击窗口中的“import IBIS”按钮,这系统弹出“open IBIS file”对话框,供设计者查找所需的IBIS模型文件“Max2.ibs”。

- 单击“打开”按钮后,该IBIS模型文件已被添加成功,系统弹出相应的更新提示框.

- 单击“OK”按钮,关闭“IBIS Converter”对话框,返回原理图编辑环境。可以看到在“元器件属性”对话框的“model”栏中,信号完整性模型已被添加。执行“设计”->“Update PCB document”命令,可将该更新同步到PCB文件中。

信号完整性分析的环境设定

在复杂、高速的电路系统中,所用到的元器件数量以及种类都比较繁多,由于各种原因的限制,在信号完整性分析之前,用户未必能逐一进行相应的SI模型设定。因此,执行了信号完整性分析的命令之后,系统会首先进行自动检测,给出相应的状态信息,以帮助用户完成必要的SI模型设定与匹配。

- 打开一个点进行信号完整性分析的工程。

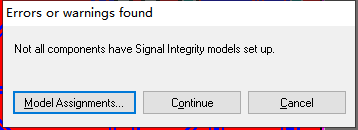

- 在原理图编辑环境中执行“工具”->“ Signal integrity”命令,或者在PCB编辑环境中,“工具”->“ Signal integrity”命令,开始运行信号完整性分析器,若设计文件中存在没有设定SI模型的元器件,则系统会弹出错误信息提示框。

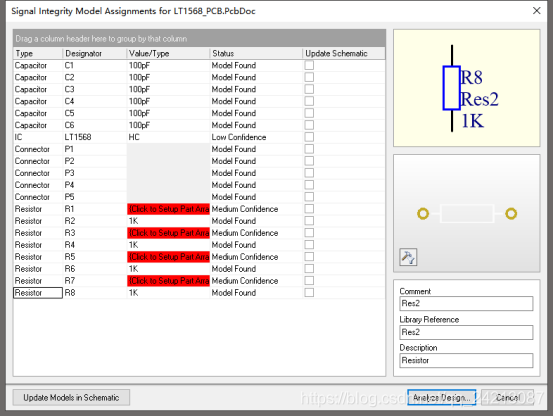

3. 单机该提示框中的“Model Assignments”按钮,会打开SI模型配置的显示对话框,显示每一元器件的SI模型及其所对应的配置状态,供用户查看或修改。

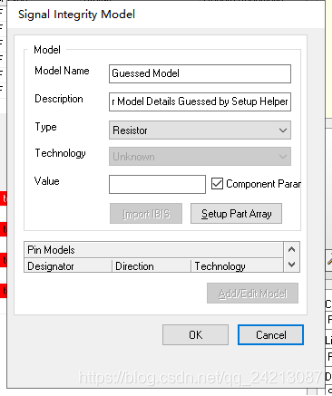

4. 双击某一元器件标识,会打开相应的“ Signal Integrity model”对话框。用户可进行元器件SI模型的重新设定,包括模型名称、描述、类型、技术、数值,并可编辑云角模型、设置元器件排列或导入IBIS模型文件等。

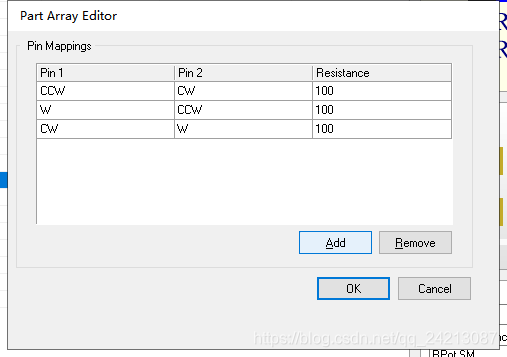

5. 在“ Signal integraty model assignments for Mixer_Routed”对话框中,单击“Type”栏或“Value/Type”栏,可直接进行单项的编辑。如选择某一器件,单击其被红色高亮标记的“Value/Type”栏,会打开“ Part Array editor”(元器件排列编辑器)对话框。

6. 将黄色高亮标记的元器件进行修改设置。

7. 单击“ Update models in Schematic”按钮,即可将修改后的模型信息更新到原理图中,这是对应的“ Status”栏中会显示“ Model Saved”(模型已保存)的状态信息。

信号完整性的设计规则

与自动布局和自动布线的过程类似,在PCB上进行信号完整性分析之前,也需要先对有关的规则加以合理设置,便准确检测出PCB上潜在的信号完整性问题。

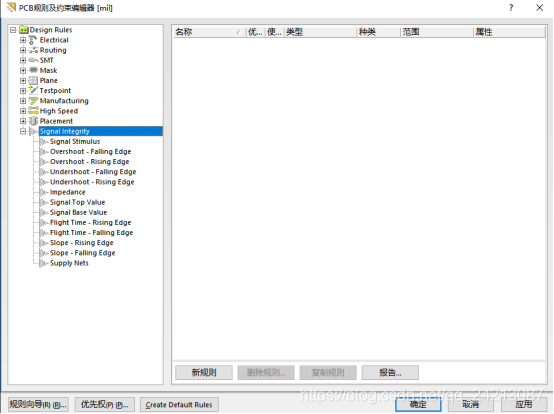

信号完整性分析的规则设置是通过“ PCB规则及约束编辑器”对话框来进行的。执行“设计”->“规则”命令,打开“PCB规则及约束编辑器”对话框。在左边目录区中,单击“ Signal Integrity”前面的+符号展开,可以看到信号完整性分析的规则一共有13项。设置时,在相应项上右击,添加新规则,之后可在新规则界面中进行具体设置。

- Signal Stimulus(激励信号)

该规则主要用于设置信号完整性分析中的激励信号特性

“约束”选项组中,需要设置的有如下几项。

·“ Stimulus类型”:激励信号类型设置。有三种选择:“ Constant Level”(常数电平即直流信号)、“ Signal Pulse”(单脉冲信号)和“Periodic Pulse”(周期性脉冲信号),系统默认设置为“ Signal Pulse”。

·“开始级别”:激励信号初始电平设置。有两种选择:“ Low level”(低电平)和“ High level”(高电平)。

·“开始时间”:激励信号开始时间设置。

·“停止时间”:激励信号停止时间设置。

·“时间周期”:激励信号周期设置。

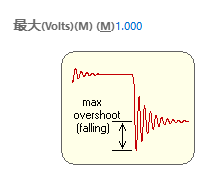

2. Overshoot-Falling Edge(信号过冲下降沿)

该规则主要用于设置信号下降沿所允许的最大过冲值,即低于信号基值的最大阻尼振荡。

在“约束”选项组中,只需要设置最大过充值的具体数值,即“最大(Volts)”,系统默认单位是V。

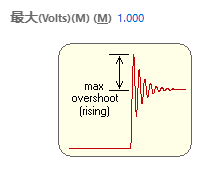

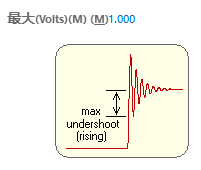

3. Overshoot-Rising Edge(信号过程上升沿)

该规则与上面的Overshoot-Falling Edge规则相对应,主要用于设置信号上升沿所允许的最大过冲值,既高于信号基值的最大阻尼振荡。在“约束”选项组中,只需要设置最大过充值的具体数值。

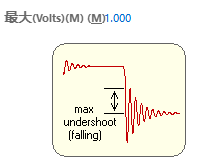

4. Undershoot-Falling Edge(信号下冲下降沿)

该规则主要用于设置信号下降沿所允许的最大下冲值,即下降沿上高于信号基值的最大阻尼振荡,具体数值在“约束”选项组中进行设置。

5. Undershoot-Rising Edge(信号下冲上升沿)

该规则主要用于设置信号上升沿所允许的最大下冲值,即上升沿上高于信号基值的最大阻尼振荡,具体数值在“约束”选项组中进行设置。

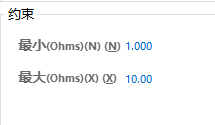

6. Impedance(阻抗)

该规则用于设置电路允许抗的最大值和最小值。

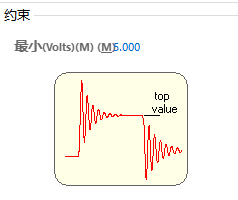

7. Signal Top Value(信号高电平)

该规则用于设置信号,在高电平状态下所允许的最小稳定电压值。

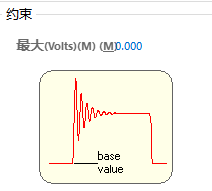

8. Signal Base Value(信号基准)

该规则用于设置信号基值电压的最大值。

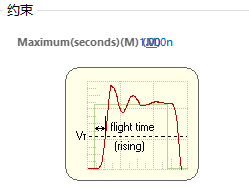

9. Flight Time-Rising Edge(飞行时间上升沿)

该规则用于设置信号上升源的最大延迟时间,一般指上升到信号设定值的50%时所需要的时间,具体数值可在“约束”选项组中进行设置,默认单位为S。

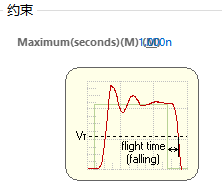

10. Flight Time-Falling Edge(飞行时间下降沿)

该规则用于设置信号下降沿边沿的最大延迟时间,一般指实际的输入电压到阈值电压之间的时间,具体数值在“约束”选项组中进行设置。

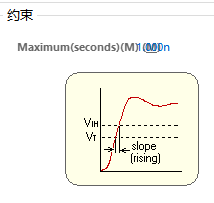

11. Slope-Rising Edge(上升沿斜率)

该规则用于设置信号的上升沿从阈值电压上升到高电平电压所允许的最大延迟时间。

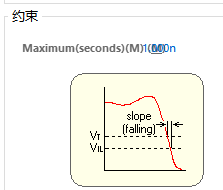

12. Slope-Falling Edge(下降沿斜率)

该规则用于设置信号的下降沿从阈值电压下降到低电平电压所允许的最大延迟时间。

13. Supply Nets(电源网络)

该规则用于设置PCB中电源网络或D网络的电压值,是在PCB编辑环境下进行信号完整性分析时所必须设定的规则。

电源网络及地网络的设置。

- 在“ PCB规则及约束编辑器”对话框中,选择“ Signal Integrity”->“ Supply Nets”规则,执行“新规则”命令,新建了一个“Supply Nets”子对话框。

- 单击新建的“Supply Nets”子规则,打开相应的设置对话框。

- 在“名称”文本框中输入“vcc”,在“ Where the first object matches”(第1个匹配对象的位置)中选择“网络”,单击按钮,在下拉列表框中选择“ Vccint”并在下面的“约束”选项组中设定“电压”值为“5V”。

- 单击“应用”按钮,完成该规则的设置。

- 再次选中“Supply Nets”规则,执行“新规则”命令,新建一个“Supply Nets”子规则。

- 打开设置窗口,在“名称”文本框中输入“ GND”,在“ Where's the first object matches”中选择“网络”,单击按钮,在下拉列表框中选择“ GND”并在下面的“约束”选项组中设定“电压”值为“0V”。

- 单击“应用”按钮,完成该规则的设置。

进行信号完整性的分析

信号完整性分析可以分为两步进行:第一步是对所有可能需要进行分析的网络进行一次初步的分析,从中可以了解到哪些网络的信号完整性最差;第二步是筛选出一些关键信号进行进一步的分析,已达到设计优化的目的,这两步的具体时间都是在信号完整性分析器中进行的。

信号完整性分析器

启动信号完整性分析器

- 在PCB编辑文件中设置了信号完整性分析的有关规则之后,执行“工具”->“signal integrity”命令,系统开始运行信号完整性分析器。

- 单击该提示框中的“ Model assignments”按钮,打开SI模型配置显示对话框,根据提示,进行元器件SI模型的设定或修改。

- 更新到原理图中之后,单机SI模型配置显示对话框中的“ Reanalyze Design.”按钮,打开“SI Setup options.”对话框。同时,在工作窗口的右下角面板标签处会出现一个“信号完整性”标签,意味着已启动了信号完整性分析器。

该对话框中有两个选项设置:“ Track impendance.”和“ Average Track Length”(平均布线长度)。“ Track impendance.”适用于没有设置布线阻抗的全部网络,设置了布线阻抗的网络则使用设定的阻抗规则进行信号完整性分析;“Average Track Length”适用于全部未布线的网络,选中“ Use Manhattan Length”复选框后,将使用曼哈顿布线的长度。

4. 单击“SI Setup options.”对话框中的“ Analyze design”按钮,系统即开始进行信号完整性分析。分析完毕后会打开“ Signal integrity.”对话框。

在该对话框的左侧显示了进行信号完整性初步分析的结果,包括各网络的状态以及是否通过了相应的规则,如上冲幅度、下冲幅度等。右侧可进行相应的设置,并对设计进行进一步的分析和优化。

串扰分析

- 菜单命令

对于信号完整性分析器的设置主要通过“ Signal integrity.”对话框中的菜单命令来完成。单击“Menu”按钮或在左侧窗口中右击,都会打开命令菜单。

·“ Select Net”选择网络。执行该命令,会将左侧窗口中某一选中的网络添加到右侧的“网络”选项组中。

·“ Details.”详细。执行该命令,系统会打开“ Full Result.”对话框,用于显示某一选中网络的详细分析结果,包括元器件数量、导线长度以及根据所设定的分析规则所得到的各项数值等。

·“Find Coupled Nets”:查找相关联网络。执行该命令后,所有与选中网络有关联的网络都会在左侧窗口中以选中状态显示出来。

·“ Cross Probe”:交叉探测。包括两个子命令,即“To Schematic”和“To PCB”,分别用于在原理图中或在PCB文件中查找所选中的网络。

·“ Copy”复制。用于复制某一选中网络或全部网络。

·“ Show/Hide Columns”:显示/隐藏纵向栏。该命令用于选择设置左侧窗口中的显示内容。对于不需要的内容,取消选择,即可隐藏。

·“ Preferences”:优先设定。执行该命令后,用户可以在打开的“ Signal integrity Preference.”对话框中设置信号完整性分析的相关选项。该对话框中有若干选项卡,不同的选项卡中设置内容是不同的。在信号完整性分析中,用到的主要是“ Configuration.”选项卡,可设置信号完整性分析的总时间、步长以及串扰分析时传输线间相互影响的距离。

·“ Set Tolerances”:设置容差。执行该命令后,系统会弹出“ Set screening Analysis tolerances”(设置扫描分析公差)对话框。

容差也称为公差,被用于限定一个误差范围,表示允许信号变形的最大值和最小值。将实际信号与这个范围相比较,就可以确定信号是否合乎要求。

在规则中设置容差

- 单击“ Set screening Analysis tolerances”对话框中的“ PCB Signal integrated rules.”按钮,打开“PCB规则及约束编辑器”对话框。

- 选中“ Signal integrity.”下的“ Undershoot-Falling Edge”规则,执行“新规则”命令,新建一个“UndershootFalling”子规则。

- 单击新建的“UndershootFalling”子规则,打开相应的设置对话框,进行设置。

- 设置完毕,返回“ Set screening Analysis tolerances”对话框中。可以看到刚才所设置的规则及优先权。

·“ Display Report.”:显示报告。执行该命令后,系统会在当前的工程的“ Generated.”文件夹下生成文本形式的信号完整性分析报告,同时显示在工作窗口中。

2. 功能按钮

·“Reanalyze Design.”:单击该按钮,将重新进行一次信号完整性分析。

·“ Model Assignments.”:单击该按钮,系统将返回到SI模型配置的显示窗口中.

·“ Reflection Waveforms”:用于进行反射分析。单击该按钮,刚进入仿真器的编辑环境中,显示相应的信号反射波形。

·“ Crosstalk Waveforms”:用于对选中的网络进行串扰分析,结果同样会以波形形式显示在仿真器编辑环境中。

·“ Perform Sweep.”:选中该复选框,系统分析时会按照用户所设置的参数范围,对整个设计的信号完整性进行扫描,类似于电路原理图仿真中的参数扫描方式。扫描步数可以在后面进行设置,系统默认选中。

·“ Suggest.”:选中该复选框,有关的参数值将由系统根据实际情况进行设置,用户不能更改;若不选中,则可自由进行设定。

串扰分析的波形显示

- 在“ Signal integrity.”对话框中选择两个网络,分别双击,将其移入右侧的“网络”选项组中。

- 在“ NCS4.”上右击,从弹出的快捷菜单中执行“ Set Aggressor”命令,将其设置为干扰源。

- 单击“ Crosstalk Waveforms”按钮,系统开始进行串扰分析。

- 分析结束,系统自动进入仿真编辑环境中,相应串扰分析的波形被显示在窗口中。

反射分析

- 打开工程中PCB设计文件,进入PCB设计环境中。

- 执行“设计”->“规则”命令,打开“PCB规则及约束编辑器”对话框。选中“ Signal integrity.”->“ Signal Stimulus”规则,执行“新规则”命令,新建一个“SignalStimulus”子规则。

- 单击新建的“SignalStimulus”子规则,打开设置对话框,设置“Stimulus类型”为“Periodic Pulse”,取采用系统的默认设置。

- 选中“ Signal integrity.”->“ Supply Nets”规则,执行“新规则”命令,新建一个“SupplyNets”子规则。打开设置对话框,在“ Where the first object matches.”中选择“网络”,单击按钮,在下拉列表框中选择“+15V”,在“约束”选项组中设定“电压”值为“15V”。

- 新建一个“SupplyNets”子规则,在“约束”选项组中设定“电压”值为“-15V”。再新建一个“SupplyNets”子规则设置接地网络。

- 实行“设计”->“层叠管理”命令,打开“Layer Stack Manager”,进行PCB层结构及参数的有关设置,如工作层面的厚度,导线的阻抗特性等。

- 执行“工具”->“ Signal integrity.”命令,系统开始运行信号完整性分析器。

- 单击该提示框中的“ Model Assignments.”按钮,打开SI模型配置显示对话框,进行元器件SI模型的设定或修改。

- 更新到原理图中之后,单机SI模型配置显示对话框中的“ Analyze Design”按钮,打开“SI Setup Options.”对话框,进行选项设定。

- 单击“SI Setup Options.”对话框中的“Reanalyze Design”按钮,系统即开始进行信号完整性分析。

- 分析完毕“ Signal integrity.”对话框会打开。选中某一网络,右击,在弹出的快捷菜单中执行“ Details.”命令,可以查看相关的详细信息。

- 双击网络“NetC5_1”,将其移入右边的“网络”选项组中,单击“ Reflection Waveforms”按钮,系统开始运行反射分析。

- 单击窗口右下角面板标签处的“ Editor.”按钮,在弹出的菜单中执行“信号完整性”命令,返回“ Signal integrity.”对话框中。

- 在“端接方式”选项组中,选中“Serial Res”复选框,并设置电阻的阻值范围,最小为“25Ω”,最大为“100Ω”。选中“执行扫描”复选框,扫描步数采用系统的默认值“10”。

- 单击“Reflection Waveforms”按钮。

- 在“ Signal integrity.”对话框中直接输入一个具体的串接电阻值“47Ω”,取消选中“执行扫描”复选框,以便更清楚的比较串接电阻前后的信号波形变化。

- 单击“Reflection Waveforms”按钮后,反射波形图中有两条曲线,浅色曲线是没有串接电阻时的波形,而深色曲线则是串接了47Ω电阻后的信号波形,波形中的过充现象已明显减小,上升沿及下降沿变得平滑。因此,根据词阻值可以选择一个比较合适的电阻串接在PCB的相应网络上。

本文详述了PCB设计中信号完整性的概念、重要性以及如何进行信号完整性分析。通过AD软件,设计师可以进行反射、串扰分析,确保高速电路设计的信号质量。信号完整性模型,如IBIS模型,对于精确仿真至关重要。同时,文章介绍了如何设定信号完整性规则,以及在遇到问题时如何调整元器件模型。通过这些步骤,设计师能有效预防和解决PCB设计中的信号完整性问题。

本文详述了PCB设计中信号完整性的概念、重要性以及如何进行信号完整性分析。通过AD软件,设计师可以进行反射、串扰分析,确保高速电路设计的信号质量。信号完整性模型,如IBIS模型,对于精确仿真至关重要。同时,文章介绍了如何设定信号完整性规则,以及在遇到问题时如何调整元器件模型。通过这些步骤,设计师能有效预防和解决PCB设计中的信号完整性问题。

489

489

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?