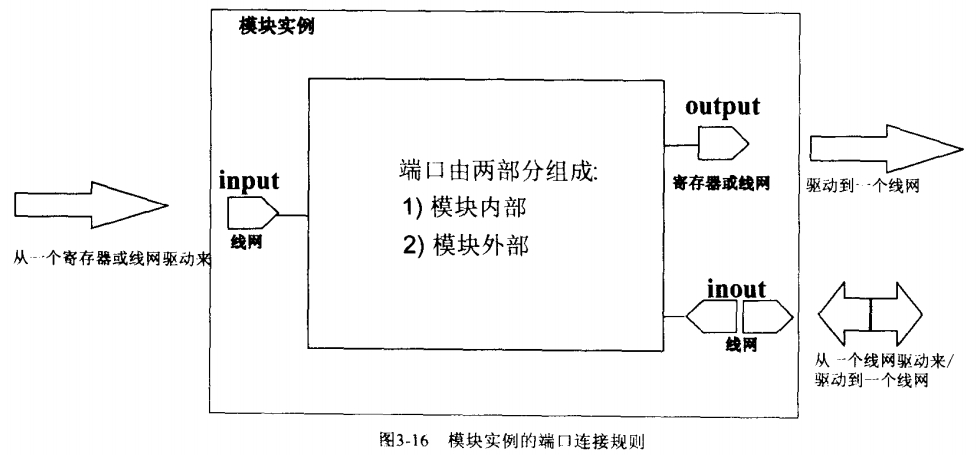

FPGA模块端口连接规则

一个模块内部

输入/输出/双向端口的属性。

- Input : 在模块内部缺省为一个线网类型。

- Output : 在模块内部是个寄存器(在过程赋值语句中被赋值)或者线网类型。

- Inout : 在模块内部缺省为一个线网类型,是双向信号, 一般定义为tri.当这个模块被实例化时,与之相连的信号类型如下:

• 与模块 input 端口相连: 可以是一个线网或者寄存器。

• 与模块 output 端口相连: 一定是驱动到一个线网。

• 与模块 inout 端口相连:输入时从一个线网驱动来,输出时驱动到一个线网。

876

876

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?