#致知穷理,学古探微;立德立言,无问西东。

有一段时间没写这个系列了,一个是我遇到的都是些小问题,大部分情况下还是我自己的问题,另一个也是一直忙于调试代码,导致了没有太多的时间去使用EDA软件。今天重新提及一下这个系列,也是我最近遇到的问题 and 解决方法。

一、 在Robei EDA里连接内部信号

一般来说,在代码模块之间的例化上,会存在两种端口例化的情况,一种是端口配输入输出线,直截了当,另一种是端口配上一级模块的内部信号,在高一级的模块里使用完了就不再引出信号线了。在Quartus 或者 Vivado 里,这两个操作没有什么不同,但是在 Robei EDA里,它的使用略有不同。

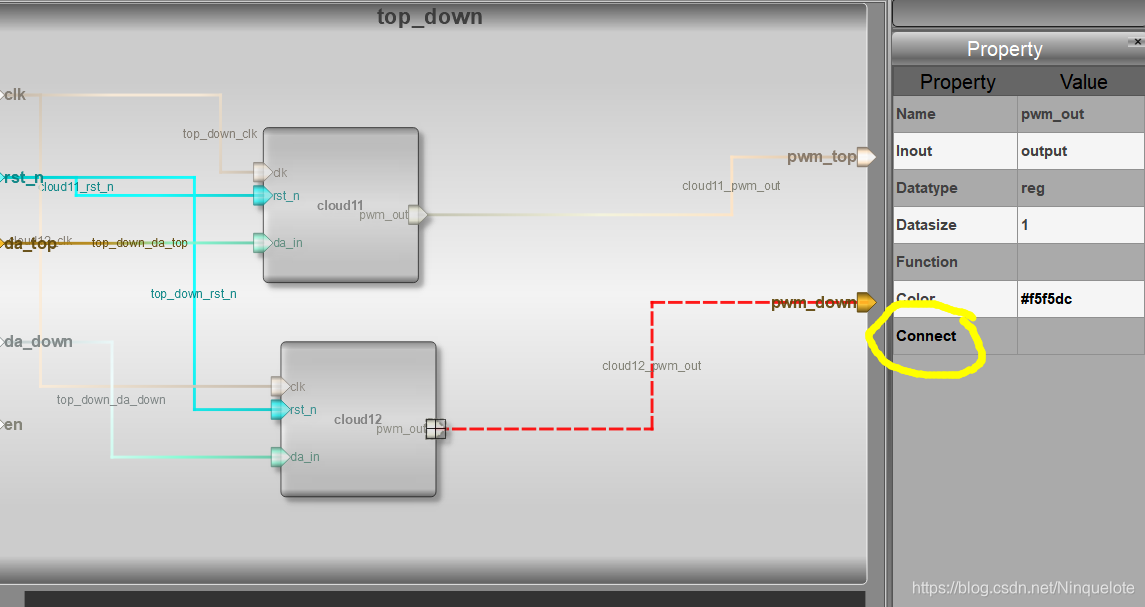

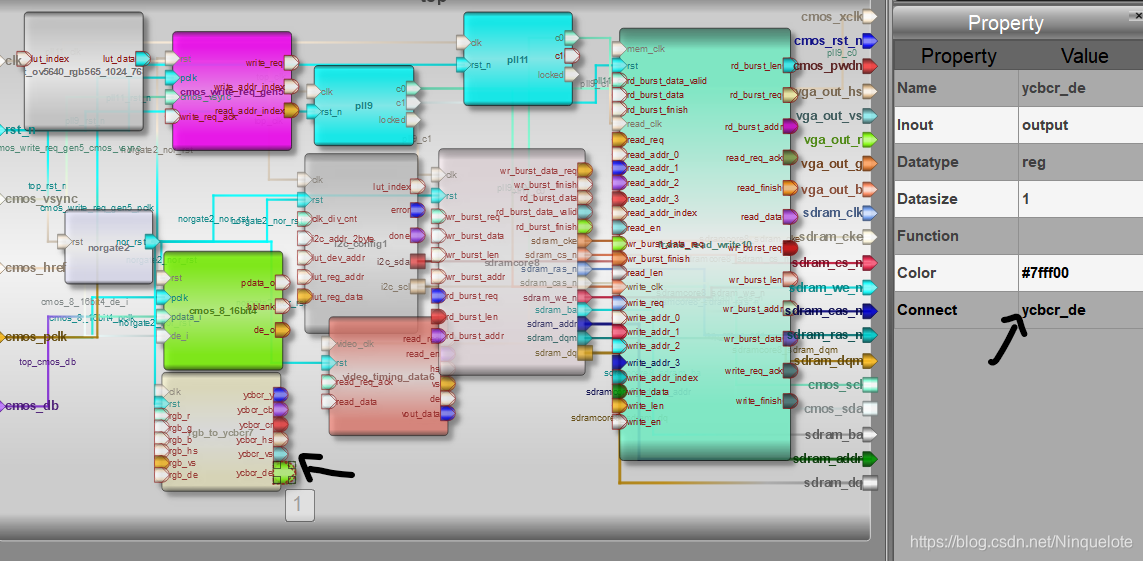

- 检查版本。在一些低一点的EDA版本里,是没有这个操作的,需要在官网下载最新版覆盖。如何检测是否有这个操作,点击robei 顶层模块的管脚,看有断属性里是否有 Connect 这个选项,如果有则可以继续操作;如果没有,需要在官网下载最新版覆盖。

- 如何连接内部信号。将高层模块里的内部信号名称复制,在模块图像界面里,点击端口,粘贴到属性栏的Connect里面,就可以了。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7259

7259

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?