module IO_PAD(input OE, input IN, inout PAD, output OUT);

bufif0(OUT, PAD, OE);

bufif1(PAD, 1'b0, OE);

pullup(PAD);

endmodule对于bufif1、bufif0、notif1、notif0,

-

它们只能有一个数据输出端口、一个数据输入端口和一个控制输入端口,第一个端口是数据输出端口,第二个端口是数据输入端口,第三个端口是控制输入端口。

-

对于bufif1和notif1,当控制等于1时,数据通过;当控制等于0时,输出为z(HiZ)。

-

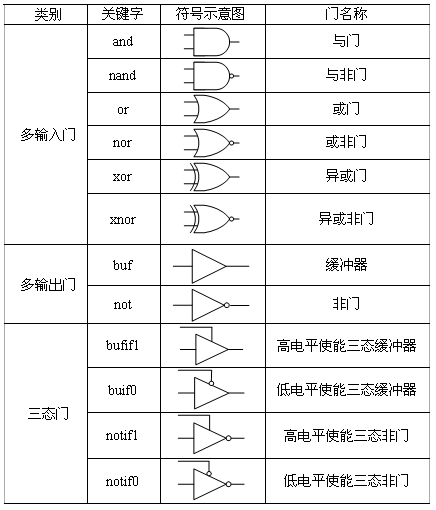

门级建模就是将逻辑电路图用HDL规定的文本语言表示出来,即调用Verilog语言中内置的基本门级元件描述逻辑图中的元件以及元件之间的连接关系。

Verilog语言内置了12个基本门级元件模型,如下表所示。门级元件的输出、输入必须为线网类型的变量。

1.多输入门

and、nand、or、nor、xor和xnor是具有多个输入的逻辑门,它们的共同特点是:只允许有一个输出,但可以有多个输入。and的一般调用格式为:

and A1(out, in1, in2, in3);

其中,调用名A1可以省略。nand、or、nor、xor和xnor的调用格式与and的类似。

2.多输出门

buf、not是具有多个输出的逻辑门,它们的共同特点是:允许有多个输出,但只有一个输入。一般的调用格式为:

buf B1(out1, out2,..., in);

not N1(out1, out2,..., in);

其中,调用名B1、N1可以省略。

3.三态门

bufif1、bufif0、notif1和notif0是三态门元件模型。这些门有一个输出、一个数据输入和一个输入控制。如果输入控制信号无效,则三态门的输出为高阻态z。一般的调用格式为:

bufif1 B1(out, in, ctrl);

bufif0 B0(out, in, ctrl);

notif1 N1(out, in, ctrl);

notif0 N0(out, in, ctrl);

其中,调用名B1、B0、N1和N0可以省略。

对于bufif0和notif0,当控制等于0时,数据通过;当控制等于1时,输出为z(HiZ)。

本文详细介绍了Verilog语言中的bufif1和bufif0三态缓冲器,以及notif1和notif0非缓冲器的工作原理。重点讲解了它们的数据输入输出控制,以及在逻辑设计中的使用。同时,涵盖了门级建模的概念和基本门级元件模型的应用。

本文详细介绍了Verilog语言中的bufif1和bufif0三态缓冲器,以及notif1和notif0非缓冲器的工作原理。重点讲解了它们的数据输入输出控制,以及在逻辑设计中的使用。同时,涵盖了门级建模的概念和基本门级元件模型的应用。

1277

1277

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?