1. Overshoot 和 Undershoot 定义

如何定义过冲与下冲?

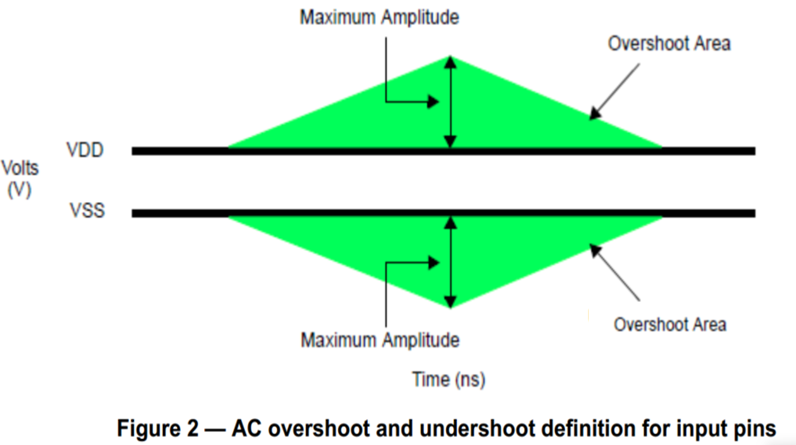

可以形象地解释,过,就是超过,越过了预定电平门限。下,就是不及,没有到达预定的电平门限。古语说,过犹不及,事缓则圆,信号的传输也是如此,电压要在输入端门限所允许的范围内,不能过冲,也不能下冲。如下图所示

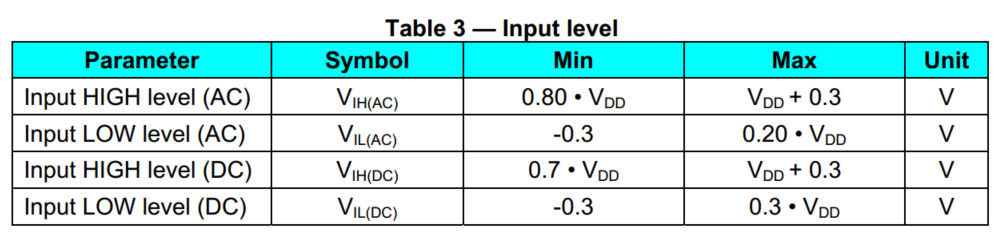

例如,在1V8_HS_LVCMOS标准中,输入可允许的高电平范围是0.8VDD~ VDD+0.3,低电平范围是 -0.3V~0.2VDD

在0→1 动态翻转时,如果信号在到来时某一时刻大于VDD+0.3,这就是100%的(上)过冲,如果信号在上升到门限之后,又掉下来,在某一时刻小于0.8VDD, 这就是100%的下冲。

在1→0 动态翻转时,如果信号在到来时某一时刻小于-0.3V,这就是100%的(下)过冲,如果信号在下降到门限之后,又向上回升,在某一时刻大于0.2VDD, 这就是100%的下冲。

那么,如果信号在VDD~VDD+0.3V范围之内呢?VDD是标准阈值,VDD+0.3是所能允许的最大输入电压,不能越过这个门限。设想如果一个输入电平保持在VDD+0.2V,又该如何评价这个信号质量(过冲)能否接受?对于芯片来讲是否安全呢?需要引入过冲/下冲的另一个评估参数: 过冲/下冲持续时间

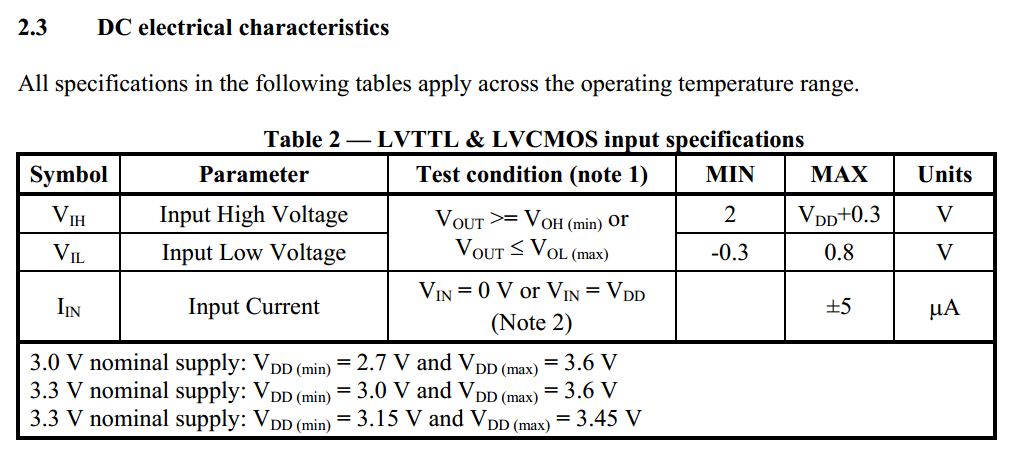

在LVTTL / LVCMOS_3V/3.3V 标准中,对输入的要求如下图所示

2. 过冲与下冲的量化

2.1 过冲与下冲的重定义

对于过冲与下冲,由于加入了持续时间这一参数,我们需要从工程角度出发,对过冲与下冲的定义做更清晰的描述:

过冲:超过了预定门限,这个门限在CMOS电平标准里指VDD,VSS

下冲;不及到预定门限,这个门限在CMOS电平标准里指VDD,VSS

如果信号在某一时刻电平超过了CMOS Maximum Amp (即VDD+0.3V),则该信号质量是完全不可以接受的(极端地设想,好比一个超高峰值电压脉冲/静电),如果信号电平在VDD~VDD+0.3V之间,需要去评估下过冲的持续时间(或者占空比)。

2.2 芯片手册里的过冲与下冲要求

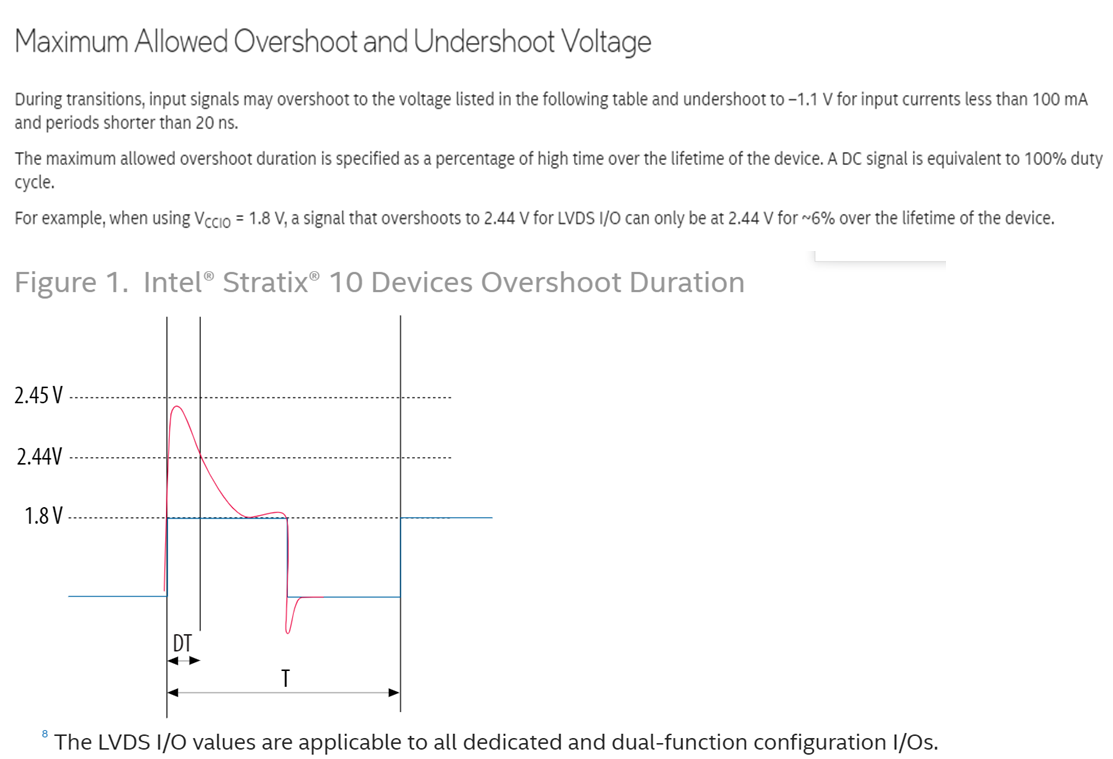

那么,如何评估信号的过冲/下冲的持续时间对于芯片端口来讲是否可接受呢?这就需要看各个芯片厂商的要求,例如,查看Inter Stratix10的芯片手册,对于不同电平的可接受的过冲与下冲Spec,有如下描述

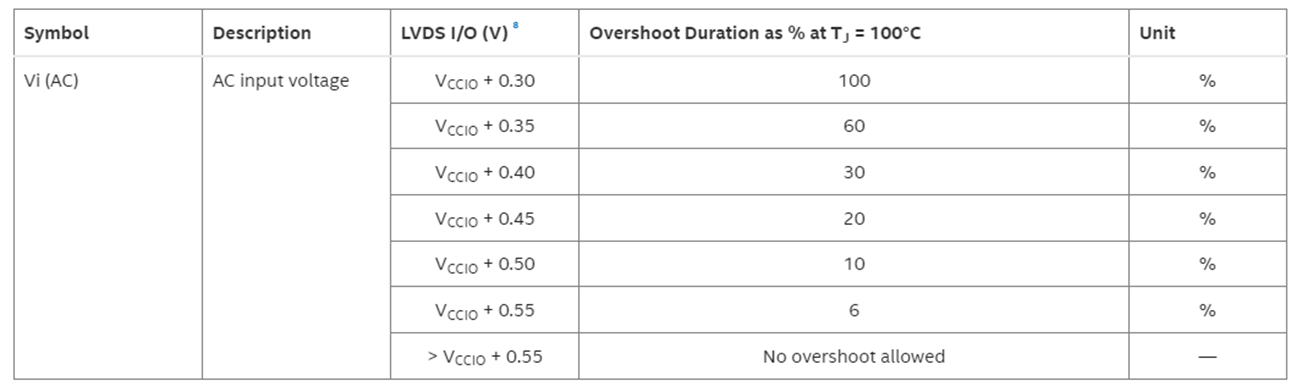

当I/O口电平标准为LVDS时,过冲与下冲的可接受范围:

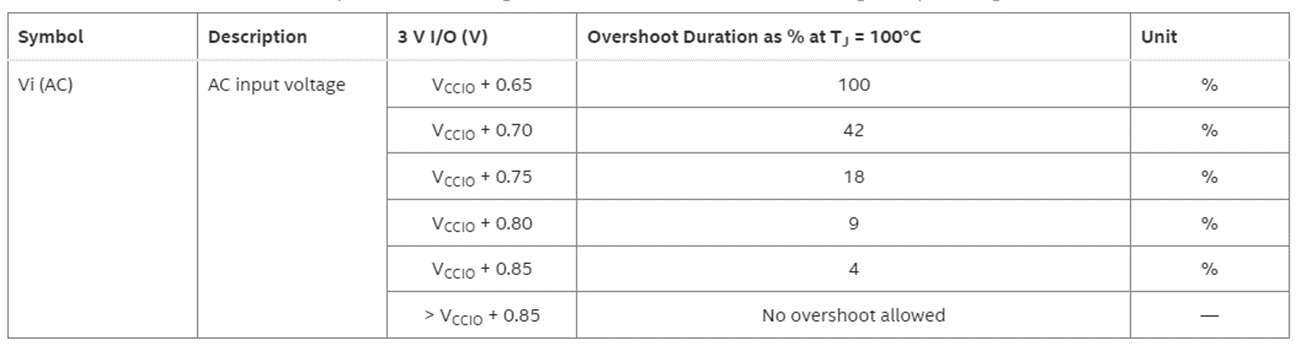

当I/O口电平标准为CMOS 3V时,过冲与下冲的可接受范围:

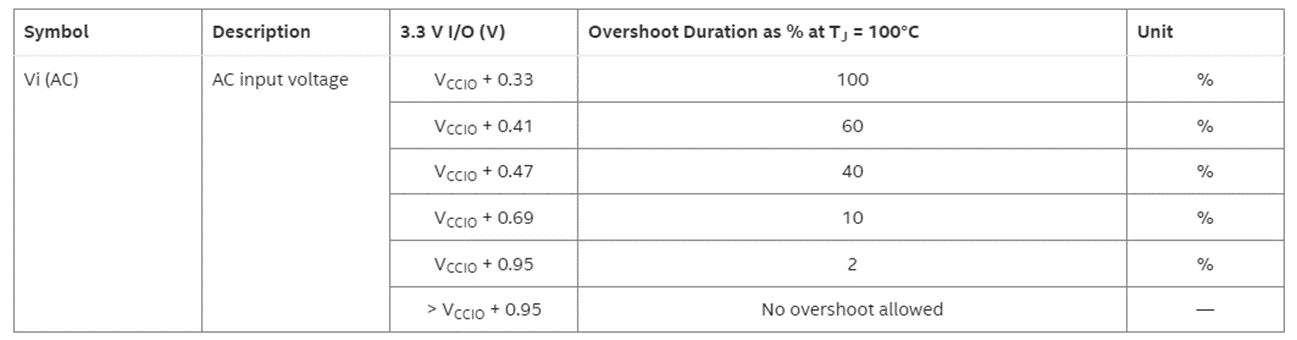

当I/O口电平标准为CMOS 3V3时,过冲与下冲的可接受范围:

2.3 示波器的过冲与下冲测量方法

通过查找Keysight 官网资料,找到了相关信息

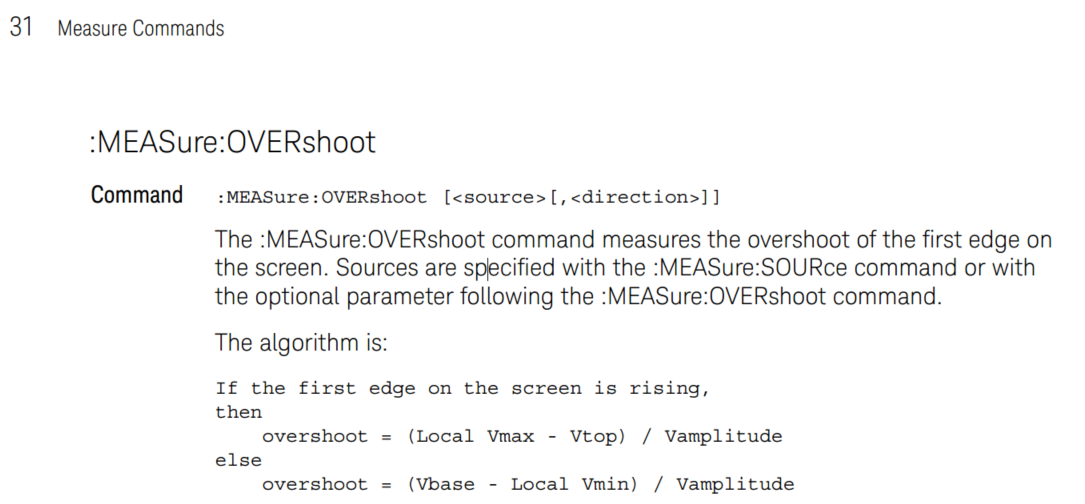

(1)Overshoot 测量方法

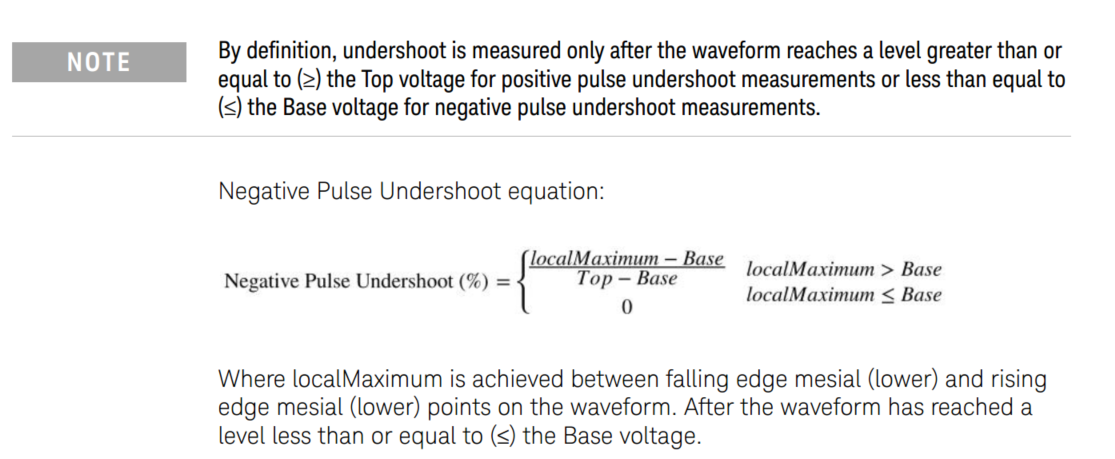

(2)Undershoot 测量方法

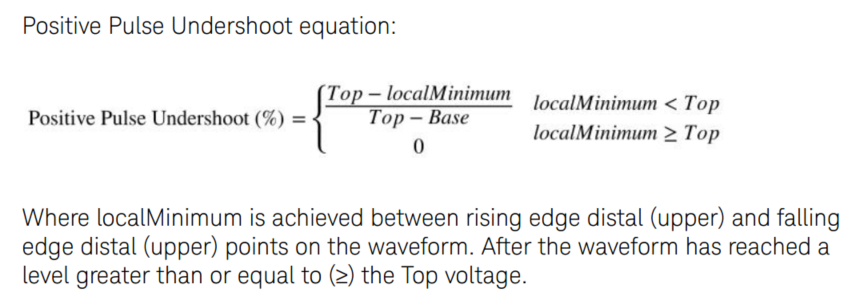

例如,测量一个波形如下图所示,undershoot的计算

Current value= (Top-localMinimum) / (Top-Base)

=(31.907mV-27.7.4mV) / (31.907mV+77.723mV) = 3.83%

从示波器对过冲与下冲的极大值/极小值测量方法可以看出,其与 JEDEC标准或芯片手册的阈值标准并不一致,因此,示波器的过冲与下冲自动测量值measurement value只能作为一种参考,工程师最好直接从波形图上读出过冲与下冲的数值,然后根据持续时间,去评估信号质量。

3. 振铃的定义

Ringing definition is shown in the below picture. Actually, The Ringing of the signal is a continuous overshoot and undershoot of signal voltage, with the voltage amplitude gradually tending to a normal value. 反复的过冲与下冲,就形成了振铃(在测量电源信号时,考量的是纹波,在测量非电源信号,考量的是过冲、下冲与振铃)。

4. 过冲与下冲的评估实例

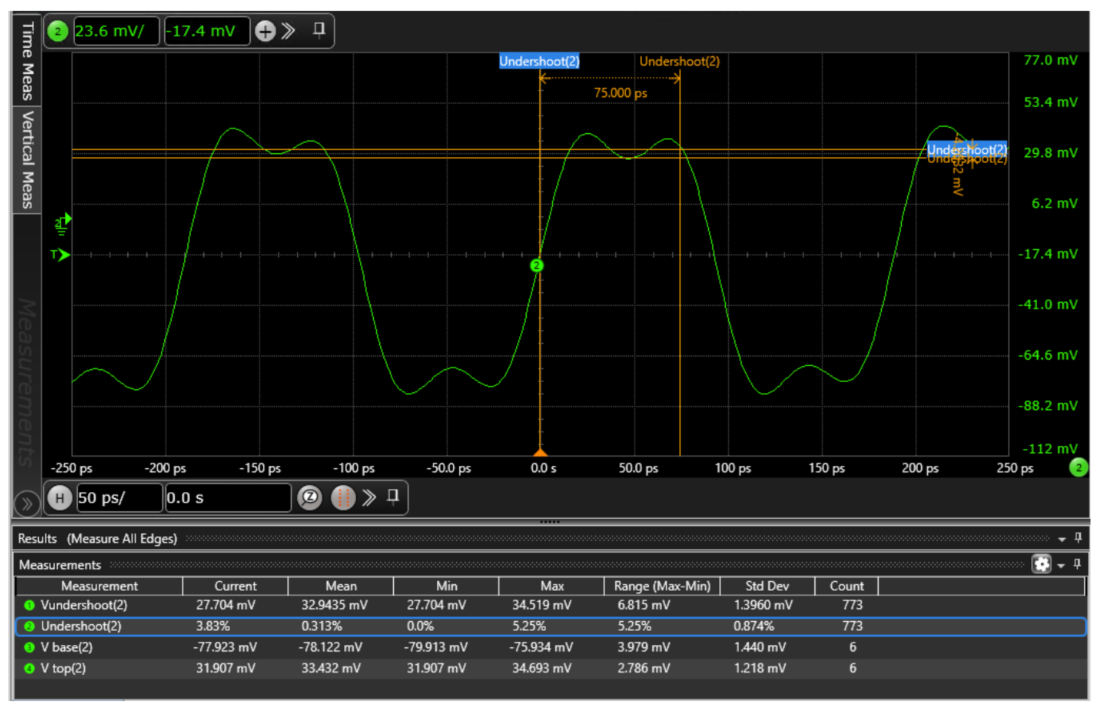

有这样一个实例,测量板级电路上的Jtag Chain的TCK信号,评估其信号质量。

从图中可以看出,信号在上升沿有下冲,在下降沿出现了过冲与下冲,那么这个信号的过冲与下冲能否接受呢?

分析测量值,在上升沿,测量到的Top=3.318V,Max=3.480V, 根据LVCMOS_3.3V电平标准 [2V~ Vdd+0.3], 然后基于图像判断其过过冲的持续时间,这是没有问题的。在下降沿,测量到的Base=-80.52mV, Min=-280mV, 根据LVCMOS_3.3V 电平标准 [-0.3V~ 0.8V],然后基于图像判断其过冲与下冲,也是符合标准的。

5. 参考文献:

- JEDEC LVCMOS Standard

- Keysight Infiniium Oscilloscope

3712

3712

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?