基于CCSDS标准的LDPC码的编码器设计

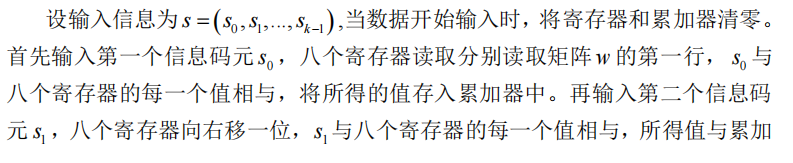

根据生成矩阵的块循环特性,使用准循环编码器来设计 LDPC 码编码器。生成矩阵 G 是由一个单位矩阵 I MK 和一个稠密循环矩阵 W 构成。在编码器设计中,核心是完成信息序列和 W 矩阵乘法即可。

主要的设计思想如下图所示:

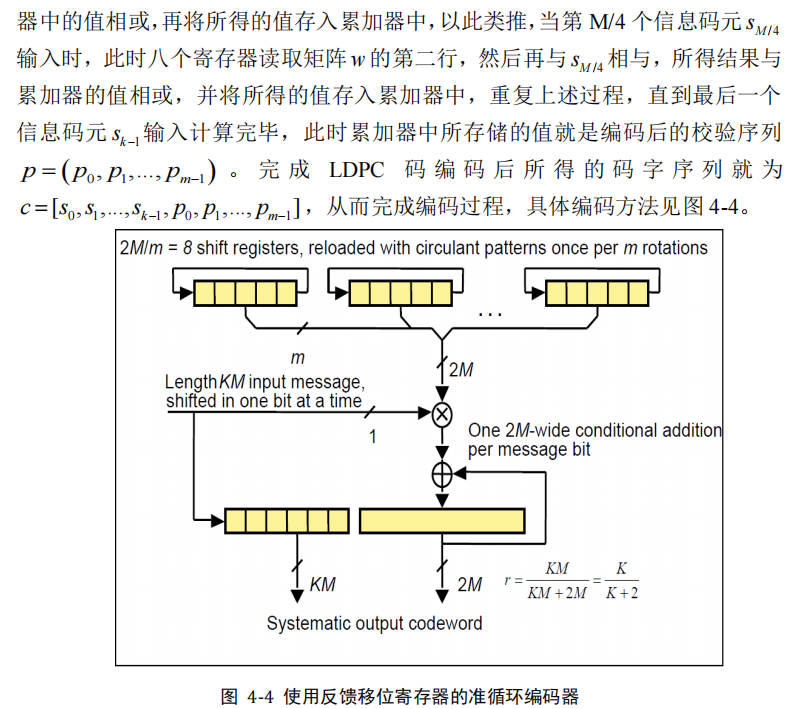

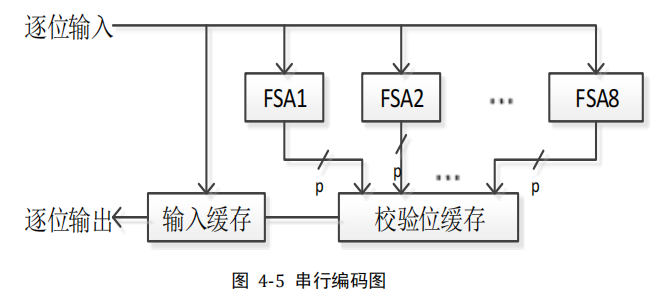

串行编码设计

代码架构如下:

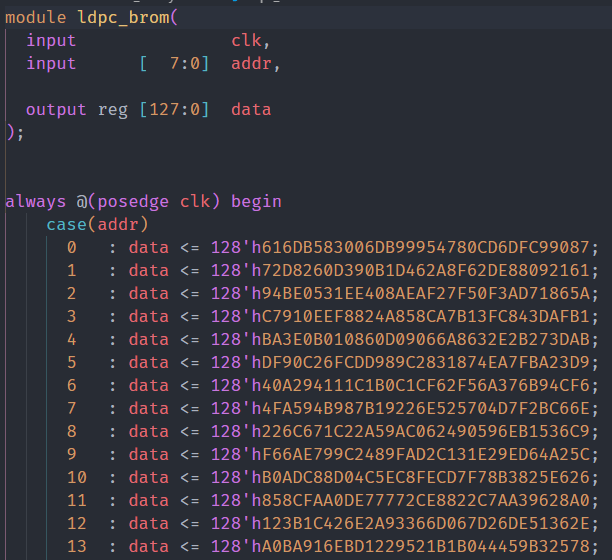

encoder负责编码计算,ldpc_brom负责存储生成矩阵,生成矩阵可通过计算得到,我是将现成的生成矩阵用matlab进行处理后保存出来的,如果有更简便的方式欢迎分享,大概长这个样子

在FPGA中是使用的块循环方法

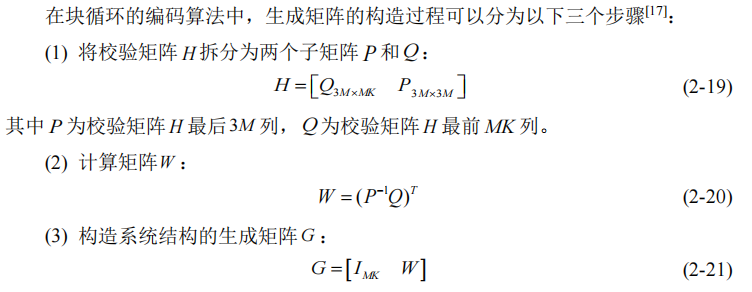

步骤 1: 将校验矩阵 H 拆分为两个子矩阵 P 和 Q: 校验矩阵 H 可以表示为如下形式:

H = [Q{3M × MK} P{3M × 3M}]

其中,P 是校验矩阵 H 的最后 3M 列,Q 是校验矩阵 H 的最前 MK 列。

步骤 2: 计算矩阵 W: 计算矩阵 W 的公式如下:

W = (P^(-1) Q)^T

其中,P^(-1) 表示矩阵 P 的逆矩阵。

步骤 3: 构造系统结构的生成矩阵 G: 生成矩阵 G 可以表示为如下形式:

G = [I_{MK} W]

其中,I_{MK} 是 MK 阶单位矩阵,W 是在步骤 2 中计算得到的矩阵。

计算的流程如下:

将存储信息向量的 mess的最低为 mess[0]送入编码器,判断当前 mess[0]是否为 1,如果为 1 则将 regW32 结果与 regP32 按位做乘法运算,即异或运算,完成一次计算后 mess 整体右移一位,移位后的 mess[0]变成了下一比特信息位,同时 8 个 regW32 循环右移一位,右移一位后的 regW32 存储的数据则变成了生成矩阵循环块的下一行数据,此时移位计数器sh_cnt 加 1;重复计算流程 32 次,即 mess 和 regW32 中所有的元素都遍历后,此时装载次数寄存器 ld_cnt 加 1。

当 sh_cnt 等于 32 且 ld_cnt 不等于 32,进行下一轮 32 次的计算流程。首先仍然是 mess_32 装载 32bit 的信息向量,8 个 regW32 依次装载表 2-5 下一行的 8 个生成多项式,继续计算流程。当转载次数 ld_cnt 等于 32 时,此时已经输入整个 1024bit 信息向量并完成编码。

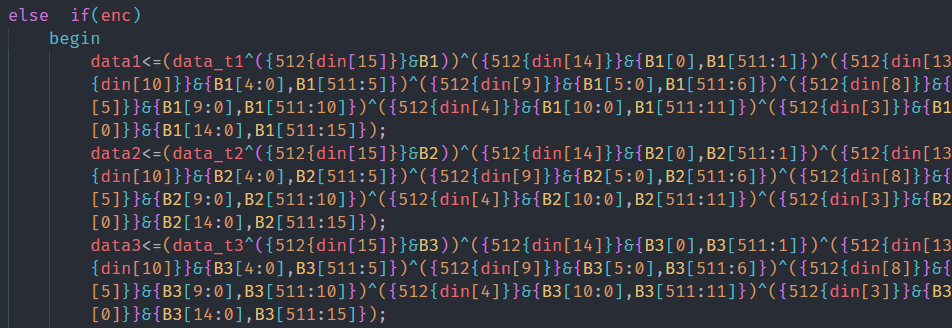

首先初始化一个1* 512的全0矩阵,名为regP512,函数输入了一个字符型参数名为W_B2,其中存储的是16进制的数据,将其转换为2进制之后逐位存放进一个新的1* 512的名为regW512矩阵中。函数还输入了一个参数为S,同样的其中存储的是16进制的数据,将其转换为2进制之后逐位存放进一个新的1* 512的名为mess的矩阵中。之后循环执行512次以下操作:判断mess{1,1}的值是否为1,如果为1则将regP512的值更新为regW512与regP512按位做即异或运算(也就是512次运算),之后将mess矩阵中的数据循环向右移一位,regW512 也循环右移一位。在循环512次之后输出regP512的值。

用verilog实现:

1956

1956

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?