本文由知乎

赵俊军授权转载,知乎主页为https://www.zhihu.com/people/zhao-jun-jun-19

7.4 约束输入路径

本节将介绍输入路径的约束。这里需要注意的一点是,STA无法检查不受约束的路径上的任何时序,因此需要约束所有路径以进行时序分析。在后面的章节中会介绍一些示例,其中一些示例可能并不关心某些逻辑,因而这些输入路径可能可以不用约束。例如,设计人员可能并不在乎一些输入控制信号的时序,因此可能并不需要进行本节中将要介绍的时序检查。但是,本节假定我们要约束全部的输入路径。

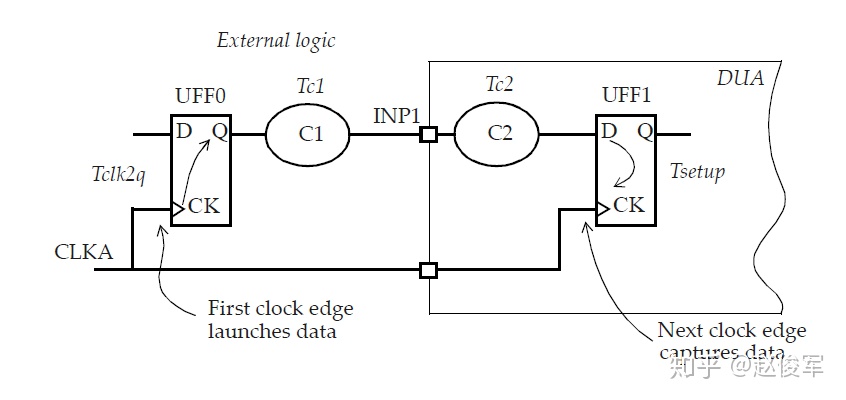

图7-21中为待分析设计(DUA)的输入路径。触发器UFF0在设计的外部,并向设计内部的触发器UFF1提供数据。数据通过输入端口INP1连接两个触发器。

CLKA的时钟定义指定了时钟周期,这是两个触发器UFF0和UFF1之间可用的总时间。外部逻辑所需的时间为Tclk2q(数据发起触发器UFF0的CK至Q延迟)加上Tc1(通过外部组合逻辑的延迟),因此输入引脚INP1上的延迟定义指定了Tclk2q加上Tc1的外部延迟。并且这个外部延迟是相对于一个时钟指定的,在本示例中为时钟CLKA。

以下是输入延迟的约束:

-

set Tclk2q 0.9

-

set Tc1 0.6

-

set_input_delay -clock CLKA -max [ expr Tclk2q + Tc1] [ get_ports INP1]

该约束指定输入端口INP1的外部延迟为1.5ns,且这是相对于时钟CLKA而言的。假设CLKA的时钟周期为2ns,则INP1引脚的逻辑只有500ps(= 2ns-1.5ns)可以在设计内部中传播。此输入延迟定义意味着输入约束为:Tc2加上触发器UFF1的Tsetup必须小于500ps,才可以确保可靠地捕获到触发器UFF0发起的数据。请注意,上述外部延迟值被指定为了最大值(max)。

图7-

图7-

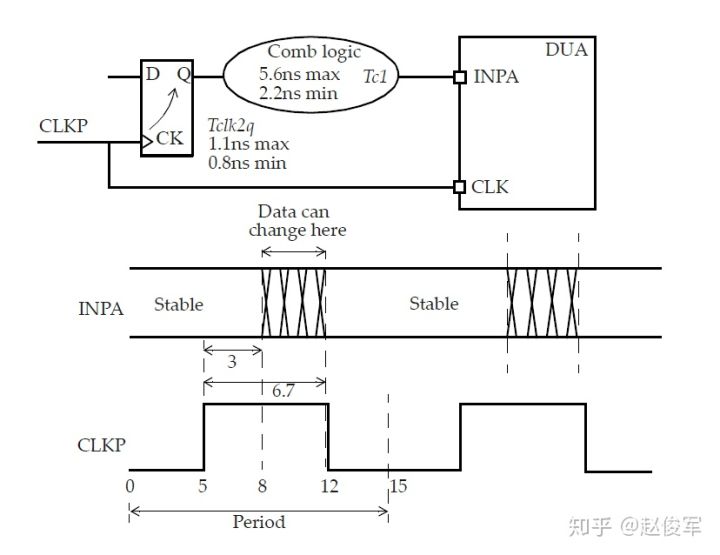

让我们同时考虑最大和最小延迟情况,如图7-22所示。以下是此示例的约束:

-

create_clock -period 15 -waveform {5 12} [ get_ports CLKP]

-

set_input_delay -clock CLKP -max 6.7 [ get_ports INPA]

-

set_input_delay -clock CLKP -min 3.0 [ get_ports INPA]

INPA的最大和最小延迟是从CLKP到IN

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

953

953

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?