1、前言

边沿检测经常用于按键输入检测电路中,按键按下时输入信号 key 变为低电平,按键抬起变为高电平。当输入的信号为理想的高低电平时(不考虑毛刺和抖动),边沿检测就发挥了很重要的作用。

由于输入的信号为一个连续值,我们需要通过时钟进行采样。根据采样定理,采样时钟的频率需要至少为被采信号频率的 2 倍。

设计的边沿检测电路的功能为:检测到 1 个下降沿或上升沿时,对应的下降沿输出信号 edge_pos、edge_neg 分别输出 1 个脉冲(即一个时钟周期的高电平)。下面以下降沿进行分析。

2、具体设计

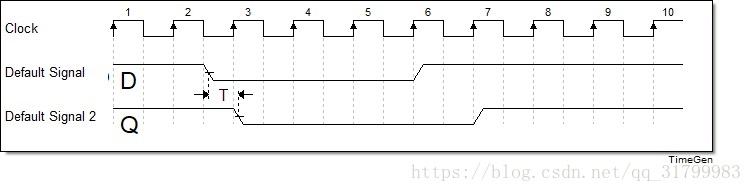

分析:在边沿检测的过程中,通过 1 个寄存器 reg 来寄存上一个时钟沿的输入值 D ,当寄存器输出 Q 与输入 D 的值分别为1、0时,证明检测到下降沿。

如上图所示,在第 2 个时钟周期的低电平期间,D 由高变低,在第 3 个时钟周期的上升沿,Q由高变低。在 D 由高变低的时刻,Q 为 1 ,D 为 0 ,证明检测到下降沿。

存在问题:采用上述方法存在一个缺陷,输入信号为异步输入,当 D 信号由高变低的时刻发生在趋近时钟上升沿附近时,会导致 D 变化的时刻与 Q 变化的时刻的时间间隔 T 很小,导致沿检测输出信号脉冲宽度很窄,系统可能会不稳定。

解决方法:将异步输入转化为同步信号,使用一级寄

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1292

1292

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?