亚稳态:在亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态引时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

解决方法:

- 降低系统时钟

- 用反应更快的 FF

- 引入同步机制,防止亚稳态传播

- 改善时钟质量,用边沿变化快速的时钟信号

关键是器件使用比较好的工艺和时钟周期的裕量要大。

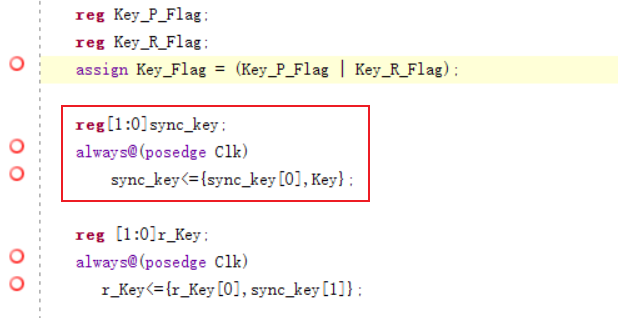

这里我们采用两级寄存器进行解决~

因为亚稳态的存在,一般在写代码的时候用两级寄存器对信号进行同步

reg [1:0]key_sync_reg;

always @(posedge Clk)begin

key_sync_reg[0]<=key;

key_sync_reg[1]<=key_sync_reg[0];

end

reg reg_key_pre;

always@(posedge Clk)begin

reg_key_pre<=key_sync_reg[1];

end

assign pedge=!reg_key_pre&&key_sync_reg[1];

更加简化的写法~

reg [2:0]key_sync_reg;

always@(posedge Clk)

reg_key_pre<={key_sync_reg[1:0],key};

assign pedge=key_sync_reg[2:1]==2'b01;

对按键消抖模块修改~添加一层同步信号

1551

1551

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?