1、概述

在 VIVADO 工具提供了关于时钟的 IP 核,其内部调用了 PLL 或 MMCM 原语,通过设置 IP 核配置界面的参数可以获得想要的频率时钟。本文以此展开,对如何根据输入时钟的改变动态配置输出时钟作出讲解,并举例进行详细阐述。

2、使用场景说明

例,一个频率为 450MHz 的差分时钟进入 FPGA 内部,经过 Clocking Wizard IP 核后,分别输出了 180MHz、50MHz、450MHz、90MHz 四个时钟。在此基础上,该输入时钟会在上位机的控制下变为 600MHz,同时需要经过 IP 核后输出 200MHz、50MHz、600MHz、200MHz 四个时钟。

当输入时钟为 450MHz 时设置的输入分频比、VCO 分频比、各输出时钟分频比等参数与输入时钟为 600MHz 时有所改变,这就需要上位机告知我们当前输入的时钟频率,并以此进行相关参数的重配置。

3、IP 核设置

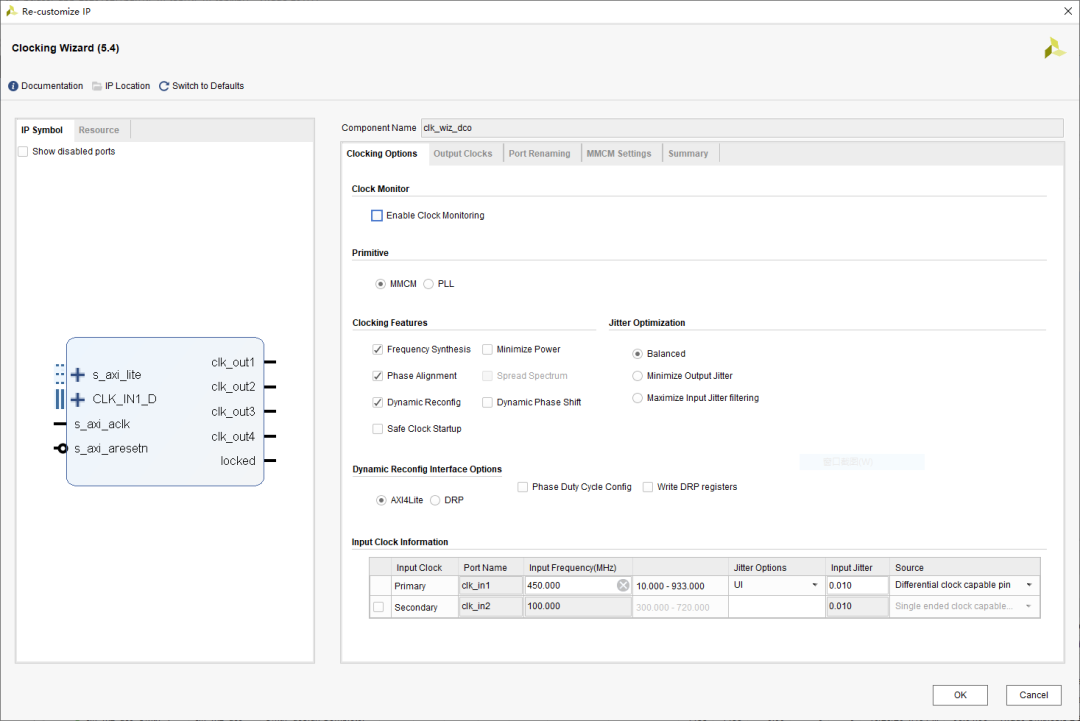

打开 IP 核,在第一页勾选 AXI4Lite,并设置输入差分时钟频率 450MHz。

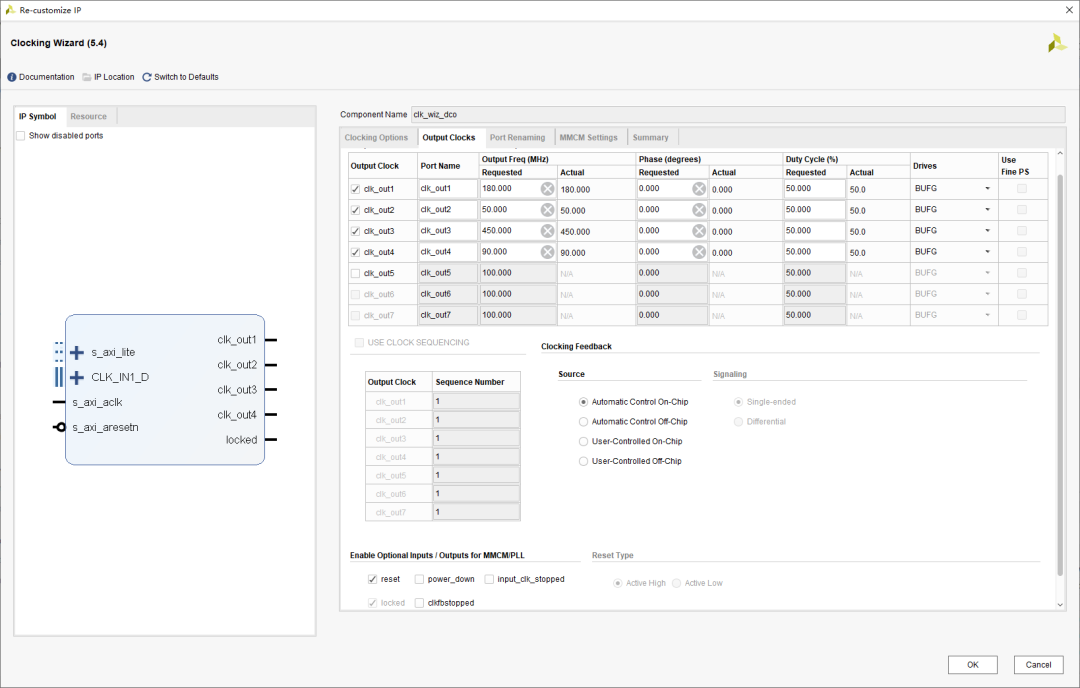

在第二页中设置如下频率:

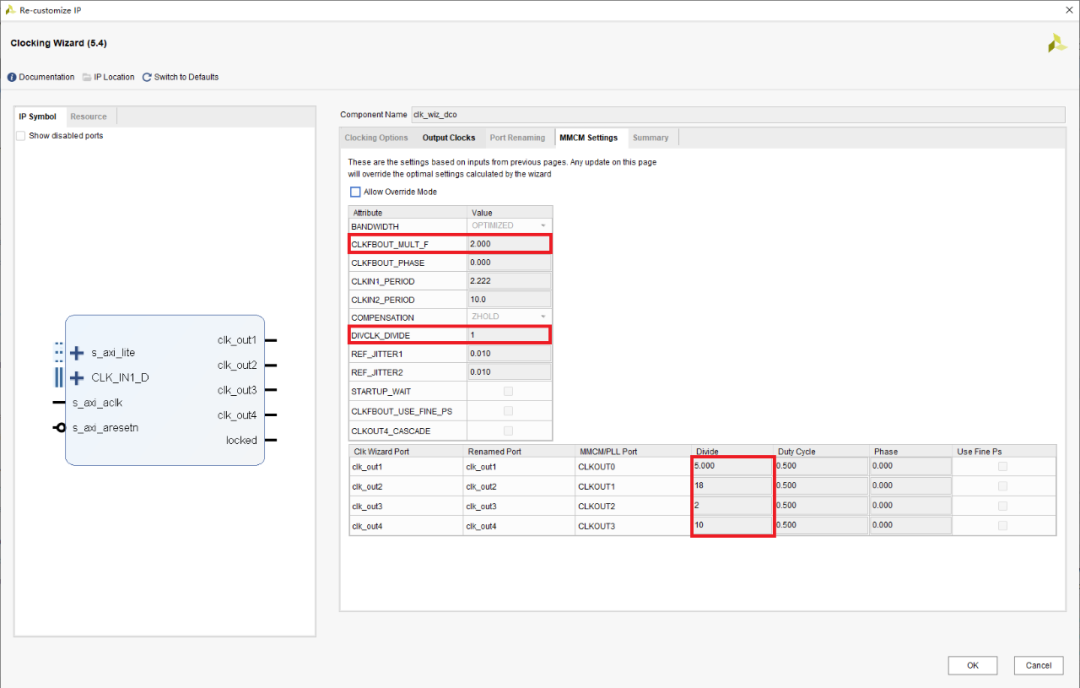

在第四页中可以看到分频及倍频参数如下:

其它保持默认设置即可。

4、AXI4-Lite 接口

在上一节的 IP 核设置中勾选了 AXI4Lite,该总线用于配置 IP 核的内部寄存器,包括 CLKFBOUT_MULT_F、DIVCLK_DIVIDE、clkout1~clkout4 对应的 Divide 参数。因此先了解 AXI4-Lite 接口,才能实现动态配置时钟的功能。

信号接口如下:

| 写地址总线 | |

| s_axi_aclk | AXI4-lite 时钟 |

| s_axi_aresetn | 异步复位,低有效 |

| s_axi_awaddr[10:0] | 写地址 |

| s_axi_awvalid | 写有效 |

| s_axi_awready | 写 |

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7210

7210

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?