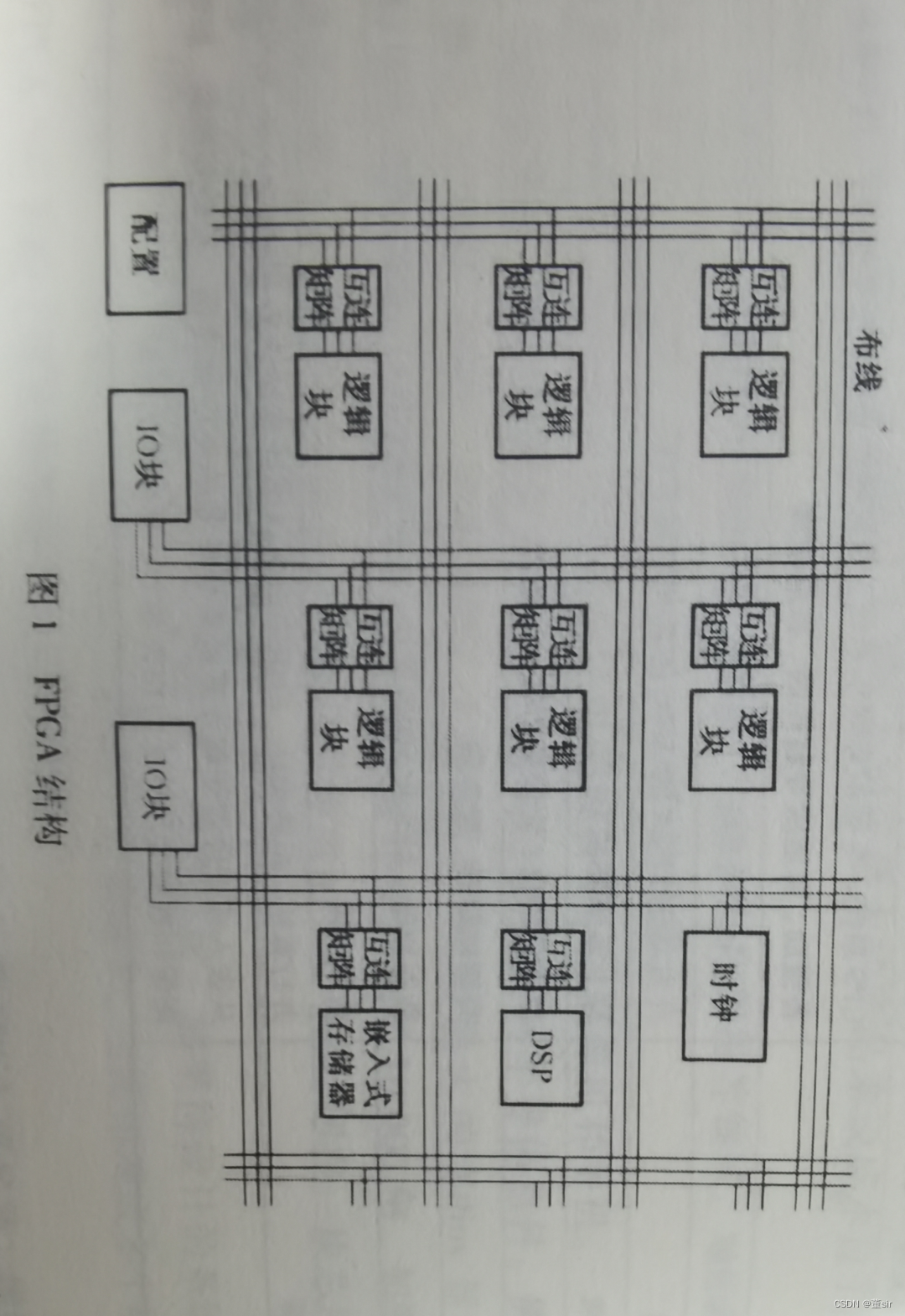

设计能够成功的关键是要对FPGA结构、功能、可用资源和局限性有一个很好的了解。本则将以Xilinx Virtex-6系列为例,简要概述现代FPGA结构。主要结构如图1所示,包括逻辑块、I0块、互连矩阵、时钟资源、嵌人式存储器、布线和配置逻辑。

许多高端FPGA还包括复杂的功能模块,如存储器控制器.高速串行/解串收发器、集成的PCI Express 接口和以太网MAC块。

当绘制出逻辑块和其他资源之间的布线后,密集的线路看起来与织布( fabric)类似。因此,通常将逻辑和布线资源形象地称为FPGA的“资源”框架。

一 逻辑块

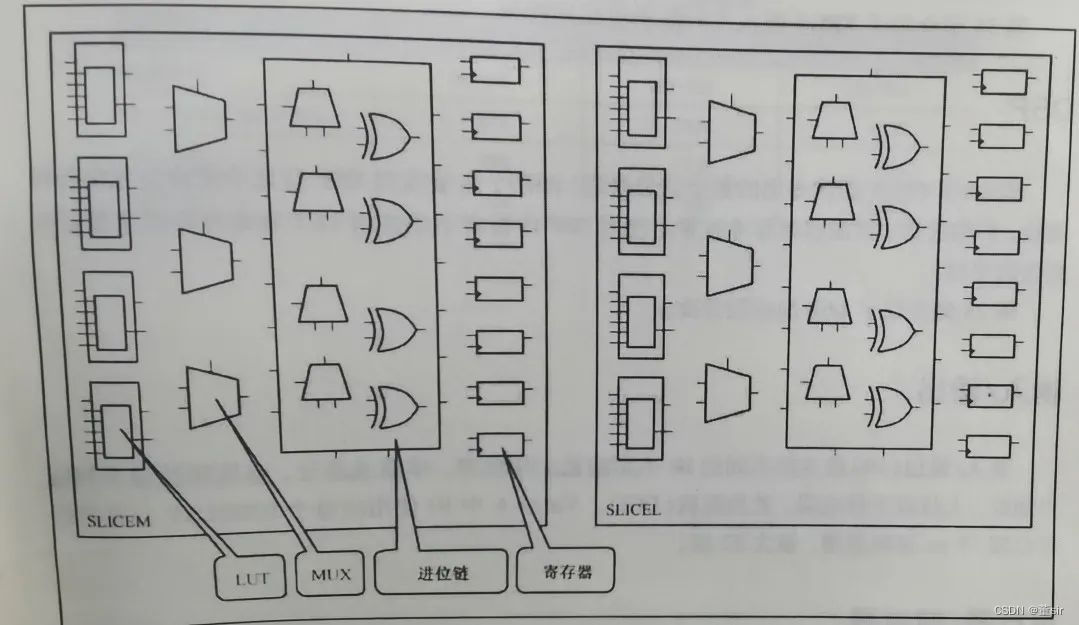

逻辑块是指实现各种逻辑功能的电路。在Xilinx FPGA中,逻辑块被称为逻辑片(Slice)。Virtex-6 FPGA系列的一个逻辑片包含4个查找表(LUT)、8个寄存器、1个进位链和多个数据选择器。Virtex-6 FPGA中逻辑片的主要组成如图2所示。

图2 FPGA结构

LUT、寄存器、数据选择器( MUX)和进位链之间的连接可以形成不同的逻辑电路。

有两种不同的逻辑片类型: SLICEM和SLICEL。SLICEM有多功能的LUT.可以配置为移位寄存器型LUT(SRL),或者配置为64位或32位的只读或随机存取存储器。

逻辑片中的每个寄存器可以配置为锁存器使用。

二 时钟资源

每个Virtex-6 FPGA提供高度可配置的混合模式时钟管理器(MMCM),用于频率合成器和移相。提供给FPGA中不同同步单元的时钟,使用专用的低偏移和低延迟时钟布线资源。时钟线由全局时钟缓冲器驱动,这样允许无毛刺时钟复用和时钟使能。

持续关注,后续会提供更详细的Xilinx FPGA 时钟资源介绍。

三 嵌入式存储器

Xilinx FPGA的嵌入式存储器有两种类型:专用Block RAM( BRAM)和可配置为分布式RAM的LUT。

Virtex-6 BRAM可以存储6 k数据位,可配置为单端口或双端口RAM.其他配置选项包括数据宽度(最大36位)、存储深度(最大32 K单元)和检纠错。

持续关注,后续介绍了FPGA嵌人式存储器的应用情况。

四 DSP

Vitex-6 FPGA提供专用的数字信号处理(DSP),主要实现DSP应用中需要使用的各种功能,如乘法器、累加器和算术运算。使用DSP内核而不是通用LUT和寄存器的主要好处是性能更好。

持续关注,后续会介绍SDP的应用情况

五 输入/输出

输入/输出( IO)块支持不同的IO引脚配置: IO标准、单端或差分、电压转换速率和输出强度、上拉或下拉电阻、数控阻抗(DCI)。Virtex-6 中IO使用的每个IODELAY元件延迟可以按78 ps逐级递增,最大32级。

六 串行器/解串器

大多数的Virtex-6 FPGA上包含专用的收发器模块,实现串行器/解串器(SerDes)功能。收发器可以工作的数据传输速率在155 Mps到11.18 Ghps之间,由具体配置情况决定。

七 布线资源

FPGA布线资源提供逻辑块、IO块、嵌入式存储器、DSP和其他模块之间的可编程连接。布线资源规划为水平和垂直网格。一种特殊的互连模块用做可配置的开关单元,连接逻辑块、I0块、DSP、水平和垂直布线的其他模块。可惜的是,Xilinx 公司没有提供其性能特点、实现细节和布线资源数量方面的有关文档。通过定时(时序)分析报告,可以得到一此布线性能的信息。FPGA 编辑器工具可以用来收集关于布线数量和结构的信息。

八 FPGA配置

大多数现代FPGA基于SRAM,包括Xilix Spartan 和Virtex系列。FPGA上电后重新配置,从外部非易失性存储器(NVM)中读数据,通过配置控制器处理,并加载到内部配置SRAM中。

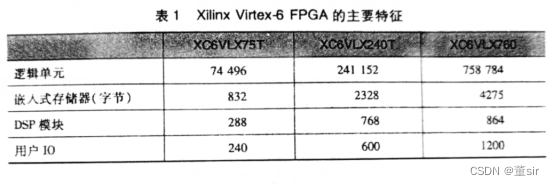

表1给出了Xilinx Virtex-6 FPGA中最小的、中间的和最大的3个器件的主要特征。

2349

2349

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?