最近一直在学习FPGA时序约束的内容,看了很多的教程。所以想用这篇去整理一下思路。好让自己能够坚持下去。

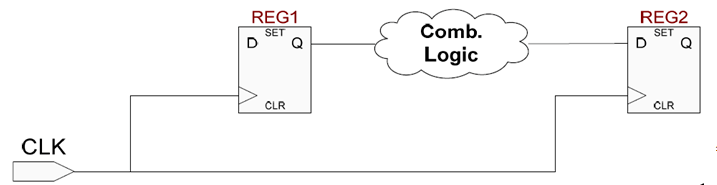

学习时序分析都离不开一个节点对节点的模型,如下图;

这个模型是FPGA时序分析的基础模型,描述数据在两个寄存器间传输的一般模式,想要真正的理解这个模型还需要知道以下几个概念:

启动沿:数据被launch的时钟边沿,在每一个时钟边沿后产生一个新的数据。

锁存沿:数据被latch的时钟边沿,也就是说,每一个锁存沿,都会有一个新的数据被保存。

整个模型的功能就是从Signal in接受数据,在经过时序逻辑和组合逻辑的处理将数据从Signal out发送。从结构可以看出,第一个D触发器reg1的功能就是将Signal in的数据采样,并发送给下一级的逻辑处理。所以我们管第一个触发器的时钟clock1的上升沿叫做启动沿。而第二个触发器reg2的功能就是将前级处理过后的信号所存给Signal。所以我们管第二个触发器的时钟clock2的上升沿叫做锁存沿。

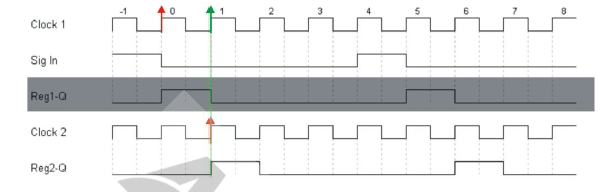

在知道启动沿和锁存沿后,我们就可以得出在理想情况下(没有物理延迟时)的时序如下:

红色箭头就是启动沿所对应的时刻,绿色箭头就是锁存沿所对应的时刻。我们在分析这个模型的建立时间和保持时间时,分析的时钟是以锁存沿为准。用锁存沿去分析建立时间和保持时间。

那么理想状态下,clock1的时钟打一拍reg1-Q 数据有效,clock1在打下一拍reg1-Q数据发生改变。这段时间就是信号的建立时间。在理想状态下的建立时间为clock1的周期。在clock2上升沿时,在reg1-Q信号线的数据被锁存。在理想状态下的保持时间就是0。

在非理想状态下,这个模型受到物理延迟的影响。在理想状态下,数据的建立时间和到达时间都为0。在启动沿(clock1)采样后reg1-Q上数据到达reg2-D端口。而在非理想状态下,这条路径要经过延时。

数据建立时间

正如上图所示,在计算数据到达时间时,一般都会存在3个延时:

-

Tclk1:时钟信号从起点到达启动寄存器的相应clk端口所耗的时间。

-

Tco:启动寄存器内部延时。

-

Tdata:数据从上级寄存器输出Q到下级寄存器的数据输入D之间的延时。

数据到达时间

通过上面的两幅图我们可以知道我们模型中存在的延迟。

我刚才说了,这个模型的建立时间和保持时间都是以锁存沿为准。记住这个,我就可以分析下一个概念余量(slack)。

理想状态下,我们的建立时间如下图所示;

Tus表示了锁存方的寄存器在读取数据之前所需要的最小准备时间,图中数据的建立时间是10ns,假设Tus是2ns。那么我们的建立时间余量就等于 10ns - Tus = 8ns。

假设把Tus调大至3ns ,锁存沿从原本10ns的位置返回7ns的位置。建立余量也从原本的8ns的再降至7ns,不过建立余量还是正值。换言之,只要建立余量还是正值,寄存器2读取reg1-Q的数据也是没有问题的。

以上都是在理想状态下

如果同源时钟信号由于路径的不同而出现时钟偏移(skew)

上图中clock1没有变化,换之clock2位移-36度,即clock2比clock1提早1ns。clock2位移-36度就表示建立变为原来的9/10.(此例子中10ns变为9ns)。

分析完建立时间保持时间同理

结合传输路径延迟如下图

实际的建立时间余量就为图中绿色部分(Setup Slack)。

实际的保持时间余量就为图中绿色部分(Hold Slack)。

1640

1640

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?