组合逻辑

- 组合逻辑电路概述

组合逻辑的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原本的状态无关,逻辑中不牵涉跳变沿信号的处理,组合逻辑的verilog描述方式有两种:

(1):always @(电平敏感信号列表)

always模块的敏感列表为所有判断条件信号和输入信号,但一定要注意敏感列表的完整性。在always 模块中可以使用if、case 和for 等各种RTL 关键字结构。由于赋值语句有阻塞赋值和非阻塞赋值两类,建议读者使用阻塞赋值语句“=”。always 模块中的信号必须定义为reg 型,不过最终的实现结果中并没有寄存器。这是由于在组合逻辑电路描述中,将信号定义为reg型,只是为了满足语法要求。

(2):assign描述的赋值语句。

信号只能被定义程wire类型。

- 组合逻辑电路分析方法

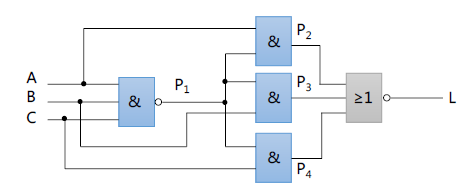

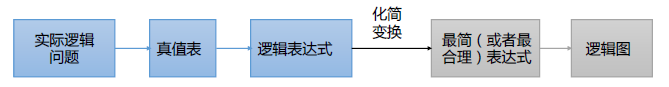

上图的组合逻辑电路是由许多门电路组合而成。我们可以依次写出各个门极电路的逻辑表达式。

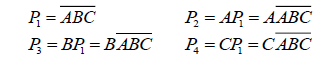

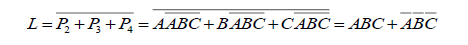

最终我们可以得出:(用公式法或卡诺图法去逻辑表达式的化简)

根据逻辑表达式我们可以得到真值表:

我们可以从真值表中看出输入与输出之间的关系。据此分析出电路的功能。

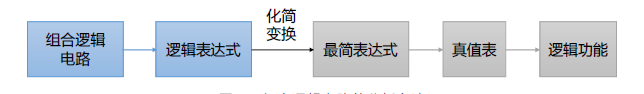

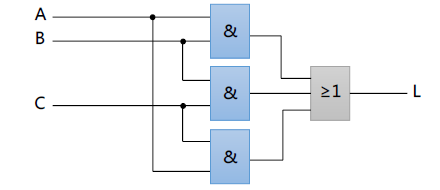

经过前面的电路分析,我们可以知道组合逻辑电路的分析方法如下图:

- 组合逻辑电路设计方法

设计方法是对分析方法的反向,我们根据功能逻辑列出真值表简化成逻辑表达式。最后得到需求功能的门电路。

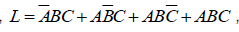

将L = 1 的结果分别取出相或得到逻辑表达式:

简化逻辑表达式

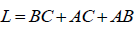

根据最后的逻辑表达式,得到逻辑图:

组合逻辑的设计方法是对分析方法的反向:

-

组合逻辑的竞争与冒险

我们在分析组合电路时,竞争与冒险是我们遇到的一大问题,根据其产生的原因的不同,我们又可以分成逻辑竞争,逻辑冒险,功能竞争和功能冒险。(1)冒险产生的原因

我们在分析门电路时,总是把门电路看成理想门电路。也就是说,这个电路是没有延迟时间的。但是在实际的电路中,输入信号在通过每一个门电路后输出,它总是有延迟时间的,这就叫做门电路的传输时间或者延迟时间。

竞争:在一个组合电路中,当一个变量经过两条以上的路径到达输入端的时候,由于每条路径的延迟时间不同,到达终点的时间也不同。这一现象就称为竞争。

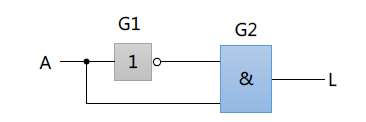

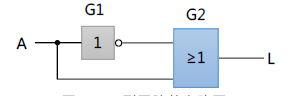

通过上图的逻辑电路可以看出,输入变量A一端是连到了G1门上,延迟一端时间后才能到达G2的输入端。因此,A信号是经过两个不同的路径到达G2门的。由于经过两条不同的路径,而且每条路径上的延迟是不一样的。那么到达G2门的两个信号不会同时到达。在G2的输入端存在竞争现象。

冒险:冒险就是在具有竞争现象的组合电路中,当某个变量发生变化时,真值表所描述的关系中出现破坏,在输出端出现了一个不应该有的尖脉冲。这种现象叫做冒险。

(2)“1”型冒险与“0”型冒险

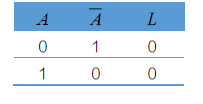

在理想的状态下,上述的逻辑电路的真值表为:

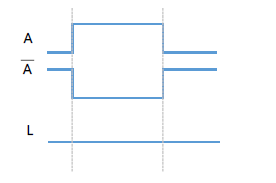

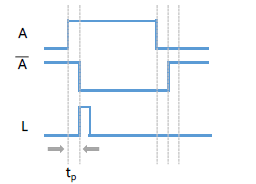

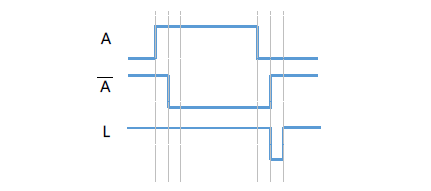

L的值恒为0,这是一个理想的状态的电路。但是在实际的电路中每一个没都是有延迟时间的。把延迟时间记为tp,则电路实际的波形为:

在实际的波形图中,出现这种L等于1的波形,相当于在电路中产生了一个尖脉冲,是不符合我们的逻辑要求的。我们把这种错误的逻辑现象称为逻辑冒险,又因为产生的是一个尖脉冲,所以我们通常称这种逻辑冒险为"1型冒险”。

对于如下的电路:

原理同上,G2门的输入信号到达的时间存在延迟:

同样产生了一个错误的波形。因为是产生了一个负的尖脉冲,所以称这种冒险为“0”型冒险。

ps:上述的例子中,他们的他们的输入变量都只有一个,当多个变量经过两条以上的路径到达输入端口时,同样会产生功能竞争与功能冒险。

在and运算中产生“1”冒险,在or关系中产生“0”冒险。

(3)逻辑冒险的识别与消除

代数法:代数法就是根据电路的逻辑表达式,将其中某些变量取值1或0时,如果表达式最后简化成and逻辑,则电路中存在“1”型冒险。如果表达式最后简化成了or逻辑,则电路中存在“0”型冒险。

卡诺图法:该方法就是根据逻辑表达式画出去对应的卡诺图,根据卡诺图的变化判断冒险存在。

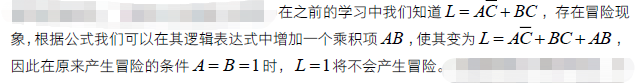

逻辑冒险的消除可以通过电路的重新设计来消除,若在函数表达式中增加冗余项(相当于在卡诺图中添加多余的卡诺圈),既不改变电路的逻辑功能,又可以消除逻辑冒险。缺点是增加了电路结构的复杂性。

消除逻辑冒险的方法不仅仅只有一种,我们还可以通过增加选通信号或增加滤波电容的方法来消除逻辑冒险。

(4)功能冒险的识别与消除

对于功能冒险的识别我们通常采用卡诺图来进行判别。

从上述的描述可知,若电路具有下列条件,则其输出可能产生功能冒险:- 有两个以上变量同时发生变化(如果仅有一个输入变量发生变化,则无功能冒险)

- 变化前后,输出稳态值保持不变

- 在由n(n >= 2)个变量发生变化的2的n次方格中,既要有0,又要有1:(如果对应2的n次个变量的取值组合的输出值全为0或1,电路是不会产生功能冒险的)

功能冒险是由输入的n个变量同时变化时,他们的实际变化在时间上有先有后引起。因此改变电路的逻辑设计并不能消除功能冒险。对待功能冒险的常用方法是增加选通信号或者加输出滤波电容的方法。

时序逻辑

- 时序逻辑电路概述

组合逻辑电路是没有记忆功能的,任何时候的状态只与该时刻输入信号的逻辑状态有关。而时序逻辑是有记忆功能的。在任何时候的输出,不仅与该时的输入信号有关,而且与该时刻以前的状态有关。

从图中可以看出,一个完整的时序电路,是由两部分构成的。一部分是组合电路,另一部分是存储电路。常用的存储电路主要有两类,一类是锁存器,而另一种是触发器(采用电平触发方式的是锁存器、采用边沿触发方式的叫做触发器)

- 锁存器

(1)RS锁存器

锁存器是数字电路中一种基本的具有记忆功能的逻辑元件。锁存器对脉冲电平敏感,它只在输入脉冲的高电平(或低电平)期间对输入信号敏感并改变其状态。下图是RS锁存器的电路图,它是一种基本的锁存器类型。是构成其他所有复杂锁存器和触发器的基础。

RS锁存器它能够将电路的状态锁住,也就是说下一刻,锁存器的置位端或者复位端的激励信号消失(置位、复位全为0),锁存器仍然能够保持之前的状态工作。

RS锁存器的禁止置位信号和复位信号同时为1的状态发生,这样锁存器会进入一种错乱状态。

上述的RS锁存器是用或非门电路完成的,RS锁存器也可以用与非门完成。

与上一种锁存器不同的是,用与非门构成的锁存器是低电平有效的。

(2)门控RS锁存器

在实际工作中,我们更加希望能有一个信号去控制锁存器的状态,门口锁存器就是在RS锁存器前加上一个控制端。

(3)D锁存器

D锁存器就是能将输入端单路数据D出入到锁存器电路中的电路。

ps:以上的锁存器都有一个缺点,就是会产生空翻现象。以D锁存器为例

我们把这四条线内的翻转叫做空翻。空翻是一种有害的现象。它使得时序电路不按照时钟的节拍工作,造成系统误动作。

- 触发器

由于锁存器在空翻现象,所以人们对锁存器进行了修改。发明了触发器。

触发器也是数字电路中的一种具有记忆功能的逻辑元件。触发器对脉冲边沿敏感的存储单元电路。它只在触发脉冲的上升沿(或下降沿)瞬间改变其状态。在数字电路中也可以记录二进制数字信号“0”,“1”。

(1)D触发器

D锁存器与D触发器时序对比

- 时序逻辑电路设计方法

时序逻辑分为同步时序电路和异步时序电路两大类,在同步时序电路中,所有的存储单元的状态是在同一的时钟控制下完成的。而异步时序电路,各个存储单元状态的改变不是同步完成的。时钟脉冲只控制部分存储电路,其他的则靠输入信号或时序内部信号控制。(设计时以同步时序为主)

在时序电路中,我们根据输出信号的特点,将其分类为摩尔型和米里型电路。

- 摩尔型电路的分析

- 米里型电路的分析

7220

7220

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?