组合逻辑

在FPGA中,输出是由输入信号实时的状态决定的,也就是说,当我们的输入信号发生改变,输出信号立马就发生改变,这种逻辑就被称之为组合逻辑,这种很容易理解,我们可以带着代码看:

assign a = b; //对于这种,就是属于组合逻辑,a的状态完全有此时的b决定,当b改变的瞬间,a也随之改变。

always @(*) begin

a <= b; //很多人可能刚刚开始学习FPGA的时候,认为这种always块是属于时序逻辑,不,这种也属于组合逻辑,因为决定a的值的因素是b的同时,always块也是由b驱动,当b变化时,驱动always块,a也同时发生变化,所以这个也是a是实时跟随着b变化而变化,所以也属于组合逻辑。

end

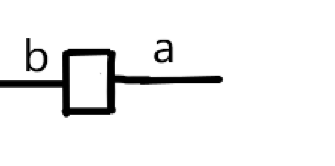

此时上述逻辑图形化。

时序逻辑

还有种电路就是由某一种信号(这个信号可以是时钟信号,大多数情况下我们使用的是时钟信号和复位信号共同作用)驱动寄存器来锁定输入信号的值,使得输出信号不能实时跟随输入信号改变。(这儿可能没有太理解。还有就是时序逻辑可以包含组合逻辑,但是组合逻辑不能包含时序逻辑。)

详细的说就是输入信号并不直接作用于输出信号,而是输入到一个寄存器,然后由时钟信号的上升沿或者下降沿(其他信号也可以,这儿以时钟信号举例)来驱动寄存器,寄存器输出值输入给输出信号。

这样多话,当时钟信号没有到来之前,寄存器已经锁定了上次时钟沿时输入的值,此时无论输入值如何改变,都不会影响到输出值。

我们接下来用代码来体现:

always @(posedge Clk) begin //这是一个又时钟上升沿驱动的时序逻辑

a <= b; //此时a的值虽然是由b决定,但是这个always块的驱动并不是b信号的变化,而是由时钟信号的上升沿驱动的,当时钟信号到来,a的值才会改变,在未到来时无论b怎么改变,a都保持原来的数值。

end

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1144

1144

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?