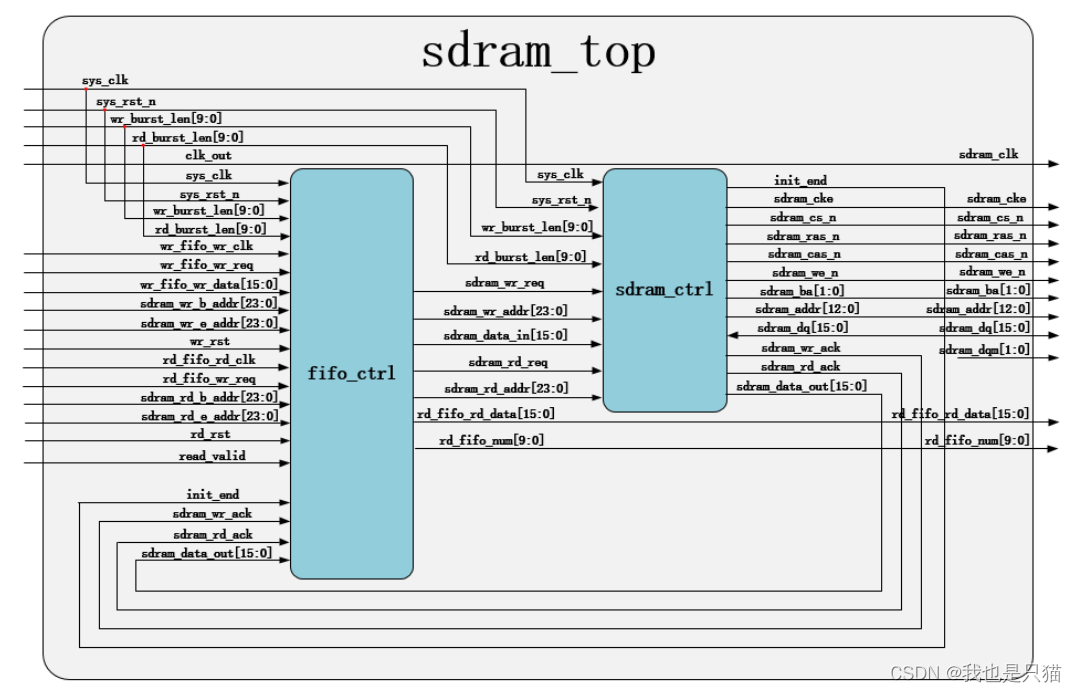

SDRAM 读写控制会使用到很多的接口,初学时很容易分不清,fifo_ctrl模块大部分端口可以分为四类,除开通常的时钟、复位,有FIFO读写和SDRAM读写。比较特殊的有rd_fifo_rd_data读FIFO读数据、rd_fifo_num读fifo中的数据量这两个信号,他们俩个直接从fifo_ctrl直接连接SDRAM,另一个单独的特殊信号为read_valid 读使能信号。结合例化模板,便很容易分清这些信号了。

fifo_ctrl模块端口:

module fifo_ctrl

(

input wire sys_clk , //系统时钟

input wire sys_rst_n , //复位信号

//写fifo信号

input wire wr_fifo_wr_clk , //写FIFO写时钟

input wire wr_fifo_wr_req , //写FIFO写请求

input wire [15:0] wr_fifo_wr_data , //写FIFO写数据

input wire [23:0] sdram_wr_b_addr , //写SDRAM首地址

input wire [23:0] sdram_wr_e_addr , //写SDRAM末地址

input wire [9:0] wr_burst_len , //写SDRAM数据突发长度

input wire wr_rst , //写复位信号

//读fifo信号

input wire rd_fifo_rd_clk , //读FIFO读时钟

input wire rd_fifo_rd_req , //读FIFO读请求

input wire [23:0] sdram_rd_b_addr , //读SDRAM首地址

input wire [23:0] sdram_rd_e_addr , //读SDRAM末地址

input wire [9:0] rd_burst_len , //读SDRAM数据突发长度

input wire rd_rst , //读复位信号

output wire [15:0] rd_fifo_rd_data , //读FIFO读数据

output wire [9:0] rd_fifo_num , //读fifo中的数据量

input wire read_valid , //SDRAM读使能

input wire init_end , //SDRAM初始化完成标志

//SDRAM写信号

input wire sdram_wr_ack , //SDRAM写响应

output reg sdram_wr_req , //SDRAM写请求

output reg [23:0] sdram_wr_addr , //SDRAM写地址

output wire [15:0] sdram_data_in , //写入SDRAM的数据

//SDRAM读信号

input wire sdram_rd_ack , //SDRAM读相应

input wire [15:0] sdram_data_out , //读出SDRAM数据

output reg sdram_rd_req , //SDRAM读请求

output reg [23:0] sdram_rd_addr //SDRAM读地址

);

5111

5111

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?