这是以TD_5.6.3_Release_88061生成的网表文件(其他工具生成的网表文件类似),与modelsim联合进行门级仿真的样例,时序仿真与门级仿真的方法类似,只是增加了标准延时文件。

1、建立门级仿真工程

将门级网表和testbench添加进来,建立工程。

2、查找所有的wire变量

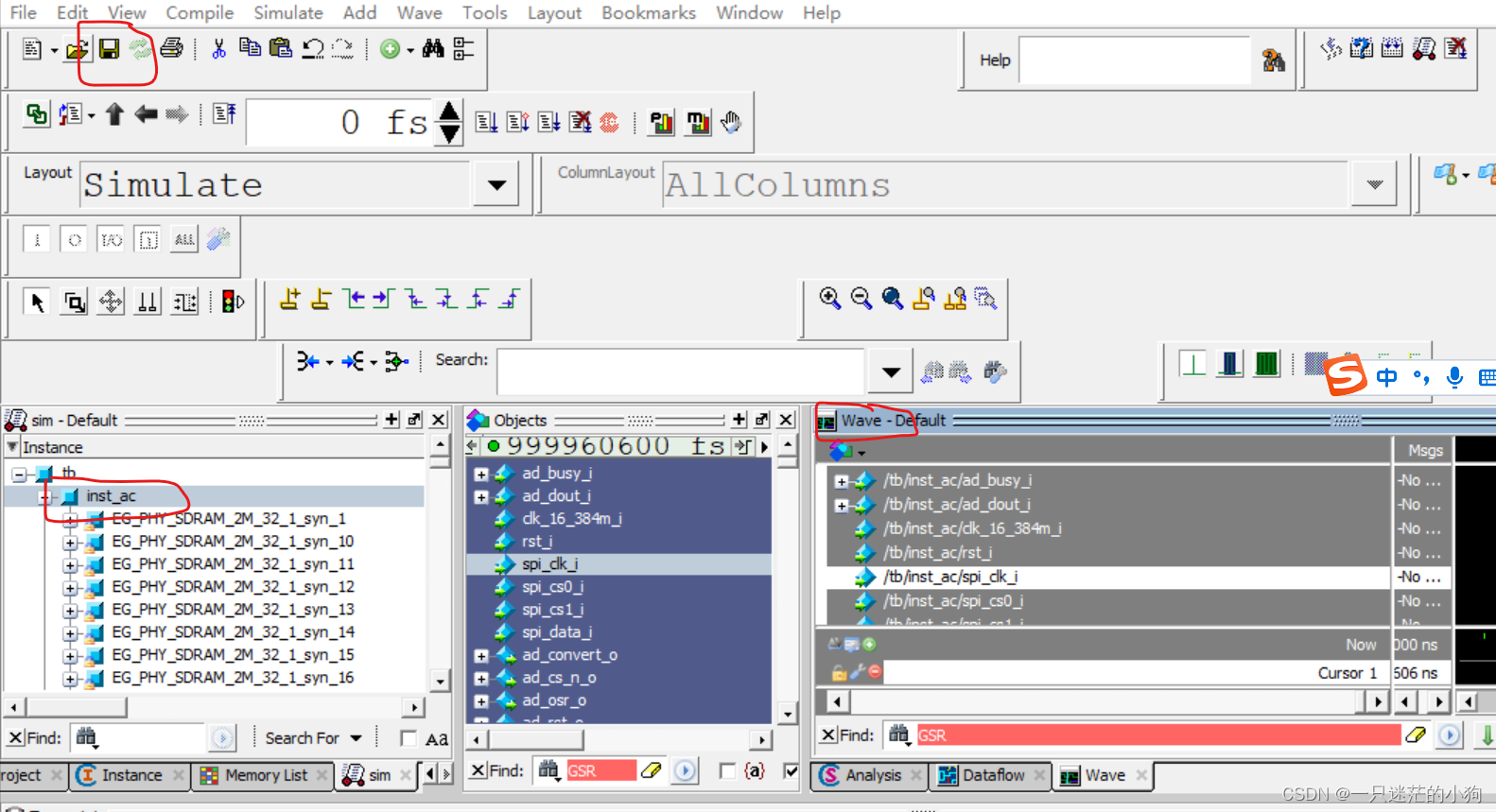

(1)在modelsim中将tb文件设置为顶层文件,运行仿真。

(2) 在sim窗口,找到顶层设计的实例化名字,鼠标右键点击add wave ,将所有的wire型变量添加到wave窗口。

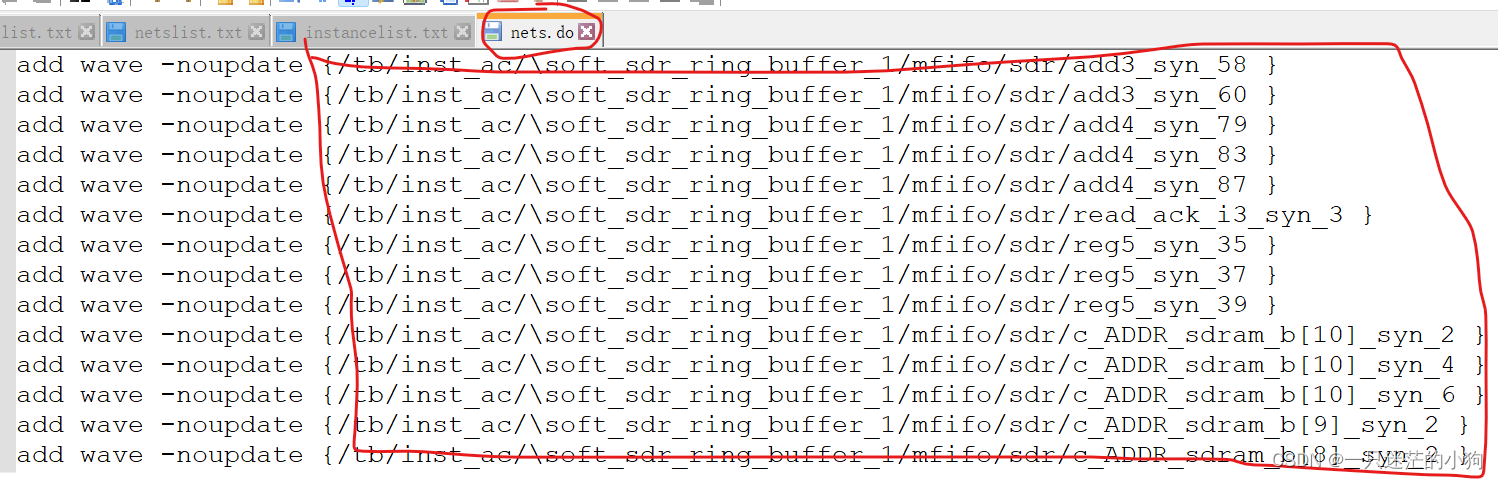

(3)点击save按钮,将所有的wire型变量保存到.do文件。下面就是设计中所有wire信号的绝对路径。

3、使用find connections命令查找所有wire变量的连接关系

主要是与instance的连接关系,这样整个设计的门级单元以及互联关系就清楚了。将所有的wire变量以及与instance之间的互联关系保存到txt文件,就可以追踪数据流了。

find connections {/tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/cnt }

# Connected nets for {/tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/cnt }

# output : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/ns[0]_syn_44 /q[0]

# output : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/ns[0]_syn_46 /q[0]

# output : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/reg0_syn_44 /q[0]

# output : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/reg0_syn_44 /q[1]

# output : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/reg0_syn_48 /q[0]

# output : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/reg0_syn_48 /q[1]

# output : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/reg0_syn_51 /q[0]

# output : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/reg0_syn_51 /q[1]

# internal : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/cnt

# input : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/add3_syn_70 /a[1]

# input : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/add3_syn_73 /a[0]

# input : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/add3_syn_73 /a[1]

# input : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/add3_syn_76 /a[0]

# input : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/add3_syn_76 /a[1]

# input : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/add3_syn_79 /a[0]

# input : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/add3_syn_79 /a[1]

# input : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/add3_syn_81 /a[0]

# input : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/reg4_syn_393 /a[0]

# input : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/reg4_syn_393 /a[1]

# input : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/reg4_syn_393 /b[0]

# input : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/reg4_syn_393 /b[1]

# input : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/reg4_syn_393 /c[0]

# input : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/reg4_syn_393 /c[1]

# input : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/reg4_syn_393 /d[0]

# input : /tb/inst_ac/\adc_array_1/adc_module[0]$adc7606_ctr_1/ad7606_1/reg4_syn_393 /d[1]

# (4)在modelsim中使用脚本将所有wire变量信号的连接关系保存到txt文件中

set wire_signals { /tb/inst/ClkIn

/tb/inst/CLK_dj

/tb/inst/RstnIn

/tb/inst/CmdRstIn

/tb/inst/DspIspIn

/tb/inst/DspHCntlOut

/tb/inst/DspHrwNOut

/tb/inst/DspHds1NOut

/tb/inst/DspHds2NOut

/tb/inst/DspHcsNOut

/tb/inst/DspHasNOut

/tb/inst/DspHrdyNIn

/tb/inst/DspHbeNOut

/tb/inst/DspHhwilOut };

foreach instt $wire_signals {

puts [find connections $instt]

}

set fhandle [open "wire_con.txt" w]

foreach ins $wire_signals {

puts $fhandle [find connections $ins]

}

close $fhandle;

打开wire_con.txt文件可以看到如下所示的连接关系

Connected nets for /tb/inst/ClkIn

internal : /tb/ClkIn

input : /tb/inst/ClkIn

input : /tb/inst/\ClkIn_pad/U0/U0 /PAD

Connected nets for /tb/inst/CLK_dj

internal : /tb/CLK_dj

input : /tb/inst/CLK_dj

input : /tb/inst/\CLK_dj_pad/U0/U0 /PAD

Connected nets for /tb/inst/RstnIn

internal : /tb/RstnIn

input : /tb/inst/RstnIn

input : /tb/inst/\RstnIn_pad/U0/U0 /PAD

Connected nets for /tb/inst/CmdRstIn

internal : /tb/CmdRstIn

input : /tb/inst/CmdRstIn

input : /tb/inst/\CmdRstIn_pad/U0/U0 /PAD

Connected nets for /tb/inst/DspIspIn

internal : /tb/DspIspIn

input : /tb/inst/DspIspIn

input : /tb/inst/\DspIspIn_pad/U0/U0 /PAD

Connected nets for /tb/inst/DspHCntlOut

output : /tb/inst/DspHCntlOut[0]

output : /tb/inst/DspHCntlOut[1]

output : /tb/inst/\DspHCntlOut_pad[0]/U0/U0 /PAD

output : /tb/inst/\DspHCntlOut_pad[1]/U0/U0 /PAD

internal : /tb/DspHCntlOut[0]

internal : /tb/DspHCntlOut[1] 将rtl代码范围缩小至某一个实例化模块,通过rtl代码与网表中的信号进行对比,找出需要查看的信号。

添加信号的方式有两种:

(1)

add wave {sim:/tb/inst_ac/\clk_management_1/sys_pll_1/pll_inst /*}

2716

2716

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?