1、RAM内容回顾

RAM(随机存取存储器),他可以随时把数据写入任一指定地址,也可随时从任一指定地址读出数据,其读写速度是由时钟频率决定的。

RAM分为

- SRAM(静态存储器) 速度快 、操作时序简单 、容量小、 成本高

- DRAM(动态存储器) 速度相对SRAM慢、操作时序复杂 、容量大,成本低

2、FPGA中的RAM

FPGA的片内存储器是SRAM的一种,主要用来存放程序执行过程中产生的中间数据、运算结果等信息。

Cyclone IV E系列的EP4CE10F17C8,该芯片是极具功耗和性价比优势,它拥有10320个逻辑单元、414Kbits的嵌入式存储资源、23个18×18的嵌入式乘法器、2个通用锁相环、10个全局时钟网络、8个用户IO BANK和最大179个用户I/O,嵌入式存储资源由一列M9K存储器模块组成,通过对这些M9K存储器模块进行配置,可以实现各种存储器的功能,例如:RAM、移位寄存器、ROM以及FIFO缓冲器。

FPGA内部的RAM或者双口RAM和外挂的功能一样,都是拿来存储数据的。放在FPGA内部的好处就是减少了读写的延时,使得数据读写速度更快。FPGA经常被拿来做一些数据处理,需要处理的数据从外部送入FPGA(例如传感器数据采集到芯片内部),先被存储到RAM内,再从RAM送到DSP(算法处理模块,可以是一段代码)进行运算,运算的结果可以直接送出FPGA、或者存到另一个RAM中等待做其他处理。

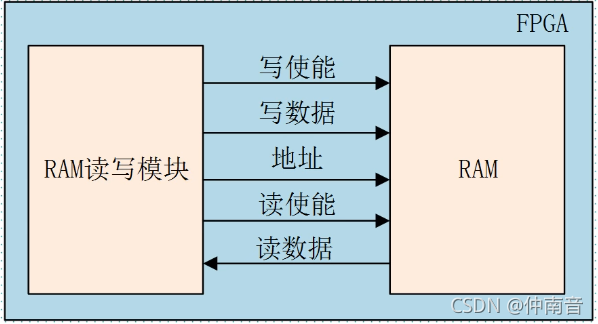

3、FPGA--RAM读写程序设计

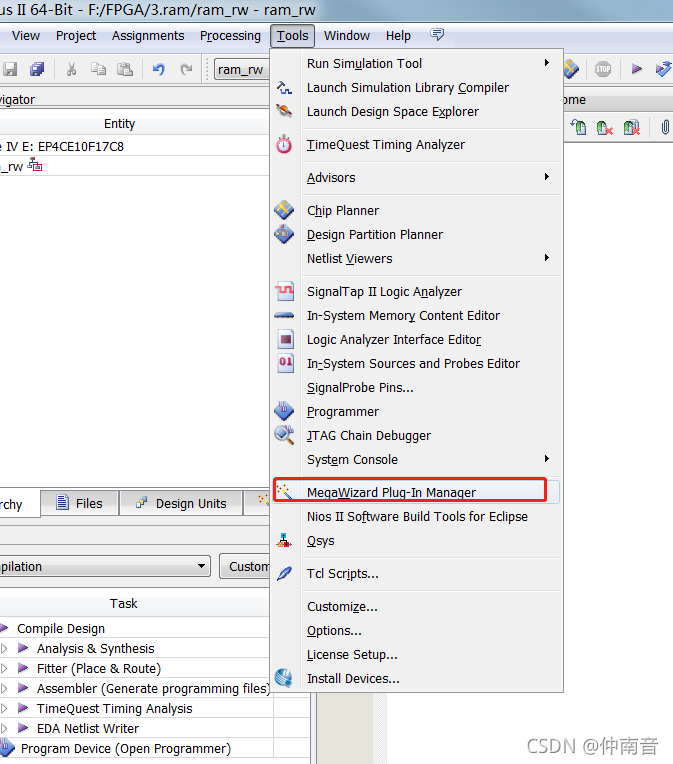

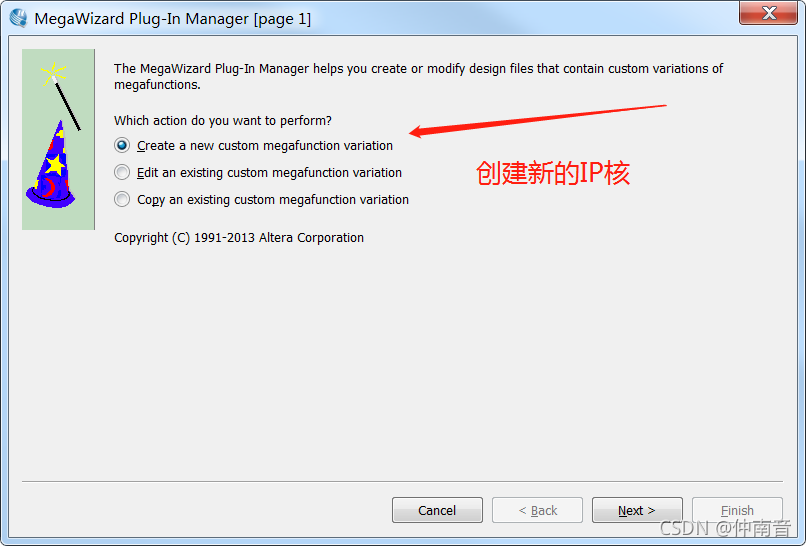

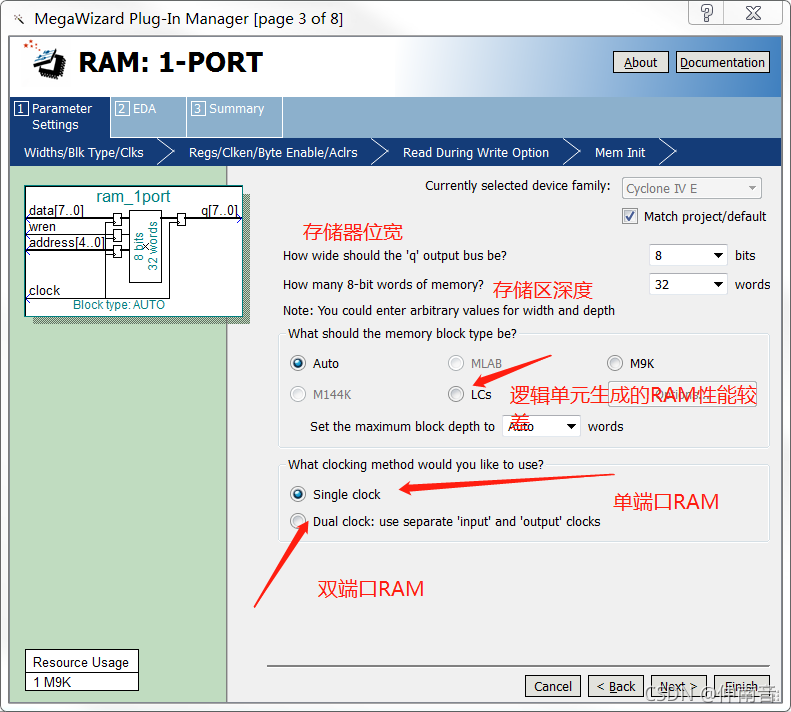

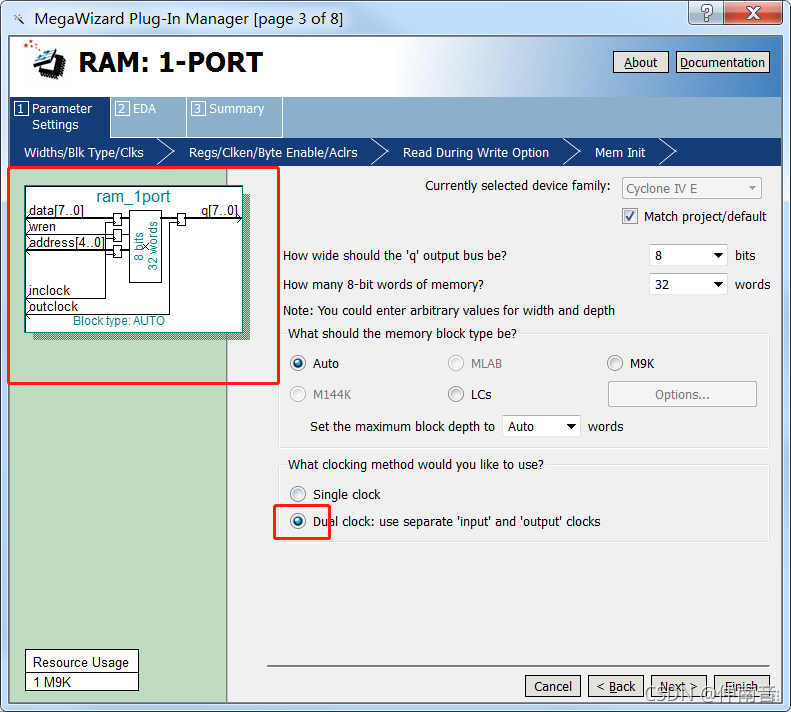

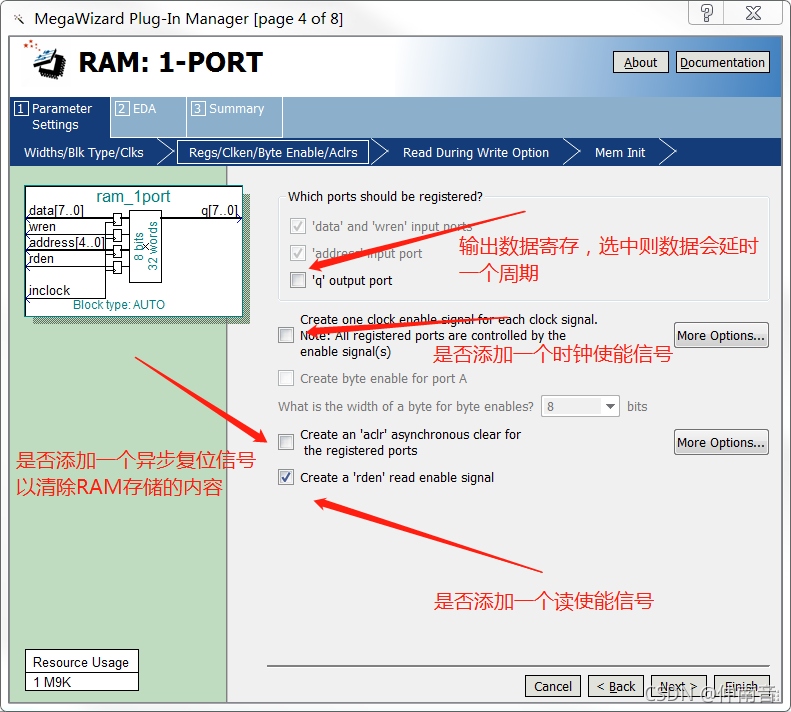

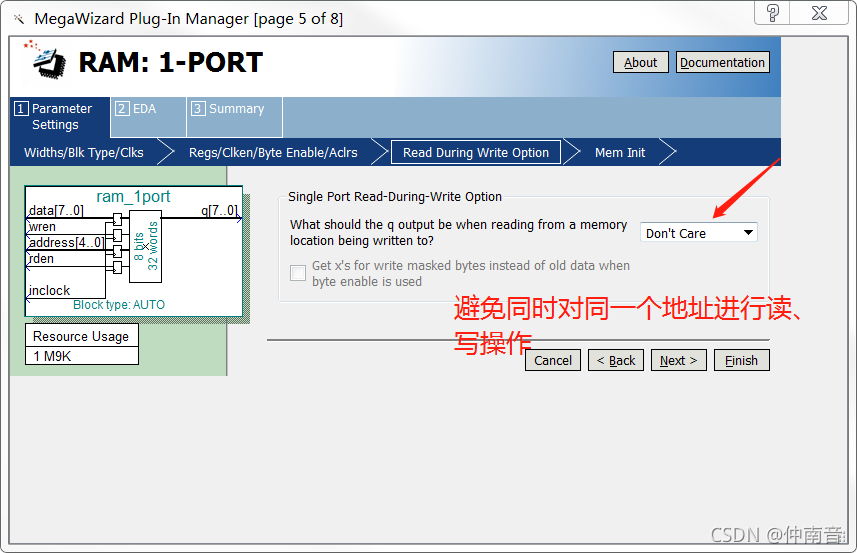

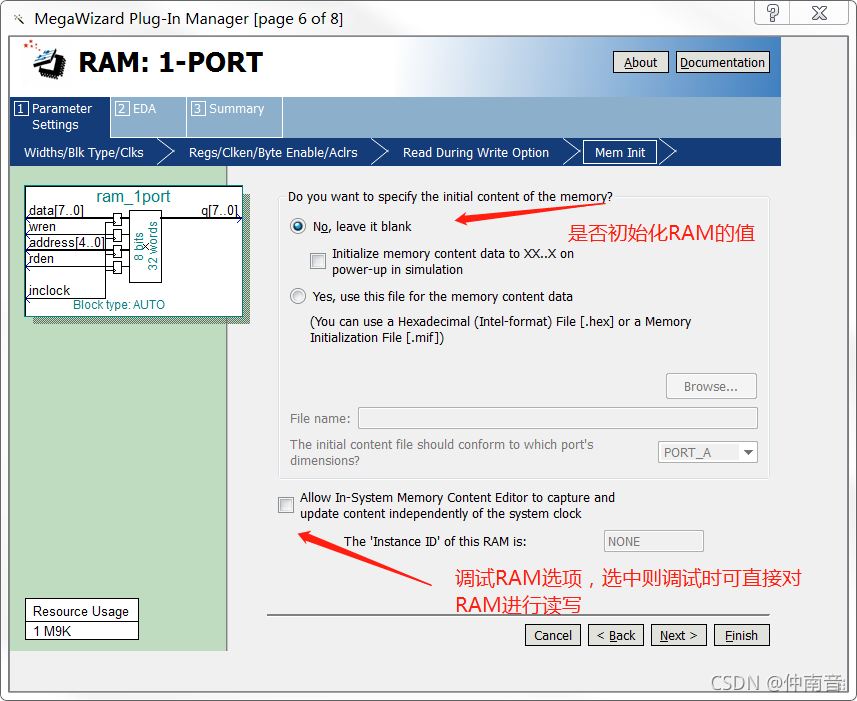

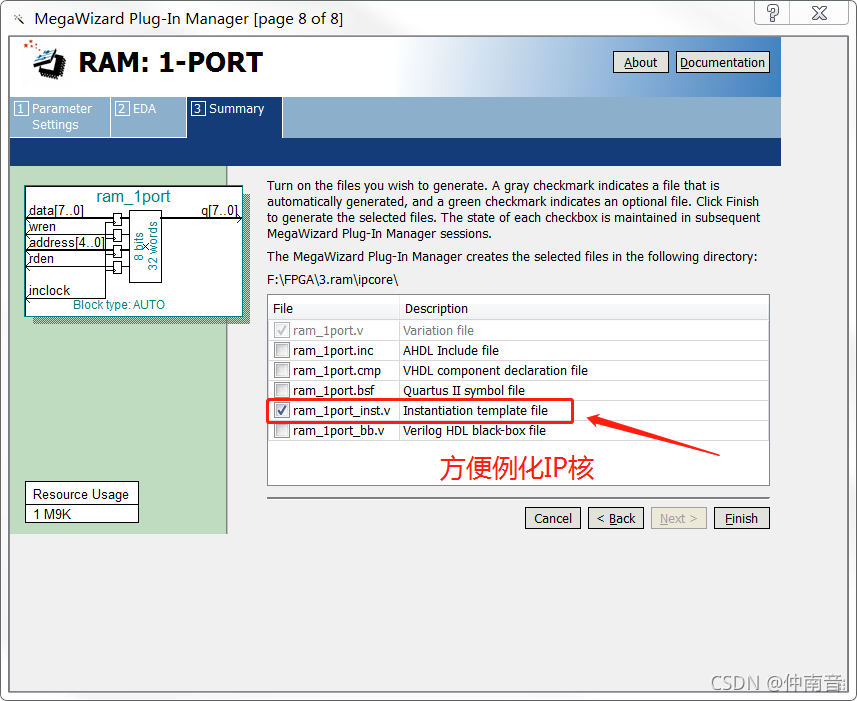

4、IP核生成RAM

5、编写RAM读写驱动程序

测试程序功能:

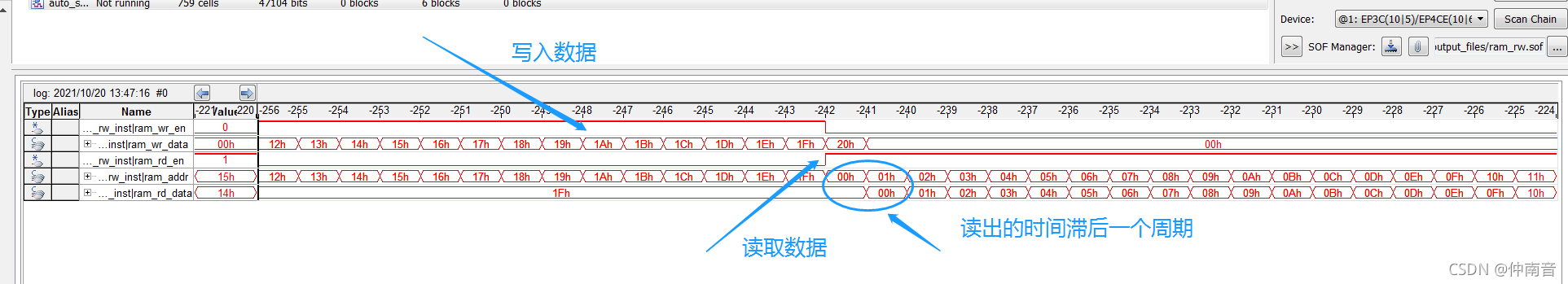

计数器累加,0~31时ram_wr_en为高电平 将数据写入RAM ,32~63时,ram_rd_en为低电高

将数据从RAM中读出。

//RAM读写驱动

module ram_rw(

input clk , //时钟信号

input rst_n , //复位信号,低电平有效

output ram_wr_en , //ram写使能

output ram_rd_en , //ram读使能

output reg [4:0] ram_addr , //ram读写地址

output reg [7:0] ram_wr_data, //ram写数据

input [7:0] ram_rd_data //ram读数据

);

reg [5:0] rw_cnt ; //读写控制计数器

//rw_cnt计数范围在0~31,ram_wr_en为高电平;32~63时,ram_wr_en为低电平

assign ram_wr_en = ((rw_cnt >= 6'd0) && (rw_cnt <= 6'd31)) ? 1'b1 : 1'b0;

//rw_cnt计数范围在32~63,ram_rd_en为高电平;0~31时,ram_rd_en为低电平

assign ram_rd_en = ((rw_cnt >= 6'd32) && (rw_cnt <= 6'd63)) ? 1'b1 : 1'b0; //assign赋值功能

//读写控制计数器,计数器范围0~63

always @(posedge clk or negedge rst_n) begin

if(rst_n == 1'b0)

rw_cnt <= 6'd0;

else if(rw_cnt == 6'd63) //计数到63清零

rw_cnt <= 6'd0;

else

rw_cnt <= rw_cnt + 6'd1;

end

//读写控制器计数范围:0~31 产生ram写使能信号和写数据信号

always @(posedge clk or negedge rst_n) begin

if(rst_n == 1'b0)

ram_wr_data <= 8'd0;

else if(rw_cnt >= 6'd0 && rw_cnt <= 6'd31)

ram_wr_data <= ram_wr_data + 8'd1;

else

ram_wr_data <= 8'd0;

end

//读写地址信号 范围:0~31

always @(posedge clk or negedge rst_n) begin

if(rst_n == 1'b0)

ram_addr <= 5'd0;

else if(ram_addr == 5'd31)

ram_addr <= 5'd0;

else

ram_addr <= ram_addr + 1'b1;

end

endmodule6、编写顶层驱动

实例化IP驱动程序 和IP核

//顶层模块

module ram_ip(

input sys_clk, //系统时钟

input sys_rst_n //系统复位,低电平有效

);

//wire define

wire ram_wr_en ; //ram写使能

wire ram_rd_en ; //ram读使能

wire [4:0] ram_addr ; //ram读写地址

wire [7:0] ram_wr_data ; //ram写数据

wire [7:0] ram_rd_data ; //ram读数据

ram_rw ram_rw_inst( //例化底层模块

.clk (sys_clk), //系统时钟

.rst_n (sys_rst_n), //系统复位,低电平有效

.ram_wr_en (ram_wr_en ), //ram写使能

.ram_rd_en (ram_rd_en ), //ram读使能

.ram_addr (ram_addr ), //ram读写地址

.ram_wr_data (ram_wr_data), //ram写数据

.ram_rd_data (ram_rd_data) //ram读数据

);

ram_1port ram_1port_inst ( //实例化底层IP核

.address (ram_addr), //ram读写地址

.inclock (sys_clk), //系统时钟

.data (ram_wr_data), //ram写数据

.rden (ram_rd_en), //ram读使能

.wren (ram_wr_en), //ram写使能

.q (ram_rd_data) //ram读数据

);

endmodule7、SignalTop II仿真调试

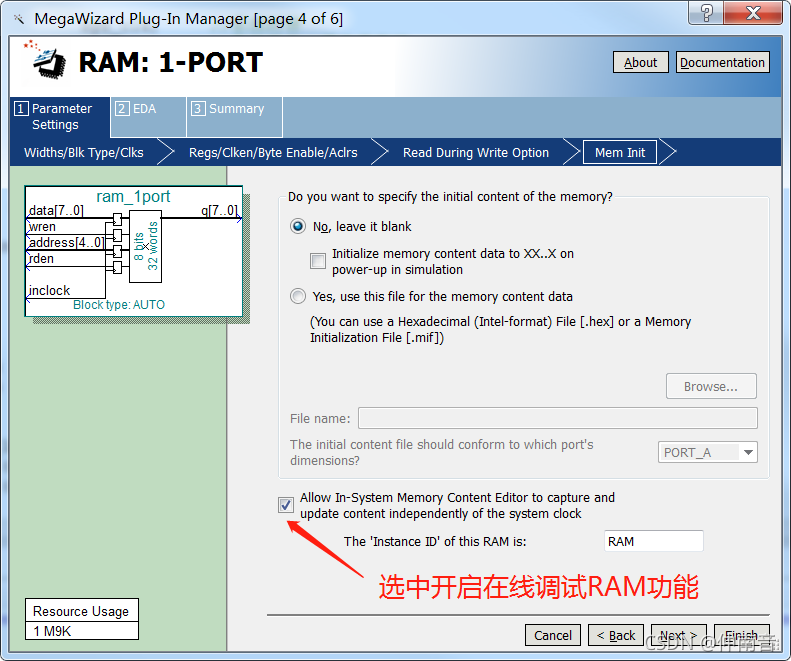

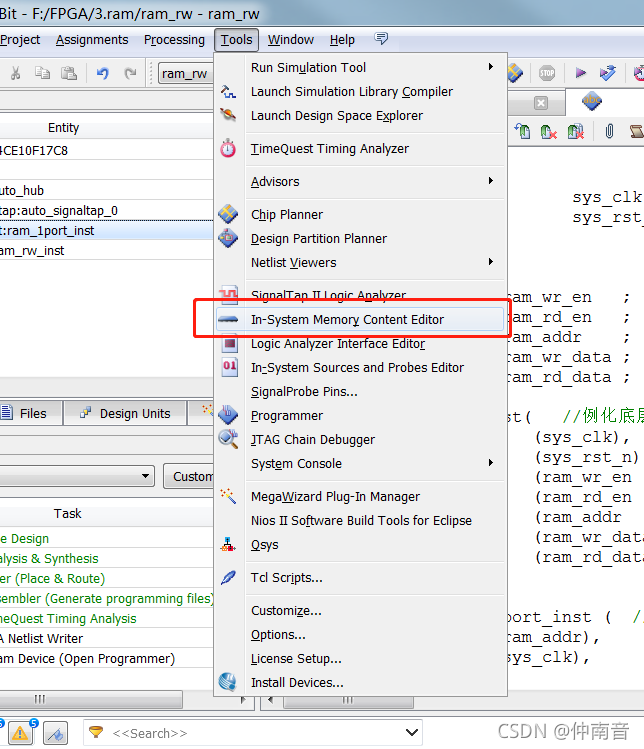

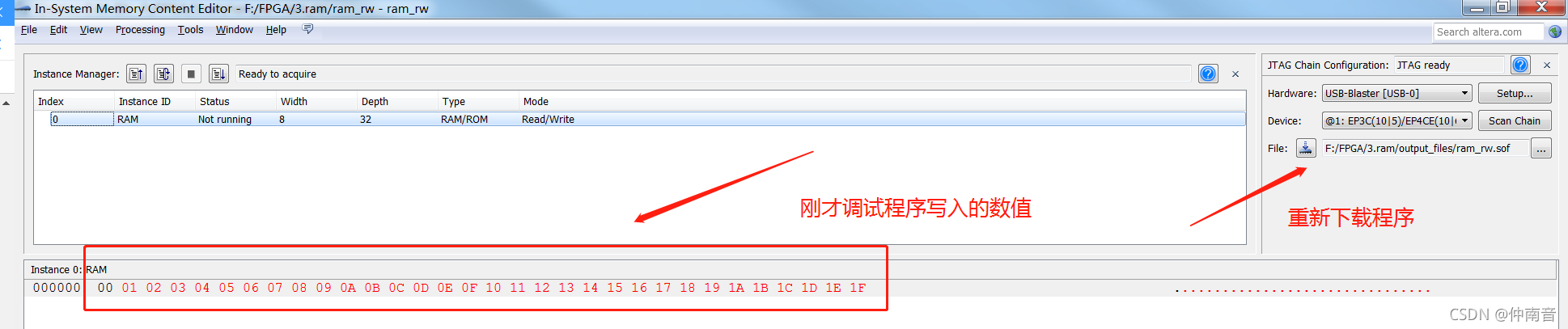

8、在线读取RAM

修改IP核配置:

重新编译工程

本文介绍了FPGA中的RAM类型,如SRAM和DRAM,强调了FPGA内部SRAM在数据处理中的作用,通过CycloneIVE EP4CE10F17C8芯片为例展示了其内存资源。此外,详细阐述了FPGA中RAM的读写程序设计,包括读写控制计数器的实现,并给出了顶层驱动模块的实例化。最后提到了SignalTopII仿真调试和在线读取RAM的操作步骤。

本文介绍了FPGA中的RAM类型,如SRAM和DRAM,强调了FPGA内部SRAM在数据处理中的作用,通过CycloneIVE EP4CE10F17C8芯片为例展示了其内存资源。此外,详细阐述了FPGA中RAM的读写程序设计,包括读写控制计数器的实现,并给出了顶层驱动模块的实例化。最后提到了SignalTopII仿真调试和在线读取RAM的操作步骤。

6385

6385

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?