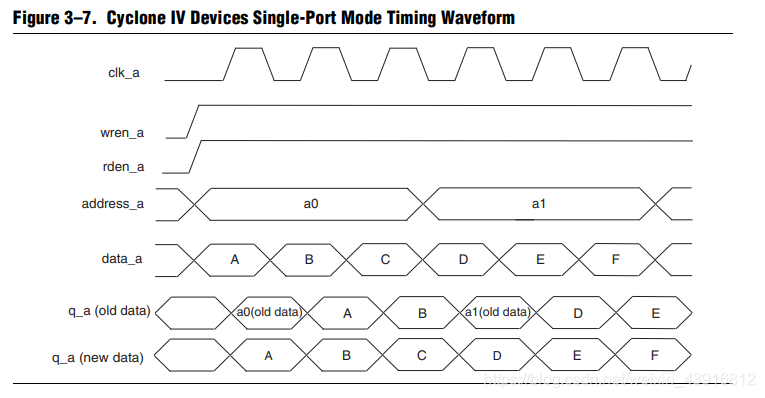

FPGA EP4CE10F17C8单端口RAM时序波形图

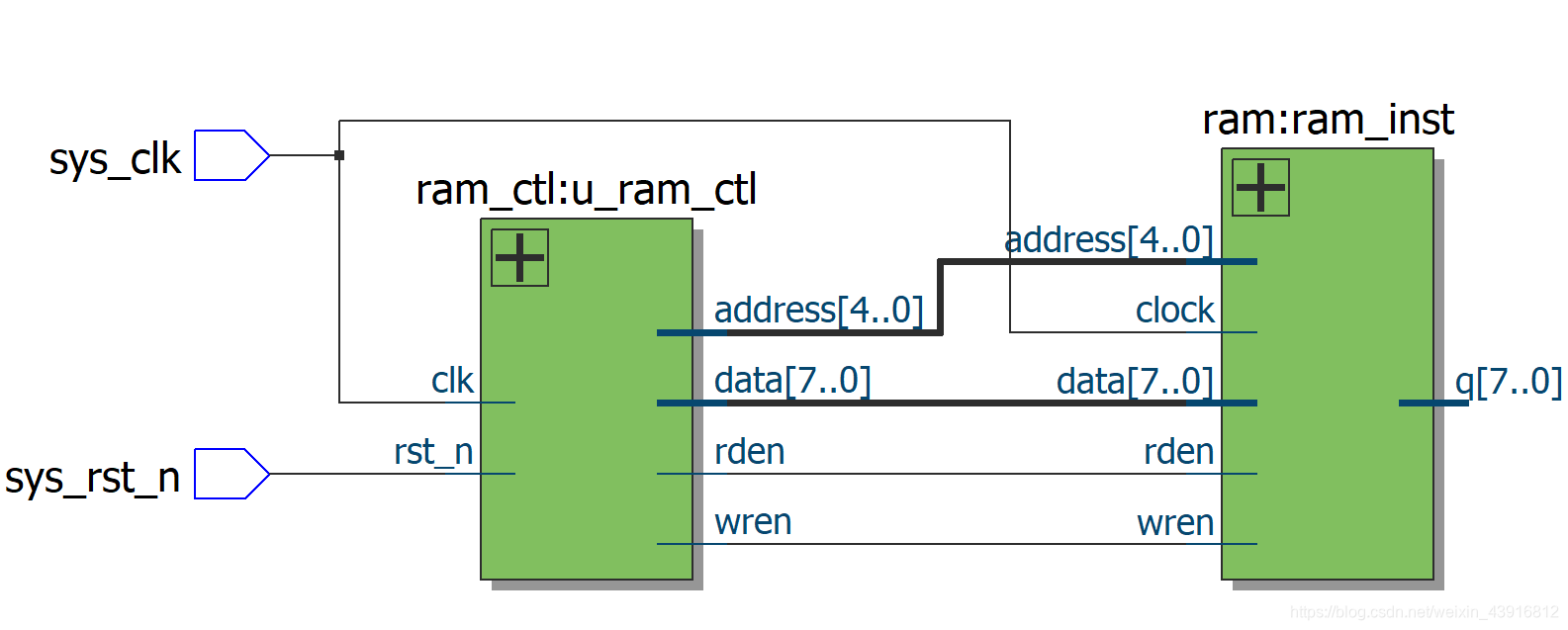

顶层模块

module ram_rw(

input sys_clk,

input sys_rst_n

);

wire rden_sig;

wire wren_sig;

wire [4:0] address_sig;

wire [7:0] data_sig;

wire [7:0] q_sig;

ram_ctl u_ram_ctl(

.clk ( sys_clk ),

.rst_n ( sys_rst_n ),

.address ( address_sig ),

.rden ( rden_sig ),

.wren ( wren_sig ),

.data (data_sig )

);

ram ram_inst (

.address ( address_sig ),

.clock ( sys_clk ),

.data ( data_sig ),

.rden ( rden_sig ),

.wren ( wren_sig ),

.q ( q_sig )

);

endmodule

RAM读写控制模块

module ram_ctl(

input clk,

input rst_n,

output wire rden,

output wire wren,

output reg [7:0] data,

output reg [4:0] address

);

reg [6:0] cnt;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt <= 7'b0;

else

if(cnt == 7'd63)

cnt <= 7'd0;

else

cnt <= cnt + 7'b1;

end

assign wren = (cnt >= 7'd0 && cnt <= 7'd31)?1'b1:1'b0;

assign rden = (cnt >= 7'd32 && cnt <= 7'd63)?1'b1:1'b0;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

address <= 5'd0;

else

if(cnt == 7'd31)

address <= 5'd0;

else

address <= address + 5'd1;

end

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

data <= 8'd0;

else

if(cnt < 8'd31)

data <= data + 8'd1;

else

data <= 8'd0;

end

endmodule

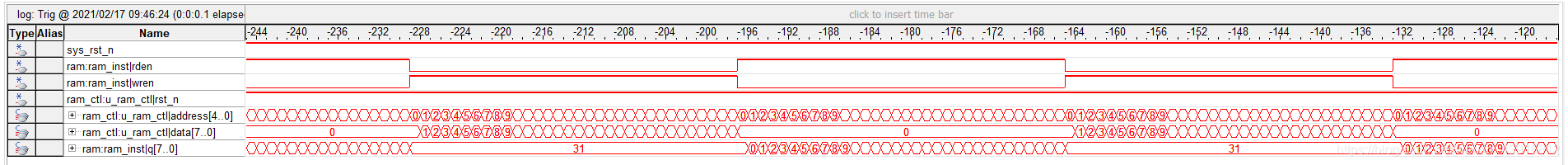

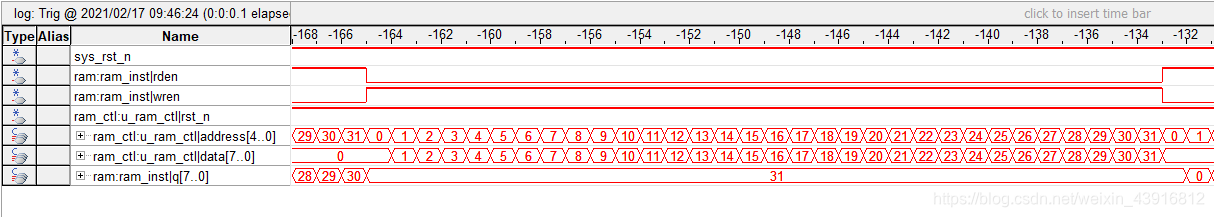

SignalTap II波形

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?