1、Linux系统

1.1、常用命令

1.2、vim编辑器

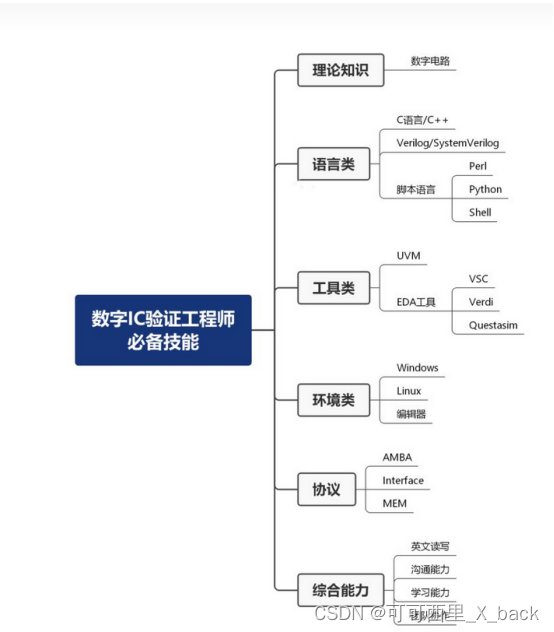

2、语言

2.1、有SystemVerilog基础

SystemVerilog结合了来自 Verilog、VHDL、C++的概念,还有验证平台语言和断言语言,也就是说,它将硬件描述语言(HDL)与现代的高层级验证语言(HVL)结合了起来。

拥有芯片设计及验证工程师所需的全部结构,它集成了面向对象编程、动态线程和线程间通信等特性,作为一种工业标准语言,SV全面综合了RTL设计、测试平台、断言和覆盖率,为系统级的设计及验证提供强大的支持作用。

能够和芯片验证方法学结合在一起,即作为实现方法学的一种语言工具。

SystemVerilog显然是描述最终的RTL设计本身的首选语言。

扩充了C语言数据类型、结构、压缩、和非压缩数组、接口、断言等。

可以使用受约束的随机测试达到令人满意的覆盖率。

设计和验证,沟通的桥梁。

推荐书籍:《SystemVerilog验证-测试平台编写指南》

2.2、有Verilog、VHDL基础(硬件设计语言,要求能看懂)

2.3、有c/c++基础

2.4、有脚本语言基础(Python、Shell、Perl)

2.5、Vera

OpenVera,商用硬件验证语言

2.6、E

商用硬件验证语言

2.7、VMM

验证方法学

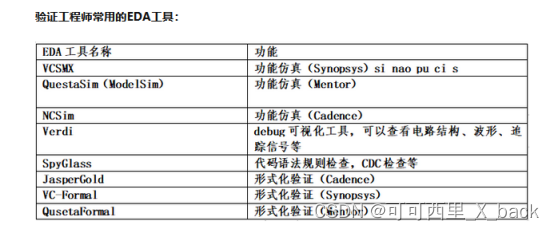

3、EDA等仿真工具使用

3.1、VCS

3.2、Verdet

4、UVM方法学

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?