解决VIvado编程中遇到的bug 5

语言 :Verilg HDL

EDA工具: Vivado、quartus2 、modelsim

- 关键词: 调用,Verilog HDL,modelsim,bug

一、引言

此系列博客专门发表 博主在开发过程中遇到的各种bug,以及bug的思路分析以及解决方法,帮助诸君在开发过程中遇到类似的问题能迅速找到解决思路和方法。

二、问题、分析及解决方法

1. vivado编译时报错

(1)错误

[Place 30-99] Placer failed with error: ‘IO Clock Placer stopped due

to earlier errors. Implementation Feasibility check failed, Please see the previously displayed individual error or warning messages for more details.’ Please review all ERROR, CRITICAL WARNING, and WARNING

messages during placement to understand the cause for failure.

##An unexpected error has occurred (EXCEPTION_ACCESS_VIOLATION)# Stack: no stack trace available, please use hs_err_.dmp instead.

(2)分析

Vivado在布局阶段遇到问题时的提示。错误代码[Place 30-99]表明布局器因为早期的错误而停止工作

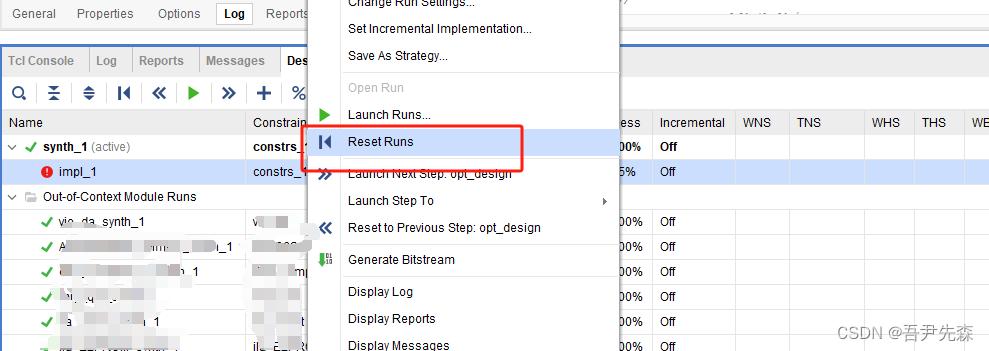

(3)解决办法

reset vivado工程的 综合和编译,然后重新编译生成比特流。

reset vivado工程的 综合和编译,然后重新编译生成比特流。

2、vivado中同时调用XADC核和DDR3核时,会报错如下

(1)错误

【place 30-99】 placer failed with error , there are more instances than sites for type XADC.

(2)分析

在Vivado布局过程中,布局器尝试放置的XADC(Xilinx Analog-to-Digital Converter)实例数量超过了目标设备上可用的XADC硬件资源位点数量。XADC是一种用于监视FPGA内部电压、温度等模拟信号的硬件模块。

(3)解决办法

解决办法:将DDR3核中xadc部分设置为disable。需要注意的是,重新生成DDR3 IP核后例化代码里会新增device_temp_i,需要将XADC核采集到的温度值,即do_out[15:4],送给device_temp_i。

3、quartus 2在编译程序时报错

(1)错误

Error (10171): Verilog HDL syntax error at top.v(71) near end of file expecting “endmodule”

(2)分析

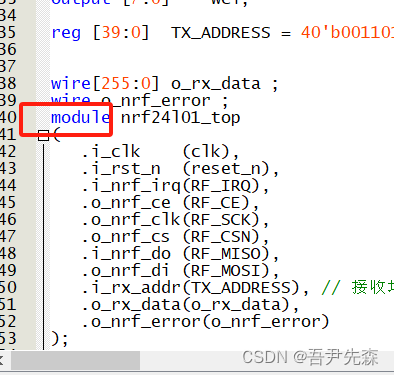

在Verilog文件top.v的第71行附近,存在一个语法错误。编译器期望在文件结束前看到一个endmodule声明,但是没有找到。

(3)解决办法

其实问题出现在模块中间,但是它报错定位到了结束的时,经过检查代码中间,例化模块时,发生错误,如下红框所示,模块名字不应该用module。

2、vivado在加载debug .ltx文件时报错

(1)错误

ERROR: [Labtools 27-3412] Mismatch between the design programmed into the device ‘xc7a100t’ (JTAG device index = ‘0’ and theprobefile(s) ‘F:/eth_test.runs/impl_1/ethernet_test.ltx’.The hw_probe ‘’ in the probes file has port index ‘5’. Thisport location for the ILA core at location (uuid_06FAF755911E5D2AB73B484E56CEC4D1), does not support a data probe.

(2)分析

错误 [Labtools 27-3412] 出现在使用 Vivado 进行 FPGA 硬件调试时,它表明了设备中编程的设计与探针文件(probe file)之间存在不匹配的情况。通常与ILA核的配置或探针文件有关。解决方案可能包括检查ILA核的时钟设置,确保ILA深度设置正确,以及确保探针文件与设计匹配

(3)解决办法

我可以确保我的ILA有时钟,但是还是一直报这样的错误,后来发现是板子使用的仿真器比较差,它是集成在开发板上的jtag。所以性能较差,需要将VIVADO的 hw的clk 速率调整到1m以下,就可以避免这样的错误了,唯一的缺点就是下载速率会变的慢一些。

那么如何将jtag的速率设置到1m左右呢,需要在vivado中打开硬件设备hw的时候,选择new target,选择手动添加hw,这个时候会出现速率的选择框,然后自动选择即可。

2787

2787

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?