作用:实现FIFO存储器读写指针比较好的方法就是使用格雷码计数器。格雷码计数器的优势在于其相邻两个数值之间只有一位发生变化,提高了系统的抗干扰能力,而且在计数时,各个输出的门电路翻转次数要远远小于二进制计数器,从而可以大幅度降低系统的功耗。

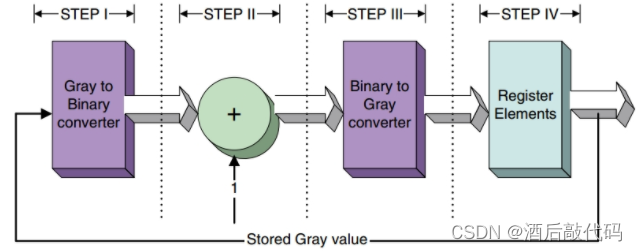

实现步骤:

- 将格雷值转换为二进制值。

- 根据条件递增二进制值。

- 将二进制值转换为格雷码

- 将计数器的最终格雷值保存到寄存器中。

格雷码转二进制

格雷码转二进制的公式如下:

binn−1 = grayn−1

bini = grayi⨁bini+1

格雷码转二进制Verilog代码如下:

module gray_to_bin (gray,bin);

parameter WIDTH = 8;

input [WIDTH-1:0] gray;

output [WIDTH-1:0] bin;

wire [WIDTH-1:0] bin;

assign bin[WIDTH-1] = gray[WIDTH-1];

genvar i;

generate

for (i=WIDTH-2; i>=0; i=i-1)

begin: gry_to_bin

assign bin[i] = bin[i+1] ^ gray[i];

end

endge

本文介绍了如何在FPGA开发中利用格雷码计数器实现FIFO存储器的读写指针比较。格雷码计数器因相邻数值仅一位变化,提高了抗干扰能力和降低了系统功耗。文章详细阐述了从格雷码到二进制、二进制加法、再到格雷码的转换过程,并提供了Verilog代码示例,展示了完整的格雷码计数器设计步骤。

本文介绍了如何在FPGA开发中利用格雷码计数器实现FIFO存储器的读写指针比较。格雷码计数器因相邻数值仅一位变化,提高了抗干扰能力和降低了系统功耗。文章详细阐述了从格雷码到二进制、二进制加法、再到格雷码的转换过程,并提供了Verilog代码示例,展示了完整的格雷码计数器设计步骤。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

760

760

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?