背景

精确的延迟计算对于复杂数字设计的时序闭合至关重要。在90纳米及以下工艺中,物理效应和设计风格为延迟计算带来了新的挑战。顶层互连由于金属线宽变窄而变得更具有电阻性,导致互连线阻抗远大于驱动单元的驱动电阻的情况。需要在广泛的Vdd值范围内进行分析以支持动态IR压降效应,以及包括电压岛和动态电压/频率调节在内的低功耗设计风格。在低电压下,温度依赖性的反转要求在中间温度值处进行分析。

因此需要一种延迟模型,它能够在接近电路仿真精度的同时,进行快速计算以支持最大设计的平面分析。该模型必须能够计算单元延迟、互连延迟、引脚斜率(也称为“转换时间”)和输入引脚电容,包括具有详细寄生参数的阶段。下面介绍的是新思科技的复合电流源时序模型(CCS Timing),该模型满足这些需求以及未来的延迟计算需求。

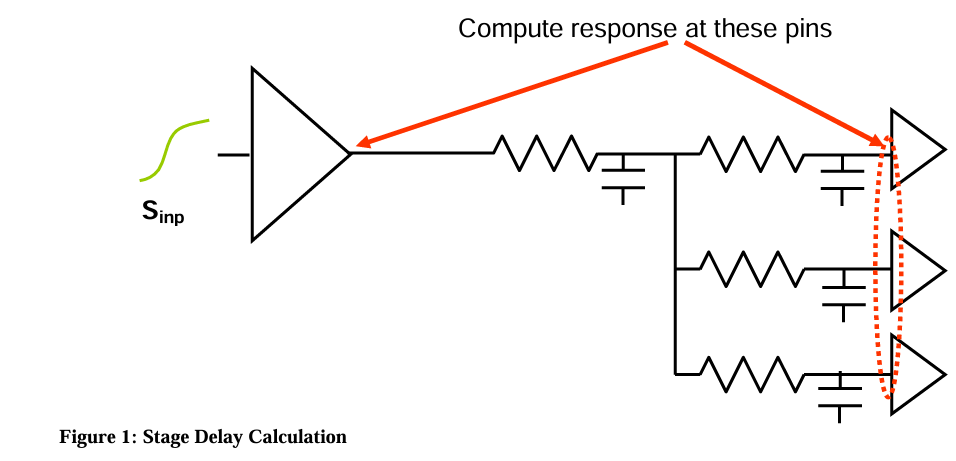

延迟计算是逐阶段进行的,其中每个阶段包括驱动单元弧、输出RC网络以及网络负载引脚的电容。 目标是根据驱动输入处的输入转换或波形,计算驱动输出和网络负载引脚处的响应,如图1所示。 然后使用计算出的响应来确定驱动器的单元延迟和负载引脚处的输入转换。

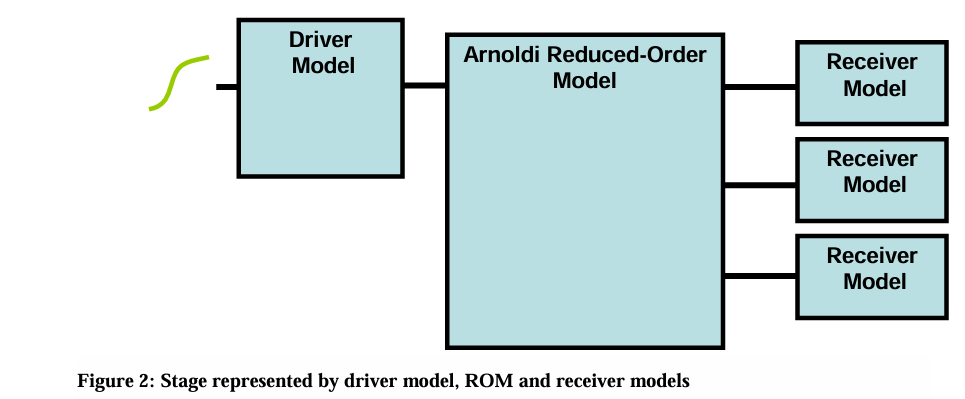

为高效执行级延迟计算,创建了三个模型: 驱动单元弧被替换为驱动模型;互连RC网络被替换为降阶模型,例如Block Arnoldi; 负载引脚被替换为接收器模型(如图2)。底层晶体管电路连接到任意RC网络时 ,接收器模型必须表示单元输入引脚的复杂输入电容。 晶体管不会向驱动器呈现恒定的输入电容。 等效电容负载( I = C d v d t I=C\frac{dv}{dt} I=Cdtdv)可以根据转换的上升/下降方向、 引脚的输入延迟、输出负载以及单元的状态而变化。 此外,在转换过程中,此电容可能会发生变化。 接收器模型必须能够表示所有这些效果。

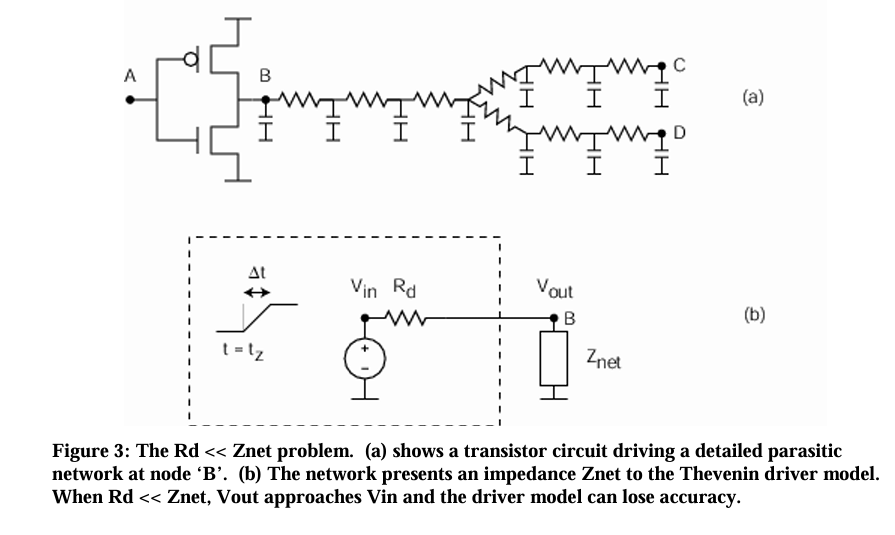

以前的驱动模型要么使用与电阻串联的时间依赖电压源(Thevenin模型),要么使用与电阻并联的时间依赖电流源(Norton模型)。这些模型中的电阻通常被称为“驱动电阻”,用于表示时序弧对输出电容的敏感性,而波形形状本身则主要由电压或电流源来表达。为了考虑晶体管行为的复杂方面,对这些模型的改进通常涉及使电压/电流源的时间依赖性质更加复杂。其他方法则涉及多个驱动电阻和任意动态阻抗。

然而,当使用传统模型驱动具有比驱动电阻 R d R_d Rd大得多的阻抗 Z n e t Z_{net} Znet的互连网络时,存在一个主要限制。考虑图 3 所示的 Thevenin 模型驱动详细寄生网络的情况。请注意,电路形成一个电压分压器,其关系为:

V o u t V i n = Z n e t R d + Z n e t \frac{V_{out}}{V_{in}} = \frac{Z_{net}}{R_d+Z_{net}} VinVout=Rd+ZnetZnet

当 R d ≪ Z n e t R_d \ll Z_{net} Rd≪Znet 时,该比值接近 1。这表明,基于与网络负载无关的驱动电阻(或任意阻抗)的驱动模型在这种情况下将无效。由于晶体管行为在靠近电源轨时偏离 Thevenin 电压源特性,因此当网络延迟大于输出转换时间时,这种情况通常最为严重。

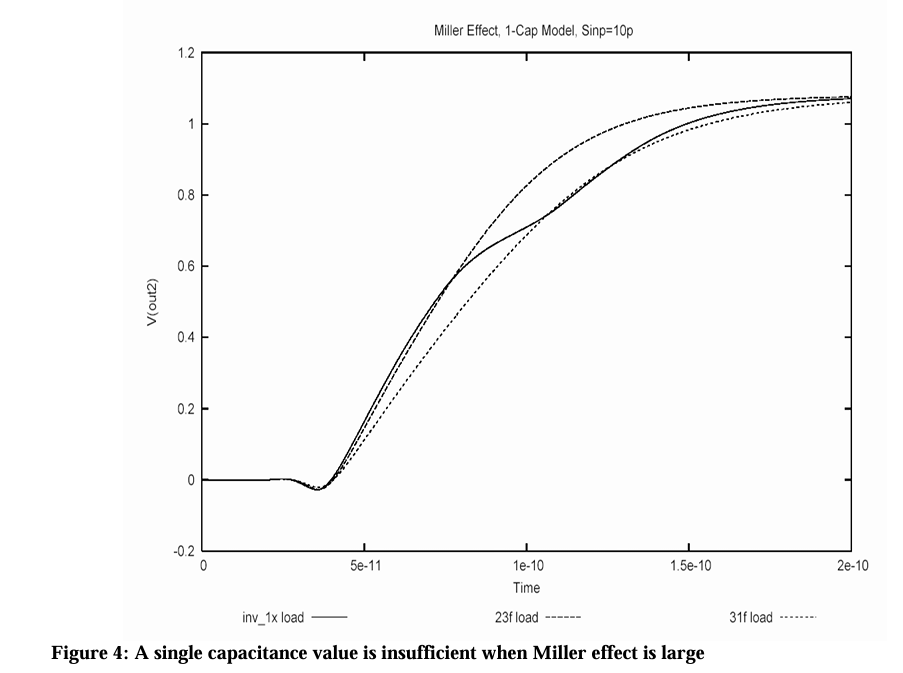

传统的接收器模型是输入引脚的单个电容值。虽然最近允许上升和下降转换使用不同的值,并引入了最小/最大范围,可以绑定复杂的电容效应,但在分析过程中会导致悲观结果。在整个转换过程中使用单一电容值会导致单级单元的不准确性,其中米勒效应显著,影响单元延迟和斜率的计算。图4显示,单级单元(例如反相器)的输入电压波形无法通过任何单一电容值很好地近似。

CCS模型

CCS时序模型由驱动模型和接收模型组成。驱动模型描述了时序弧如何将转换从输入传播到输出,以及如何驱动任意的RC网络。接收模型描述了输入引脚对驱动单元呈现的电容。CCS时序驱动模型是一个时间和电压依赖的电流源,具有本质上无限的驱动电阻,即使当 R d ≪ Z n e t R_d \ll Z_{net} Rd≪Znet时,也能提供高精度。该模型通过将集中负载的任意晶体管行为映射到任意详细的寄生网络的行为来实现这种精度,而不是通过建模晶体管行为。

考虑一组输出电流随时间变化的预特征测量值,对于特定的输入斜率和一组输出电容。 当我们将这些电流应用于各自的电容时,我们可以重建电压波形。 如果我们遇到一个未进行预特征分析的输出电容,我们可以通过插值电流来预测结果波形。 同样,如果我们遇到一个未用于预特征分析的输入斜率,我们也可以进行插值。

现在考虑驱动一个详细的寄生网络。在给定的时间步长,我们可以将预表征的输出电流应用到网络中。将有一个唯一的电流,在给定的时间步长上,它会在集中电容和网络上产生相同的电压。这个电流就是给定时间步长的选择值,我们在这个后续的每个时间步长重复此过程。CCS 时序延迟计算使用先进的插值技术,以确定输入斜率和/或输出负载值与单元表征期间使用的值不匹配时的电流波形。此外,通过使用多个库中的数据,插值还用于 VDD 和温度的中间值。

CCS时序表征

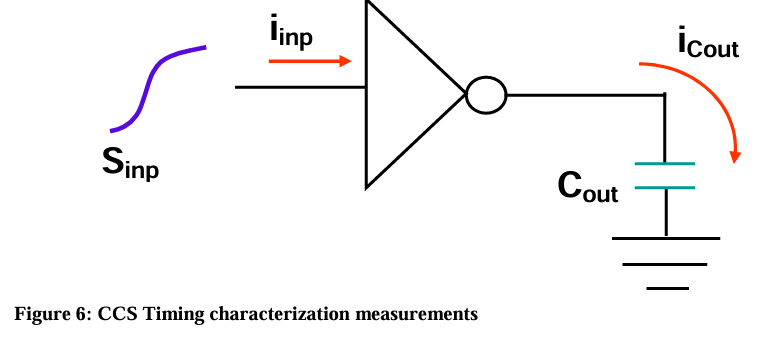

为CCS时序表征单元时序弧与非线性延迟模型(NLDM)的表征非常相似:选择输入激励以产生特定的输入转换时间(Sinp);在输出引脚上连接负载电容(Cout);并以与NLDM相同的方式运行电路仿真。但是,而不是测量输出引脚上的电压阈值,而是测量通过负载电容器流入输出引脚的电流。Cout上的电流用于驱动程序模型,而流入输入引脚的电流则用于确定接收器模型。

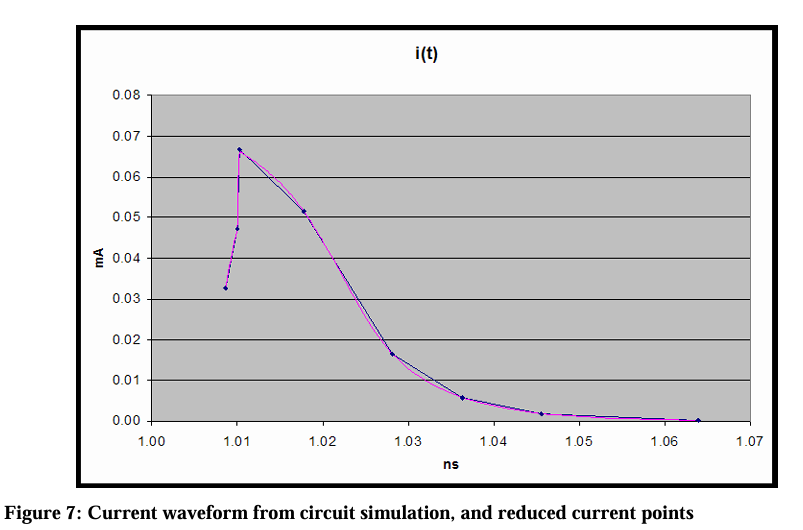

这些表征实验针对不同的Sinp和Cout组合的表格重复进行。 每个电路仿真时间步长通过Cout的电流都被保存,然后缩减为一组小得多的电流和时间(i,t)点。 这些点的选择确保在过渡期间的每个时间步长上都可以精确重现Vout(t)。图7显示了完整的i(t)波形和减少后的点集示例。

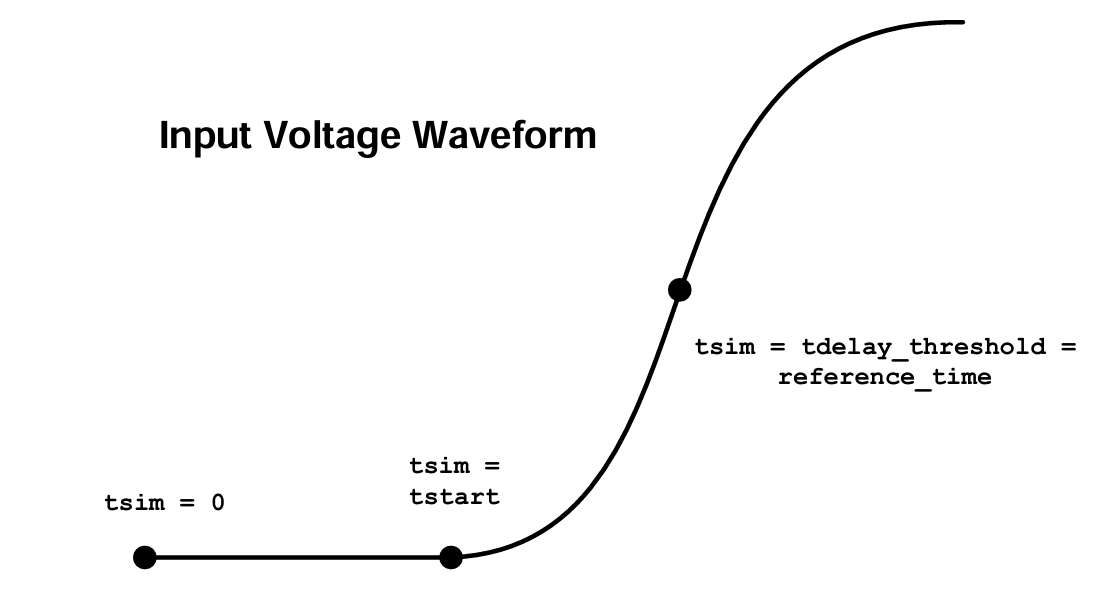

输入引脚的电流和电压会被保存,然后用于确定C1和C2的值,从而使门级延迟计算能够 closely 匹配到延迟阈值的时间以及到输入引脚第二个斜率阈值的时间。为了计算单元延迟,还需要额外的一条信息,即输入参考时间。参考时间是输入引脚波形跨越上升或下降延迟阈值(这通常为VDD的50%)时的仿真时间。

CCS 工艺库

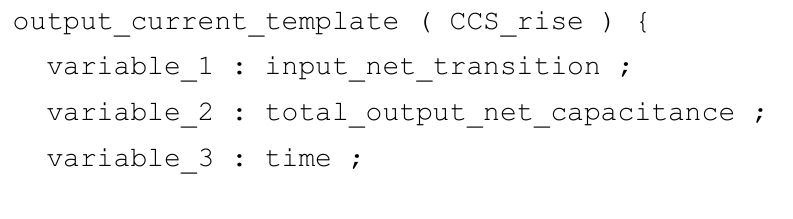

复合电流源驱动器模型的模板始终将时间作为变量3的值。 输入转换时间和电容值可以分配给变量1或变量2。 对于output_current_rise组,电流向量的值部分中的电流值必须为正。 同样,对于output_current_fall组,电流值必须为负。电流向量不应包含零电流值,PrimeTime 假定在电流向量的第一个时间值之前初始电流为零,最终电流被认为是电流向量中存储的最后一个值。

reference time

参考时间属性是输入电压特征波形穿越输入延迟阈值的时间,相同输入转换时间对应的参考时间是相同的(不管负载电容如何变化)。CCS时序特征的开始时间是单元输入上的电压转换开始的时间,这早于参考时间。在CCS延迟计算中,参考时间用于计算单元延迟。下图是参考时间的示例:

接收器电容

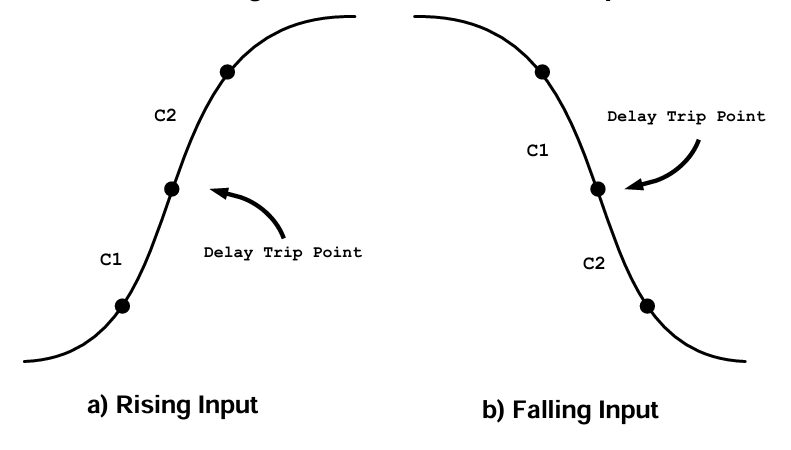

在 CCS 时序建模中,接收器模型使用两个电容值(C1 和 C2)来近似模拟单元输入电容在信号转换过程中的变化行为。

在 PrimeTime 的延迟计算中:

-

C1 表示在输入信号转换、但尚未达到延迟触发点(delay trigger point)之前的等效电容;

-

C2 表示在超过触发点之后的等效电容。

这一建模方式适用于输入信号的上升沿和下降沿。

库中使用 receiver_capacitance*_rise 和 receiver_capacitance*_fall 语法来描述这两个电容值,它们均基于输入端的信号转换特性。

在选择电容值时,建议:

-

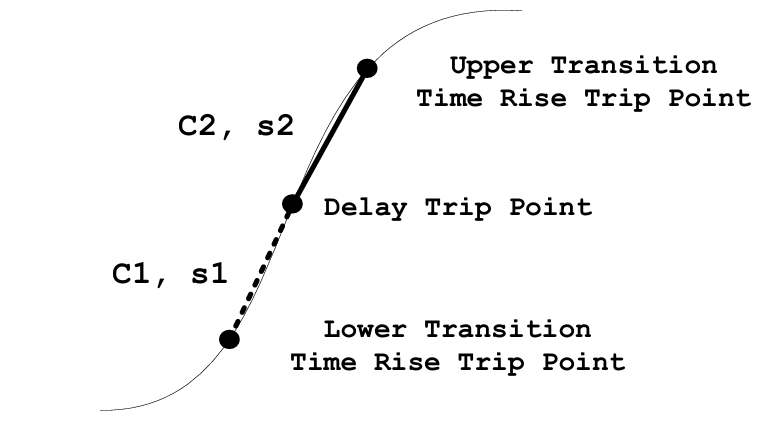

设置 C1 值,使其对应的电流积分产生的电压波形能够精确匹配单元的延迟触发点;

-

设置 C2 值,使其对应的电流波形在继续转换时能准确对齐单元输入波形的第二个斜率变化点(slope inflection point)。

由于 C1 和 C2 的提取依赖于输入波形的局部段,而非完整转换,因此它们所代表的转换时间通常小于库中定义的标准转换时间。因此,接收器模型中的转换时间索引应基于波形的局部转换时间,并通过适当的外推(extrapolation)方式对齐标准库中覆盖的转换时间范围。

CCS接收器模型使用两个电容值来模拟转换期间的单元加载。 为了确保CCS接收器的最佳精度,计算得到的C1值应确保点 (V2,t2) 完全匹配。 计算得到的C2值应确保点 (V3,t3) 完全匹配。

新思科技的“CCS jumpstart scripts”包含一个模块,该模块计算每个接收电容的最优值。以下是“CCS_Solve.pm”模块的工作原理:

For each rising timing arc:

- Find C1 “seed value” below delay threshold

C 1 s e e d = ∫ t 1 t 2 I ( t ) d t V 2 C_{1seed}=\frac{\int_{t_1}^{t_2}I(t)dt}{V_2} C1seed=V2∫t1t2I(t)dt t1 = starting time , t2 =time at delay threshold V2

- Find C2 “seed value” above delay threshold

C 2 s e e d = ∫ t 2 t 3 I ( t ) d t V d d − V 2 C_{2seed}=\frac{\int_{t_2}^{t_3}I(t)dt}{V_{dd} - V_2} C2seed=Vdd−V2∫t2t3I(t)dt t2 = time at delay threshold V2, t3 = ending time

- Calculate optimal C1 and C2 values.

• Brent algorithm is used to minimize curve fit error over a specific waveform range

• The default waveform range is a single point (V2, t2) for C1

C1 = CCS_Solve::brent (C1seed , …, (V2, t2));

• The default waveform range is a two points (V2, t2) and (V3, t3,) for C2

C2 = CCS_Solve::brent (C2seed , …, (V2, t2), (V3, t3,));

-

Test receiver values by calculating delay and slew values and comparing to actual delay and slew values.

-

Store results into characterization database in Liberty syntax

总结

NLDM的局限性

NLDM(Nonlinear Delay Model)使用 LUT(查找表)建模延迟和转换时间,它的延迟计算方式很简单:

-

输入条件:输入的 slew(转换时间)+ 输出的负载电容

-

输出结果:对应的 delay 和 output transition(输出边沿rf)

但它有几个本质缺陷:

- 假设波形是理想的(近似线性)

实际波形可能是非线性或受干扰的(串扰/噪声),但 NLDM 无法表达这些波形细节。

- 只考虑 0.5VDD 点

只关心输入输出达到 0.5VDD 的时间,却忽略了整条波形路径,容易低估/高估 delay。

- 无法准确传播波形

输入波形被当作单一 slew 值处理,无法表示实际形状、二次变化、延迟跳变等。

CCS优势

- 真实电流模型驱动

- CCS 使用电流源建模驱动单元,也就是说它记录了:

I o u t = f ( V o u t , S l e w i n ) I_{out} = f(V_{out}, Slew_{in}) Iout=f(Vout,Slewin)

- 这样可以通过电流积分,精确计算真实的输出波形 V(t):

V o u t ( t ) = ∫ I o u t ( t ) C l o a d d t V_{out}(t) = \int \frac{I_{out}(t)}{C_{load}} dt Vout(t)=∫CloadIout(t)dt

- 波形传播机制

-

CCS 会将驱动单元的输出波形传播到接收单元,而接收单元也不再是一个简单电容,而是具有动态电容响应(C1/C2)的模型。

-

每一级的门都基于真实波形传播进行 delay 和 slew 的重新计算。

-

可以处理波形失真、串扰叠加、门限偏移等问题。

- 支持信号完整性分析

- CCS 能够准确评估:串扰延迟,波形畸变,多驱动源,噪声传播

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?