对于cell的delay的计算,由于规模的原因,是不可能通过晶体管级仿真进行的。

所以引入了静态时序分析的概念。

而在静态时序分析中,cell delay,是通过查找表并进行插值来得到的,从而大大减少了计算量,提高了工具的运行速度。

对cell delay的表征(characterization),有两种形式。

CCS:composite current source

NLDM:non linear delay model

CCS,已经被引用多年。目前,与nldm一样,已经成为了单元库的标配。

本文将简单介绍一下两种delay model,以及他们的区别。

NLDM

nldm是最早引入的技术。在65nm以及之前,一直是一种可靠的迅速得到cell的delay的方法。

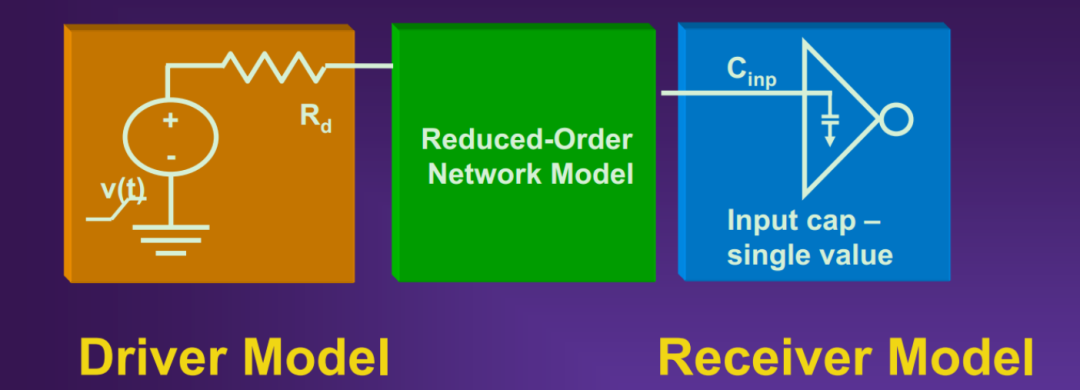

nldm包括 nldm driver model 和 nldm receiver model

nldm driver model

nldm表征的是cell的input到ouput的delay值以及输出的transition time。

如图,我们以一个反相器为例,在o

本文介绍了静态时序分析(STA)中的两种cell延迟模型——NLDM(非线性延迟模型)和CCS(复合电流源模型)。NLDM包括driver和receiver模型,但在小尺寸工艺中面临电阻和Miller效应问题。相比之下,CCS模型解决了这些问题,提供更精确的延迟和电流波形描述,尤其是在处理大电阻net和Miller效应时表现优越。

本文介绍了静态时序分析(STA)中的两种cell延迟模型——NLDM(非线性延迟模型)和CCS(复合电流源模型)。NLDM包括driver和receiver模型,但在小尺寸工艺中面临电阻和Miller效应问题。相比之下,CCS模型解决了这些问题,提供更精确的延迟和电流波形描述,尤其是在处理大电阻net和Miller效应时表现优越。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3556

3556

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?