本文以Vivado RAM IP的读写为例,实战AXI总线。

1.RAM IP配置

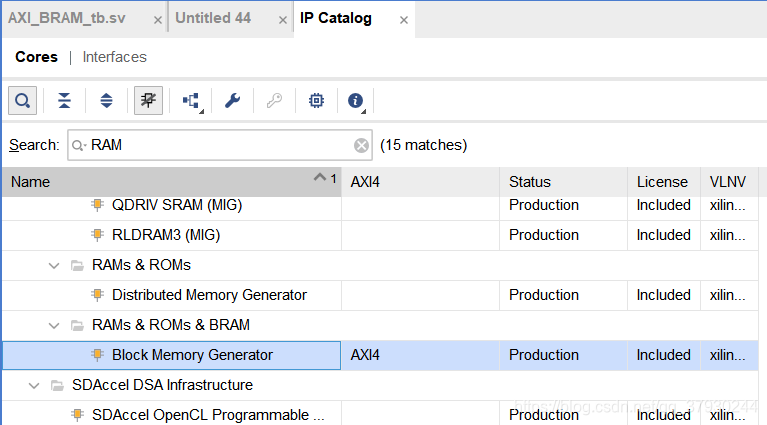

在IP Catalog中选择Block Memory Generator.

配置接口为AXI4-lite。

配置位宽为32bits,深度为1024。

2.RAM IP基本操作

在Source->IP Source->Instantiation Template->BRAM.veo中查看生成的例化模板:

//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG

BRAM your_instance_name (

.rsta_busy(rsta_busy), // output wire rsta_busy

.rstb_busy(rstb_busy), // output wire rstb_busy

.s_aclk(s_aclk), // input wire s_aclk

.s_aresetn(s_aresetn), // input wire s_aresetn

.s_axi_awaddr(s_axi_awaddr), // input wire [31 : 0] s_axi_awaddr

.s_axi_awvalid(s_axi_awvalid), // input wire s_axi_awvalid

.s_axi_awready(s_axi_awready), // output wire s_axi_awready

.s_axi_wdata(s_axi_wdata), // input wire [31 : 0] s_axi_wdata

.s_axi_wstrb(s_axi_wstrb), // input wire [3 : 0] s_axi_wstrb

.s_axi_wvalid(s_axi_wvalid), // input wire s_axi_wvalid

.s_axi_wready(s_axi_wready), // output wire s_axi_wready

.s_axi_bresp(s_axi_bresp),

本文详细介绍了如何在Vivado中配置AXI4-lite接口的RAM IP,包括配置参数、理解读写时序,并通过状态机实现读写操作。还提供了仿真时序图和注意事项,以验证读写操作的正确性。

本文详细介绍了如何在Vivado中配置AXI4-lite接口的RAM IP,包括配置参数、理解读写时序,并通过状态机实现读写操作。还提供了仿真时序图和注意事项,以验证读写操作的正确性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?