1.滤波器类型

模拟滤波器分为有源和无源,在上一节已经见过——FPGA知识积累【5】第6点

现在讲讲数字滤波器的类型:

①按照频带分类:

W为某截至频率

低通滤波器(LPF):通带0 ~ W

带通滤波器(BPF):通带W1 ~ W2

带阻滤波器(BSF):阻带W1 ~ W2 (限波)

高通滤波器(HPF):通带 W ~ ∞

全通滤波器(APF):全通

②按响应类型分类:

巴特沃斯响应滤波器:最大化滤波器的通带平坦度

贝塞尔响应滤波器:最小化了通带的相位非线性

切比雪夫响应滤波器:通带或阻带上频率响应幅度等波纹波动的滤波器

③按单位脉冲分类:

无限脉冲响应滤波器(IIR):递归滤波器,从硬件的角度来看,IIR滤波器速度快,效率高、实时IIR滤波器的采样率远高于FIR,且具有反馈

有限脉冲响应滤波器(FIR):有限长单位冲激响应滤波器,又称为非递归型滤波器,是数字信号处理系统中最基本的元件

2.最 小/大 项性质

最小项的性质:

①在输入变量任一取值下,有且仅有一个最小项的值为1;

②全体最小项之和为1 ;

③任何两个最小项之积为0 ;

④两个相邻的最小项之和可以合并,消去一对因子,只留下公共因子;(卡诺图重要原理)相邻:仅一个因子不同的最小项,如:A’BC’与A’BC;

最大项的性质:

①在输入变量任一取值下,有且仅有一个最大项的值为0 ;

②全体最大项之积为0 ;

③任何两个最大项之和为1 ;

④两个相邻的最大项之积可以合并,消去一对因子,只留下公共因子。相邻:仅一个因子不同的最大项,如:A’+B+C和A’+B+C

3.高速低速信号

以下是Candence对高速信号的判断;

①凡是大于50MHz的信号,就是高速信号

②与频率没有直接关系,而是信号上升/下降沿小于50 ps时就认为是高速信号

③当信号所在的传输路径长度大于1/6λ ,信号被认为是高速信号

④当信号沿着传输路径传输,发生了严重的趋肤效应和电离损耗时,被认为是高速信号

以上几种定义,在某种程度上都具有合理性。而信号的上升沿和下降沿时间越小,信号的高频分量会越来越多,信号带宽较大,此时必须考虑信号的完整性问题。

4.包处理性能计算

报文长度为65bytes,FPGA处理位宽为64bit,采用250M工作时钟,包处理性能是多少?

①包处理性能怎么算呢?在我看来,无非就是多少时间内读取了多少数量的数据

②那么题干中给了时钟频率250M,我们可以算出一个时钟周期的时间是1/250M 秒

③那么一个时钟周期FPGA能处理多少数据呢,我想应该是64bit,也就是说一个时钟周期的时间,即1/250M 秒,FPGA处理了64bit数据,而处理一个包的时钟个数为65x8÷64=8.1多,所以需要9个时钟,那么包处理性能就是250/9 Mbps

5.时钟类型

①全局时钟:全局时钟网络上的时钟信号,可以保证较小的信号偏斜(skew),即时钟信号到达各个触发器的时间尽可能接近,换句话说就是同步时钟,可预测性强

②多级逻辑时钟:不应该用多级组合逻辑去钟控PLD设计中的触发器,可靠性低

③行波时钟:一个触发器的输出用作另一个触发器的时钟输入,与电路有关的定时计算变得很复杂

④门控时钟:用于减少随时钟翻转进行多余的内部寄存器翻转从而将功耗降低的时钟

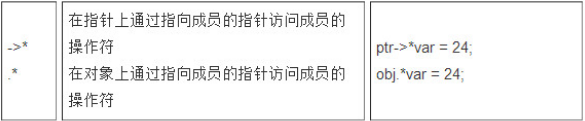

6.操作符优先级

第一级:

第二级:

第三级:

第四级:

第五级:

第六级:

第七级:

第八级:

之后逐级降低优先级:

第十五级:

第十六级:

7.8421码

8421码是中国大陆的叫法,8421码是BCD代码中最常用的一种,每个十进制数都用4位进行表示。例如45用8421码表示则是 01000101 ,前面的0100表示4,后面的0101表示5。

8.Verilog可综合的语句

①所有综合工具都支持的结构:always,assign,begin,end,case,wire,tri,aupply0,supply1,reg,integer,default,for,function,and,nand,or,nor,xor,xnor,buf,not,bufif0,bufif1,notif0,notif1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parameter

②所有综合工具都不支持的结构:time,defparam,$finish,fork,join,initial,delays,UDP,wait

③有些工具支持有些工具不支持的结构:casex,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task,while。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?