计算机结构

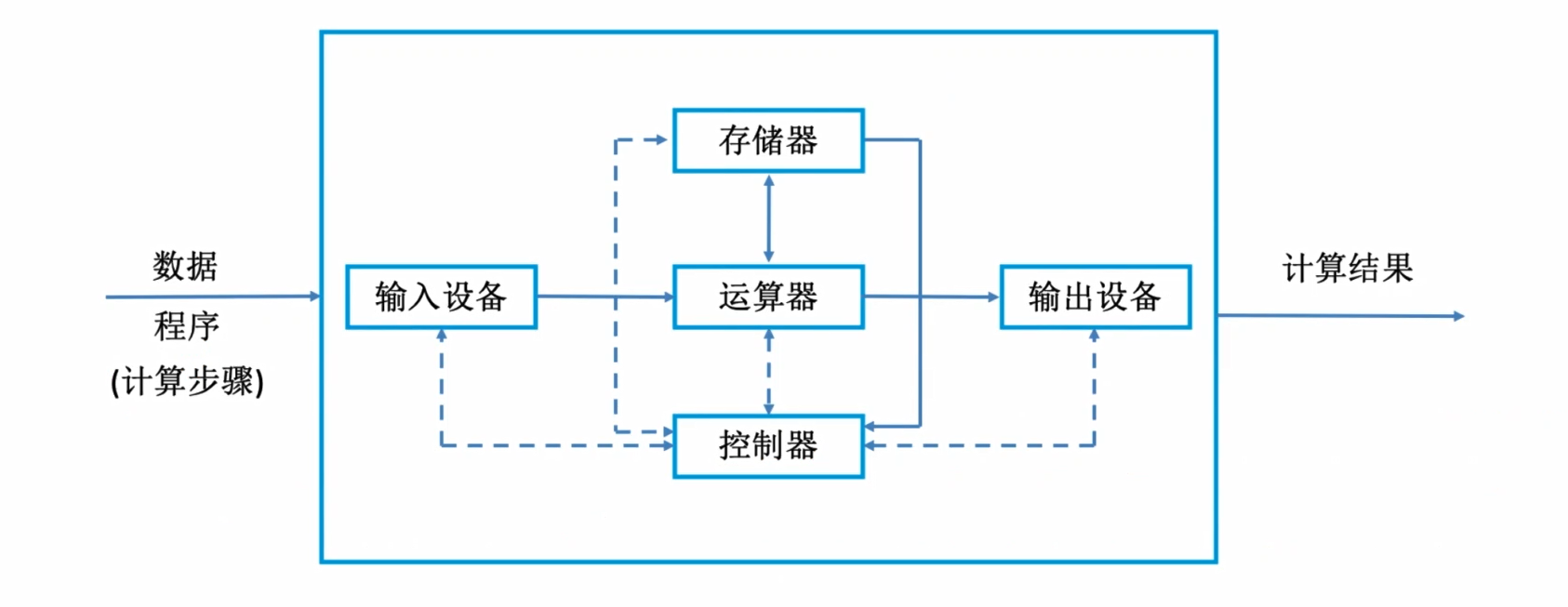

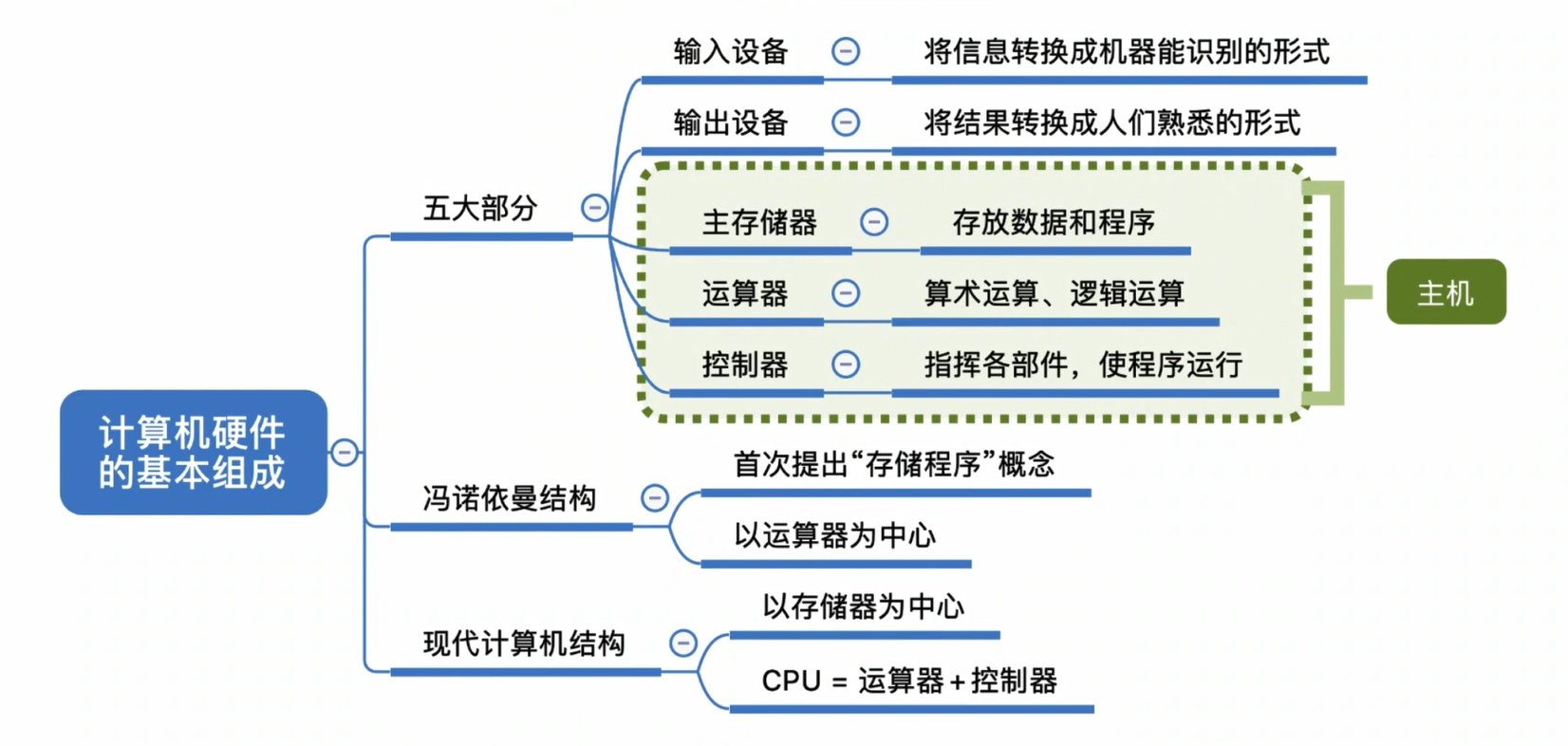

冯诺依曼结构

冯诺依曼结构中首次提出了“存储程序”的概念,即将指令以二进制代码的形式事先输入计算机的主存储器,然后执行在存储器中的首地址的第一条指令,此后便根据程序规定的次序执行其它指令,直到程序结束。

它的特点包括:

- 计算机由运算器、存储器、控制器、输入设备和输出设备这五大部件组成

- 指令和数据以同等地位存放于储存器中,并可按地址寻访

- 指令和数据均用二进制数表示

- 指令由操作码和地址码组成,操作码用来表示操作的性质,地址码用来表示操作数在存储器中的位置

- 指令在存储器内按顺序存放。通常,指令是按顺序执行的,在特定条件下,可根据运算结果或设定的条件改变执行顺序

- 机器以运算器为中心,输入输出设备与存储器间的数据传送通过运算器完成

世界上第一个采用冯诺依曼结构的计算机是 EDVAC

冯诺依曼结构的硬件框图如下

从输入设备输入的程序被称为软件,而大蓝框内的部分称为硬件。在计算机系统中,软件和硬件在逻辑上是等效的,即对于同一个功能,可以通过软件来实现,也可以通过硬件来实现。用软件实现的成本更低,但效率也更低,用硬件实现的成本更高,但效率也更高

例如我们可以设计一个电路用于乘法计算,但是我们也可以设计程序通过多次加法来实现,但是通过硬件的实现方式在效率上远远超过软件

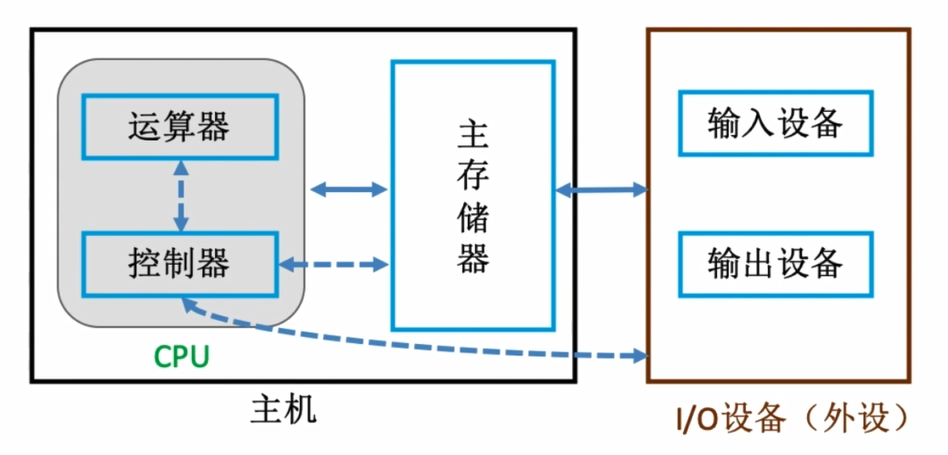

现代计算机结构

现代计算机通常以存储器为中心,即输入设备直接将数据存放到存储器中,而输出设备直接从存储器读取,这样就能让运算器专注于运算

由于运算器和控制器之间的逻辑关系十分紧密,因此将两者集合于同一个芯片上,即中央处理器(CPU)

现代计算机的结构框图如下

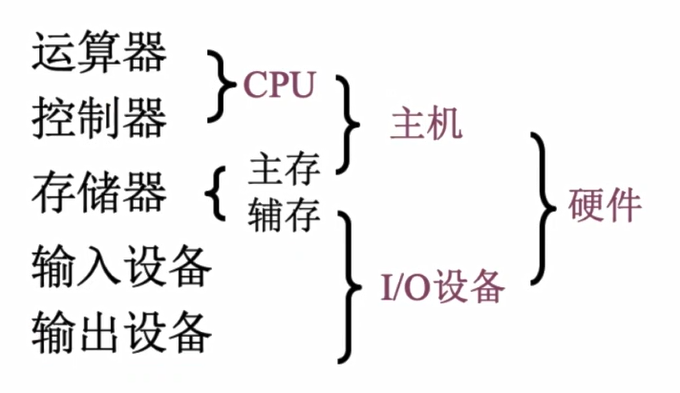

主存与辅存

主存又称内存,包括 ROM(只读存储器) 与 RAM(随机存储器)

RAM能够与CPU直接进行数据交换

辅存又称外存,包括磁盘,磁带,光盘等。CPU无法直接与辅存联系,只有把辅存里的内容读取到主存才能由CPU进行计算

考点总览

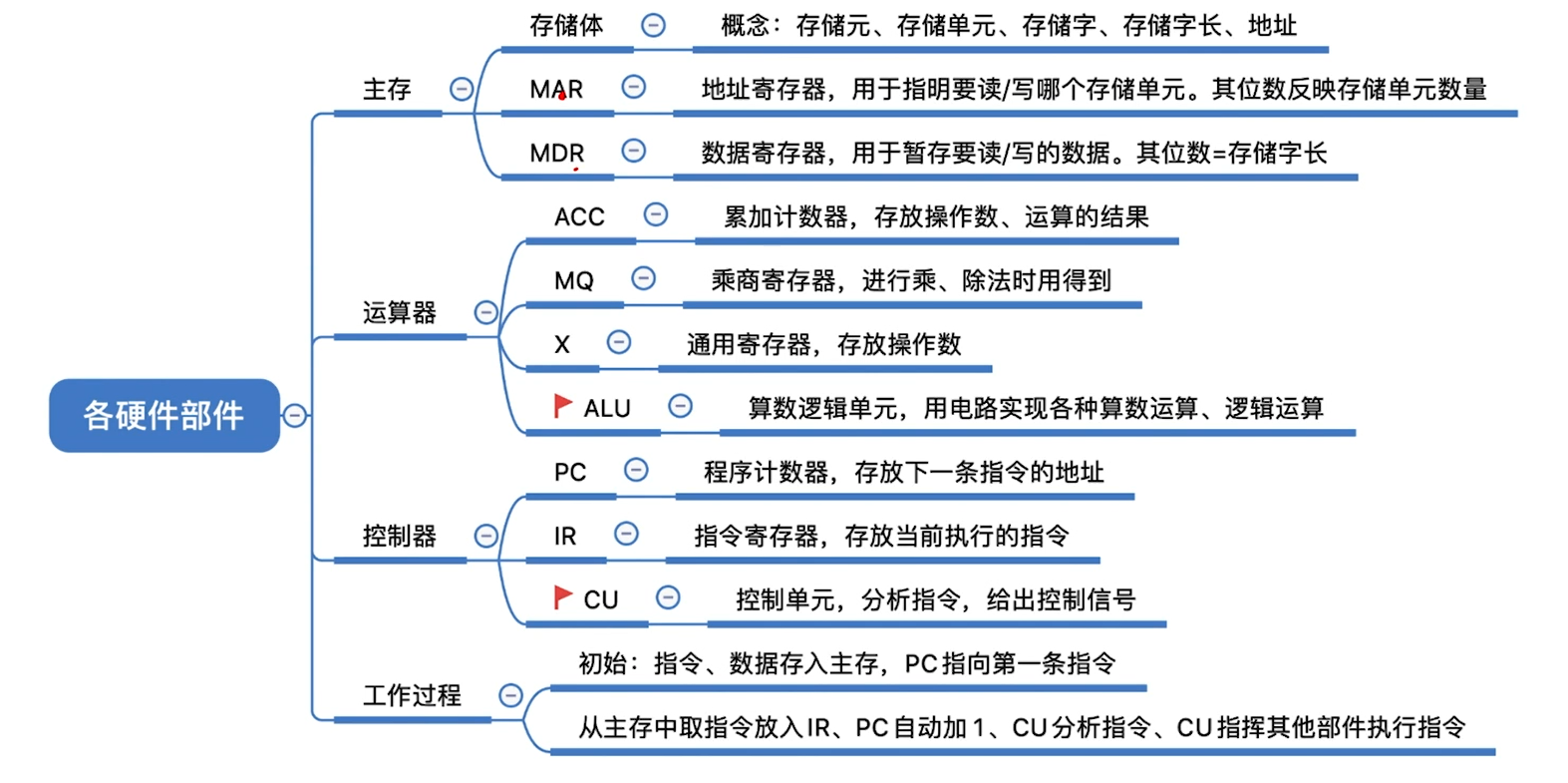

计算机硬件

主存储器

主存储器中存放数据的原件称为存储体,除此之外,还包括两个重要的寄存器,即 MAR(存储地址寄存器) 和 MDR(存储数据寄存器)

CPU在读取数据时,先将数据的地址写入 MAR 中,然后根据 MAR 上的地址找到对应的数据,写入到 MDR 中,这时CPU便可以向 MDR 读出数据

不同的地址在存储体中对应了不同的存储单元,存储单元中的二进制代码组合被称为存储字,其位数被称为存储字长

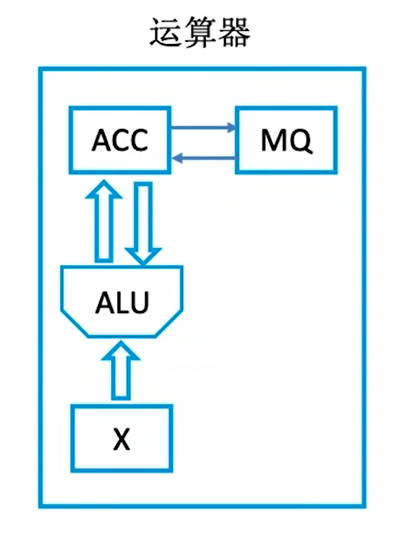

运算器

运算器用于实现算数运算和逻辑运算,例如加减乘除,与非运算

ACC: 累加器,用于存放操作数或运算结果

MQ: 乘商寄存器,在乘除运算时,用于存放操作数或运算结果

X: 通用的操作数寄存器,用于存放操作数

ALU: 算数逻辑单元,通过内部复杂的电路实现算数运算、逻辑运算

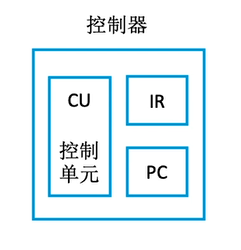

控制器

CU: 控制单元,分析指令,给出控制信号

IR: 指令寄存器,存放当前执行的指令

PC: 程序计数器,存放下一条指令地址,并能自动加一

执行一条指令需要三个阶段

- 取指令(PC)

- 分析指令(IR)

- 执行指令(CU)

其中一二步骤称为取值,第三步称为执行

考点总览

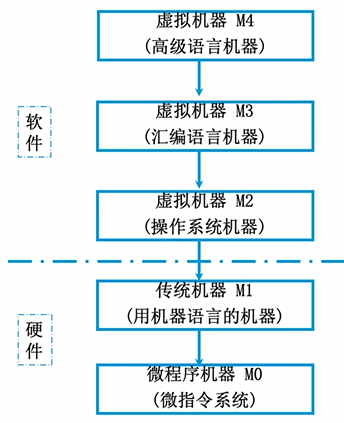

计算机系统层次结构

微指令

计算机只能识别机器语言,计算机在执行二进制机器指令时,需要把机器指令细分为更小的微指令

系统层次

使用高级语言编程时,先由编译程序将代码翻译成汇编语言程序,再通过汇编程序翻译成机器语言程序供计算机执行。上图虚线即为操作系统,它向上提供"广义指令",即系统调用,向下执行二进制机器指令,再由硬件来执行微指令

对于该层次结构,每个下层都是上层的基础,而每个上层都是对下层的扩展

编程语言

编程语言可分为高级语言,汇编语言,机器语言

翻译编程语言的程序被称为翻译程序

其中编译程序负责把高级语言一次性全部翻译为汇编语言

汇编程序负责把汇编语言翻译成机器语言

解释程序负责把高级语言翻译成机器语言,并且每翻译一句就立即执行一句

考点总览

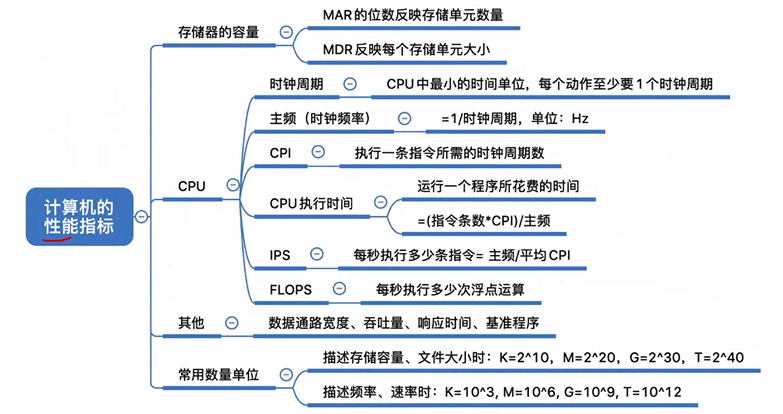

计算机性能指标

存储器指标

存储器的主要指标是总容量,总容量可以通过以下公式计算

总容量(bit) = 存储单元个数 × 存储字长

例如:若 MAR 位数为32位,MDR 为8位。则 MAR 总共能表示2^32个地址,即存储单元个数为 2^32 个,MDR 为8位表示存储单元字长为8位,因此总容量为(2^32)×8 bit=4GB

需要注意的是,MAR虽然有32位,但是并不意味着每个地址都对应一个存储单元,而是MAR最多只能对应2^32个存储单元,因此上面的计算结果实际上是这台计算机最大支持的存储容量。而在题目中,如果没有特别说明,一律认为MAR没有浪费,即存储单元个数就是MAR的最多支持个数

CPU性能指标

主频与时钟周期

以英特尔CPU为例,有一个"i5-9400F 2.9GHz6核6线程"的CPU,其中2.9GHz即为CPU的主频

主频是CPU内数字脉冲信号震荡频率。两次脉冲信号开始时间的时间差称为"CPU时钟周期",CPU主频与时钟周期的关系如下

CPU主频(Hz) = 1 / CPU时钟周期(s)

主频决定了CPU执行的速度

CPI

除了主频之外,CPI也会影响CPU的性能。

CPI是执行一条指令所需要的时钟周期数,CPI越大表示执行指令越慢

例如取值指令只需要9个微指令,而乘法指令则需要11个微指令,因此同一个CPU执行不同的指令所需要的时钟周期数是不同的。甚至同一个CPU执行同一个执行,其CPI也可能是不同的,因为它还会受到硬件状态影响。例如当内存负荷较大时,从内存中读取数据就需要更多的时钟周期数

执行一条指令的耗时可以通过以下公式计算

耗时 = CPI × CPU时钟周期

例如:某CPU主频为 1000Hz,一段程序包含100条指令,平均CPI为3,则程序的执行时间为

100 × 3 × (1 / 1000(Hz)) = 0.3(s)

IPS

IPS表示每秒能够执行多少条指令,它是执行一条指令耗时的倒数,即

IPS = 1 / (CPI × CPU时钟周期数) = 主频 / CPI

FLOPS

FLOPS表示每秒能够执行多少次浮点运算

系统整体性能指标

数据通路带宽

指数据总线一次所能并行传送的二进制信息位数

计算机中,IO设备与内存,内存与CPU的数据传输都是通过数据总线进行的

吞吐量

表示系统在单位时间内处理请求的数量

该指标受到CPU、内存等因素影响,通常用于描述网站服务器性能。系统从收到一次HTTP请求到做出响应所需要的时间就是处理请求的时间,而一秒内处理请求的数量就是吞吐量

响应时间

响应时间指计算机从用户发出请求开始,到系统对该请求做出响应并得到结果所需要的时间。例如用户打开文件夹,从双击鼠标开始到弹出新窗口所需要的时间就是响应时间

基准程序

基准程序是用于测量计算机性能的一种程序。由于上面的各种指标都是静态量,难以用于对比计算机性能

基准程序就是俗称的"跑分软件",它在本质上就是一段包含各种指令的代码,通过运行这些指令,来得到系统性能评分

考点总览

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?