学习quartus 和 verilog时离不开仿真工具,今天实现了modelsim仿真波形图的功能。

下载modelsim

对于新手而言,不需要破解ModelSim,可以用免费的ModelSim-Altera Starter Edition,也就是入门版,可以仿真一万行可执行代码(这一万行是指不包括注释,纯的代码)。只有非常大的设计才需要用ModelSim-Altera Edition或者ModelSim-SE版,下载链接:官网下载

在安装的时候,选择 Modelsim-Altera Start Edition(Licence is not required),然后按照正常流程安装。

编写设计和TEST_branch

以四位加法器为例:

下面展示 .V文件。

module count4(out,reset,clk);

output[3:0] out;

input reset,clk;

reg[3:0] out;

always @(posedge clk)

begin if (reset) out<=0; //同步复位

else out<=out+1; //计数

endendmodule

仿真文件是.vt格式

`timescale 1ns/1ns

`include "count4.v"

module coun4_tp;

reg clk,reset; //测试输入信号定义为 reg 型

wire[3:0] out; //测试输出信号定义为 wire 型

parameter DELY=100;

count4 mycount(out,reset,clk); //调用测试对象

always #(DELY/2) clk = ~clk; //产生时钟波形

initial

begin //激励信号定义

clk =0; reset=0;

reset=1;

reset=0;#DELY

#DELY #(DELY*20) $finish;

end

//定义结果显示格式

initial $monitor($time,,,"clk=%d reset=%d out=%d", clk, reset,out);

endmodule

编译成功后打开modelsim

仿真

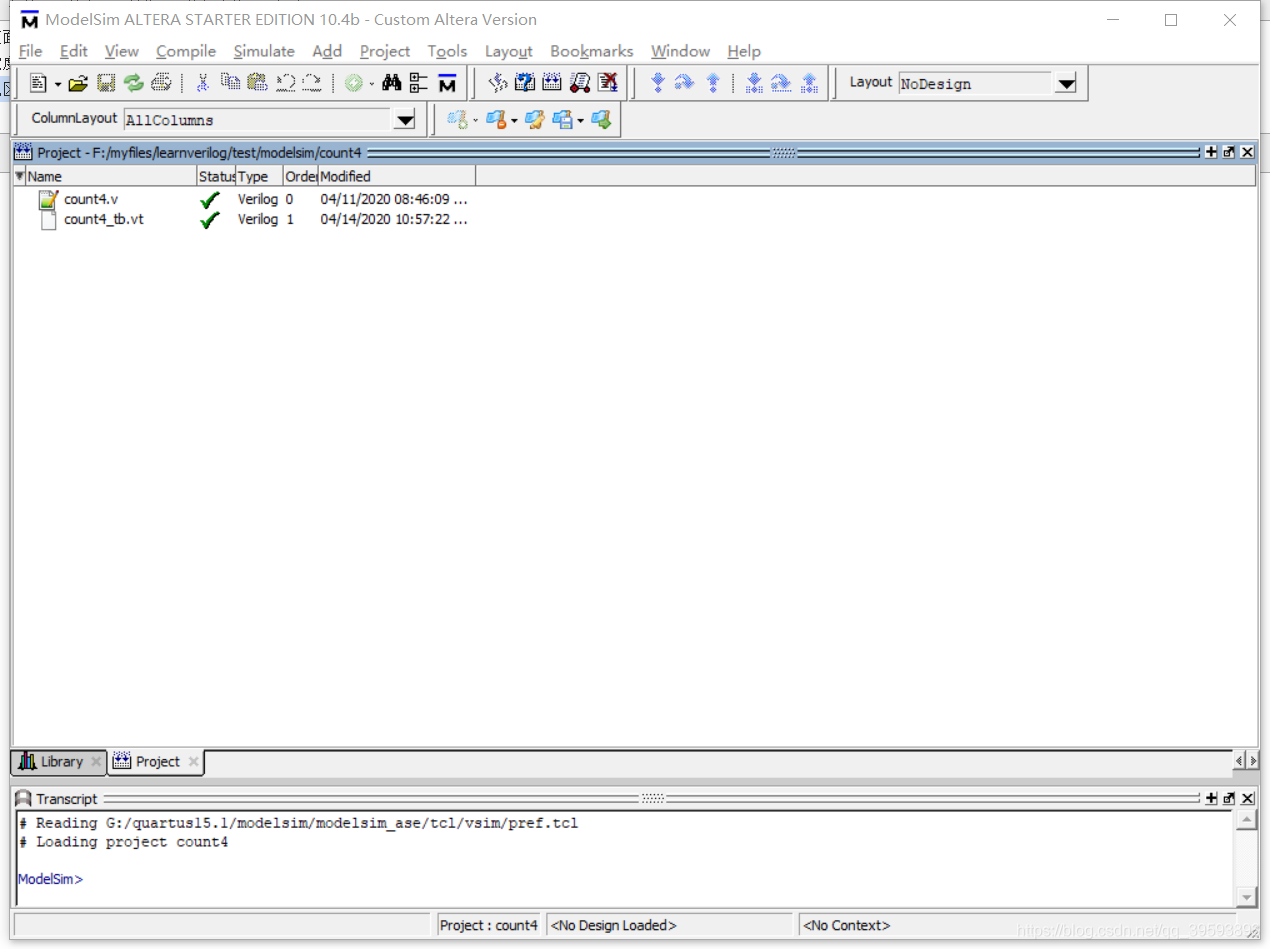

1.在modelsim中新建工程,导入count4和count4_tb,编译这两个文件。

2.在library中的work目录找到count4_tb,右击选择“simuate”,再右击count4_tb-add to wave->all item in region

3.修改仿真时间

4.在Transcript中输入“run”即可运行。

7981

7981

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?