FPGA采用Xilinx pynq Z2开发板。基于V2.5版本开发

OverView

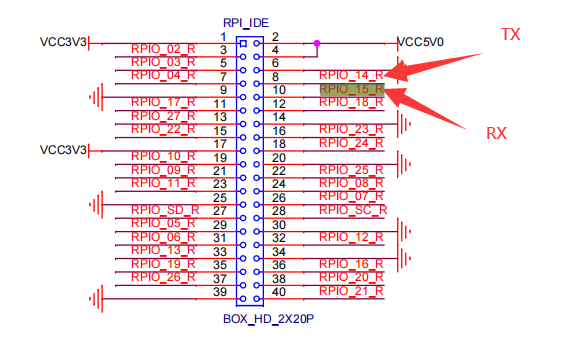

uart端口映射

BUG调试记录

- 2024.1.7

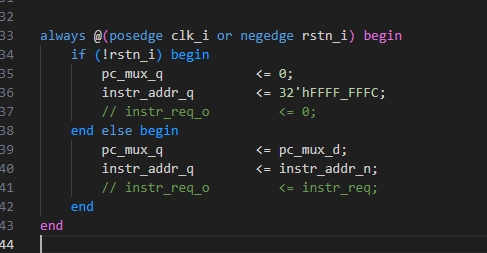

复位状态导致取指时序错误

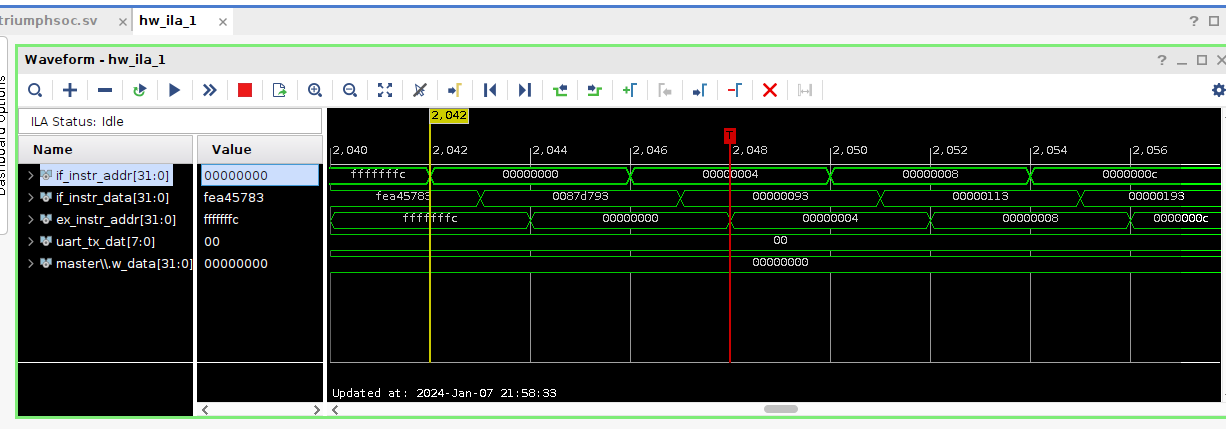

错误波形:

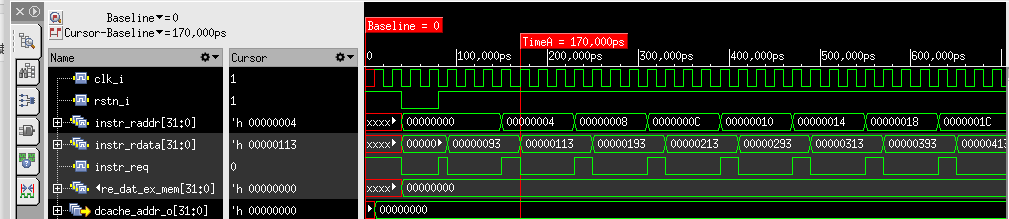

正确波形

问题代码:

- 2024.1.9

clock_wizard设置输入时钟是输出时钟的2^n倍,输出时钟的占空比才是50%

即使clock_wizard设置占空比是50%,如果不是2^n倍,实际占空比也不会是50%,甚至也会影响其他信号的占空比。

- 2024.1.10

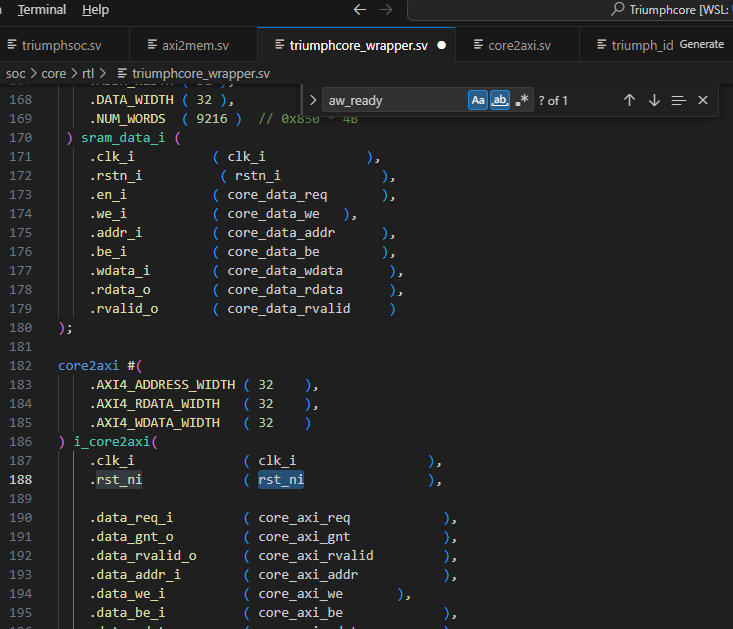

复位信号赋值错误导致core2axi中状态机CS始终不变化

w_valid只拉高一个周期,拉了很多波形出来,本来以为是aw_ready_i的组合逻辑路径较长,FPGA综合时序的问题,结果发现aw_ready_i在和aw_ready同一cycle拉高,然后就想到状态机未跳转的问题,结果一来出来发现NS变化,CS不变,那就是时钟和复位的问题了,时钟不太可能有问题,那就是复位的问题,然后一看代码,傻眼了。。

欸,改吧改吧。

后来想,为啥软仿没查出来呢?

软仿复位信号是Z,没有下降沿触发,CS默认也是0。

XilinxpynqZ2FPGAV2.5开发中的调试与问题解决

XilinxpynqZ2FPGAV2.5开发中的调试与问题解决

本文详细记录了使用XilinxpynqZ2开发板在V2.5版本中遇到的UART映射、取指时序错误、clock_wizard设置和复位信号问题。作者通过BUG调试揭示了复位信号对状态机的影响,以及为何软仿未能捕捉到问题的原因。

本文详细记录了使用XilinxpynqZ2开发板在V2.5版本中遇到的UART映射、取指时序错误、clock_wizard设置和复位信号问题。作者通过BUG调试揭示了复位信号对状态机的影响,以及为何软仿未能捕捉到问题的原因。

2621

2621

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?