基于近期的工作,先暂时做个记录,记录一下对高速PCB板进行仿真的过程。整个工作过程基本按照目录进行。

1、Cadence Allegro和Sigrity的安装及破解

整套软件的安装基于大佬吴川斌的博客:Cadence Orcad Allegro Sigrity相关软件资源下载分享 持续更新 敬请关注。

我下载的是Cadence 2017.4和Sigrity 2019,Cadence各安装包详细如下:

下载阿里狗破戒大师打开如下:

在该界面,导入安装包路径,如D:\Cadence_install和安装路径如D:\,点击下一步即可自动安装,破解。安装完成后整个软件安装于自动创建的D:\Cadence文件夹下。

但是现在还只是第一步,要顺滑地使用,特别重要的是安装好更新补丁,不然会出现各种各样奇奇怪怪的问题。安装更新补丁在阿里狗下一个界面完成。

最后要安装的是Sigrity,否则Allegro Sigrity SI中无法使用SPEED2000和PowerSI等组件,报出Failed to run the SI/PI analysis because the PowerSI executable could not be found。。。的错误。

2、Allegro Sigrity进行信号完整性仿真分析

信号完整性问题主要是在高频信号传输过程中,信号互联已经不能由简单的集总元件表示,此时在传输过程中电压电流信号质量会受到很大影响,从而导致出现噪声、干扰和时序等问题。典型的信号质量问题包括有:过冲,回冲,振铃和边沿单调性等,造成他们的原因主要集中在信号的反射,串扰和抖动等。为了尽可能减小这些影响,高速PCB设计之前最好先进行仿真,我工作时做的第一块板就比较愣头青,以为参考原厂的参考设计即可,但是只要有一点不符合规范,就会导致最后测试的性能差距较大。下面是通过Cadence仿真的基本流程。

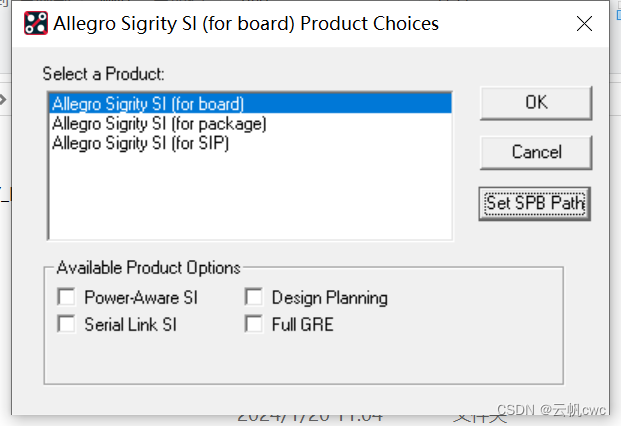

首先打开Signal integrity 2017.4,选择Allegro Sigrity SI(for board),第一次使用需要Set SPB Path,选择Cadence安装位置即可,例如:D:\Cadence\Cadence_SPB_17.4-2019

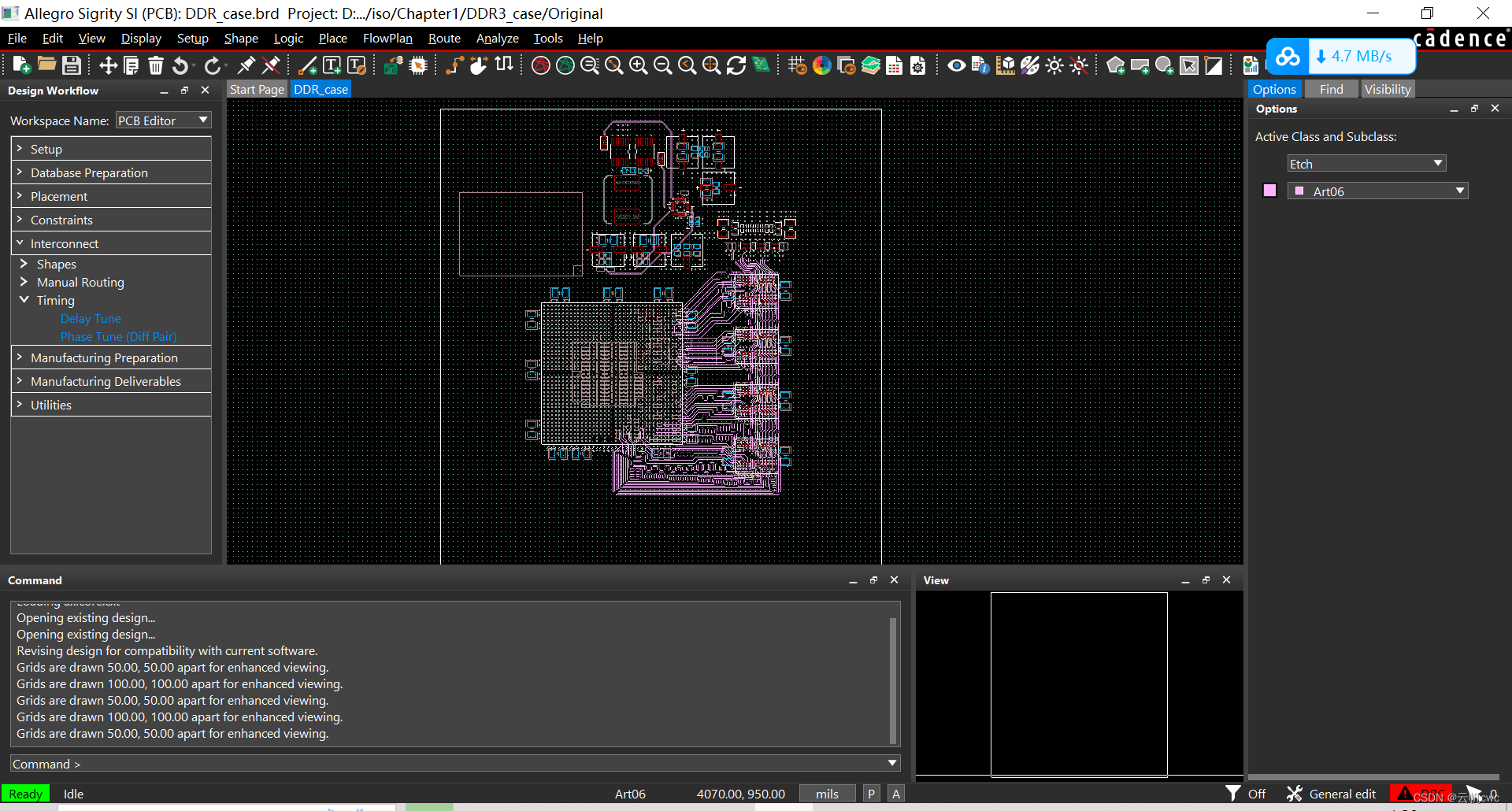

打开界面如下图所示:

下面进行以简单的传输线阻抗和反射分析仿真为例,展示通过Allegro Sigrity SI实现一系列信号完整性仿真。

2.1、传输线阻抗与反射分析仿真

在Allegro Sigrity SI环境下,点击Tools-Topology Editor,进入到Sigplorer拓扑仿真环境中,也可以直接从Sigplorer进入,此时界面如下所示:

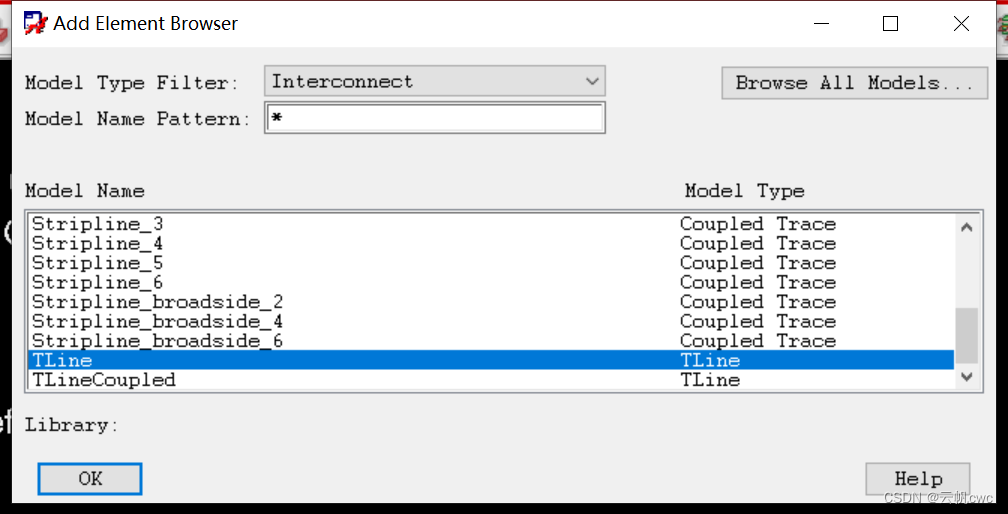

通过Add Element添加OUT,IN和Line,如下图所示:

放置好元件后,进行连线和设置,点击OUT下的pulse进入到信号设置如下图:可自定义设置信号频率和Pattern。

单击TLine,配置其阻抗和传输延时,延时模式这可选择时间或是传输线长度,

同时延时可设置为多个值,用于仿真对比。

在设置完成后经常会有Sigplorer卡死问题,这是由于输入法设置的问题,将首选输入法设置为英文输入法即可流畅使用。

设置完成后,选择Analyze-Simulate或是 此图标,开始进行仿真

此图标,开始进行仿真

弹出的对话框显示进行三次仿真,这个与设置了三组传输延时时间一致,点击continue,仿真结束后右下角显示Ready,左下角右键Simulate结果,查看仿真波形

下面是三种仿真在终端输出的波形图,可以看到传输线越长,由于反射的影响波形越糟糕。

在拓扑中增加终端电阻进行匹配,如下图所示:

仿真结果显示反射的影响大大减小

这只是简单的拓扑仿真,后续针对我的PCB板进行仿真才是实际工作的需要。

6053

6053

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?