Sigrity进行阻抗和串扰仿真

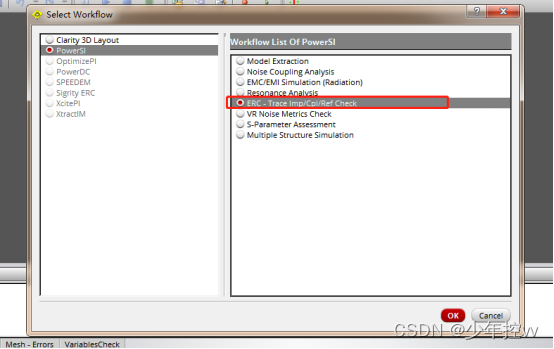

一、首先打开power SI,然后选择工作环境,file->switch workflow->ERC-Trace imp如图

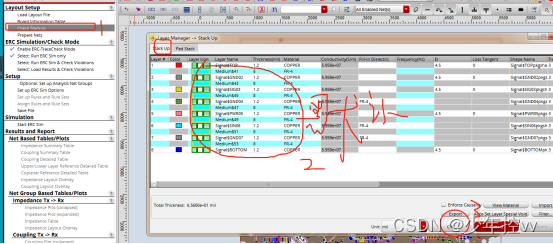

二、打开后,然后进行加载你的PCB文件(candece的brd文件),非cadence需要转化才行;打开后如图:

三、首先检查下层叠结构,注意PCB的层叠结构对阻抗的仿真非常重要!!!,否则差的很远,接下来会做一个对比;下面做DDR和CPU之间的阻抗和串扰仿真,先做一个默认的大家看下结果,层叠结构设置如图,现在只是用默认值;

四:设置好层叠结构后,选择要仿的芯片位号即可,setup ->option:set up…点击后出来的是TX,点击next后就会弹出一样的框进行选择RX;如图:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4286

4286

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?