1 绪论

1.1 设计背景

集成电路设计(Integrated circuit design, IC design),亦可称之为超大规模集成电路设计(VLSI design),是指以集成电路、超大规模集成电路为目标的设计流程。集成电路设计涉及对电子器件(例如晶体管、电阻器、电容器等)、器件间互连线模型的建立。所有的器件和互连线都需安置在一块半导体衬底材料之上,这些组件通过半导体器件制造工艺(例如光刻等)安置在单一的硅衬底上,从而形成电路。

近些年来,集成电路技术发展迅猛,促使半导体技术不断地发展,半导体技术正在进入将整个系统整合在单一晶片上的时代。故对VLSI的版图设计的要求也越来越高。Tanner软件可提供完整的集成电路设计环境,帮助初学者进入VLSI设计领域。本设计采用Tanner Tools Pro 工具,对逻辑为Y=AB+C进行电路设计与仿真、版图设计与仿真,在报告中给出电路图、版图与仿真结果。

1.2 设计目标

设计目标逻辑:Y=AB+C

用CMOS工艺设计逻辑为Y=AB+C的电路和版图。因为CMOS是天然的反逻辑输出,所以需要先设计出逻辑为/Y=/(AB+C)的电路,再将输出接入一个CMOS反相器实现逻辑功能。

设计电路图(Schematic)时,N网络A与B串联且与C并联,P网络A与B并联且与C串联,在N和P网络的交界节点接入反相器后引出输出Y。

设计版图(Layout)时,在P型衬底(P-Sub)上进行制作,所以N-MOS管可以直接掺杂制作,而P-MOS管需要先制作一个N阱(N-Well),并在N阱里制作P-MOS管。整个设计比较简单,仅仅使用单层金属布线(Meteal)。

导出电路和版图网表(spice)文件,用Tspice软件进行仿真波形,分析电路和版图是否设计正确性以及其性能如何。在LVS验证中匹配电路原理图和版图逻辑和尺寸匹配性,完成整个设计过程。

2 Y=AB+C 的电路原理图设计与仿真

2.1 电路原理图设计

目标逻辑Y=AB+C,设计电路其功能为当C=1时,Y=1;当C=0而B和C不同时为1时,Y=0;当C=0,A和B都为1时,Y=1。

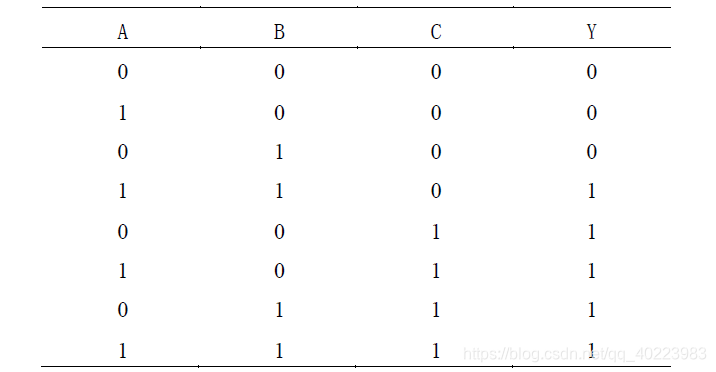

以上电路功能符合设计的目标逻辑Y=AB+C,所以此电路图(Schematic)设计正确,下面给出其真值表,如下表所示:

使用S-Edit软件进行电路图(Schematic)绘制,在Schematic Model下绘制电路图(Schematic),首先从Symbol Browser中导出N-MOS管和P-MOS管,然后绘制InputPort和OutPort,最后通过Wire线进行连接,如下图所示;

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2993

2993

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?