本章目录:

1. MCU

微控制单元 (Microcontroller Unit ; MCU) ,又称单片微型计算机 (Single Chip Microcomputer )或者单片机,是把中央处理器(Central Process Unit;CPU)的频率与规格做适当缩减,并将内存(memory)、计数器(Timer)、USB、A/D 转换、UART、PLC、DMA 等周边接口,甚至 LCD 驱动电路都整合在单一芯片上,形成芯片级的计算机。

CPU(Central Processing Unit,中央处理器)发展出来三个分枝,一个是 DSP(Digital Signal Processing/Processor,数字信号处理),另外两个是 MCU(Micro Control Unit,微控制器单元)和 MPU(Micro Processor Unit,微处理器单元)。

2. AXI

AXI(Advanced extensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA3.0中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。AMBA4.0 将其修改升级为 AXI4.0。

AMBA4.0 包括 AXI4.0、AXI4.0-lite、ACE4.0、AXI4.0-stream。

AXI 协议是基于 burst 的传输,并且定义了以下 5 个独立的传输通道:

读地址通道、读数据通道、写地址通道、写数据通道、写响应通道。

地址通道携带控制消息,用于描述被传输的数据属性;数据传输使用写通道来实现 master 到 slave 的传输,slave 使用写响应通道来完成一次写传输;

读通道用来实现数据从 slave 到 master 的传输。

AXI 使用基于 VALID/READY 的握手机制数据传输协议,传输源端使用 VALID 表明地址/控制信号、数据是有效的,目的端使用 READY 表明自己能够接受信息。

读/写地址通道:读、写传输每个都有自己的地址通道,对应的地址通道承载着对应传输的地址控制信息。

读数据通道:读数据通道承载着读数据和读响应信号包括数据总线和指示读传输完成的读响应信号。

写数据通道:写数据通道的数据信息被认为是缓冲(buffered)了的,master 无需等待 slave对上次写传输的确认即可发起一次新的写传输。写通道包括数据总线(8/16…1024 bit)和字节线(用于指示 8 bit 数据信号的有效性)。

写响应通道:slave 使用写响应通道对写传输进行响应。所有的写传输需要写响应通道的完成信号。

3. IIC

I2C 总线在物理连接上非常简单,分别由 SDA(串行数据线)和 SCL(串行时钟线)及上拉电阻组成。通信原理是通过对 SCL 和 SDA 线高低电平时序的控制,来产生 I2C 总线协议所需要的信号进行数据的传递。在总线空闲状态时,这两根线一般被上面所接的上拉电阻拉高,保持着高电平。

I2C 通信方式为半双工,只有一根 SDA 线,同一时间只可以单向通信。

I2C 总线上的每一个设备都可以作为主设备或者从设备。

I2C 总线上的主设备与从设备之间以字节(8 位)为单位进行双向的数据传输。

I2C 协议规定,总线上数据的传输必须以一个起始信号作为开始条件,以一个结束信号作为传输的停止条件。起始和结束信号总是由主设备产生(意味着从设备不可以主动通信。所有的通信都是主设备发起的,主可以发出询问的 command,然后等待从设备的通信)

4. SPI

SPI,是一种高速的,全双工,同步的通信总线。

(1)MOSI – 主器件数据输出,从器件数据输入

(2)MISO – 主器件数据输入,从器件数据输出

(3)SCLK –时钟信号,由主器件产生,最大为 fPCLK/2,从模式频率最大为 fCPU/2

(4)NSS – 从器件使能信号,由主器件控制,有的 IC 会标注为 CS(Chip select)

I2C 是多主机总线,通过 SDA 上的地址信息来锁定从设备;

SPI 只有一个主设备,主设备通过 CS 片选来确定从设备。

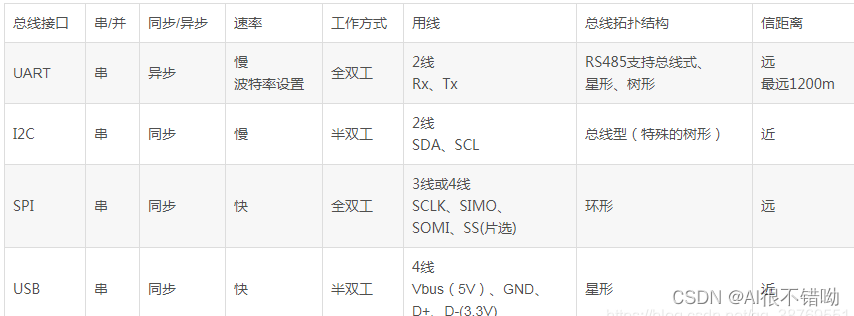

4.1 IIC、SPI、UART、CAN、RS485、USB、PCI速率比较

这个是后来加的,为什么呢?因为面试过程中问到了,我只知道谁谁谁是高速的,谁是低速的,不知道具体是多少,所以回来补一下子。

4.1.1 I2C

有三种模式:

S(标准模式)测量与控制场合,100kb/s

F(快速模式),速率为 400kb/s

Hs(高速模式),速率为 3.4Mb/s。

4.1.2 SPI

最大工作频率为 4M。

4.1.3 CAN

理论上,CAN总线在速率小于5K时,距离可达10000m;速率接近1Mbps时,距离小于40m。

现实中常用的高速CAN总线速率有500k或250k,低速CAN总线有125k和62.5k,传输距离在几米到几十米间。速率和传输距离的选择还有考虑硬件的要求。

4.1.4 USB

USB1.1:

-------低速模式(low speed):1.5Mbps

-------全速模式(full speed): 12Mbps

USB2.0:向下兼容。增加了高速模式,最大速率480Mbps。

-------高速模式(high speed): 25~480Mbps

USB3.0:向下兼容。

-------super speed :理论上最高达4.8Gbps,实际中,也就是high speed 的10倍左右。

4.1.5 UART

最大传输速率为10Mb/S。

4.2 SPI的四种工作模式

4.2.1 前序

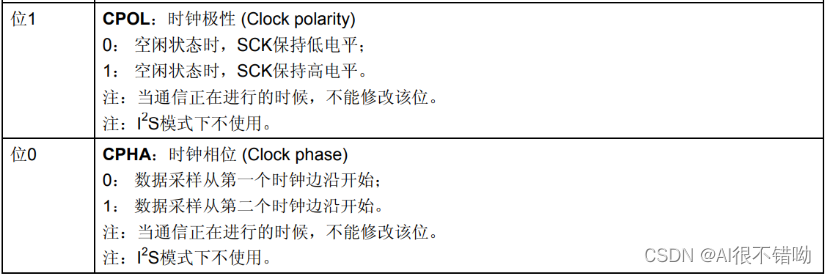

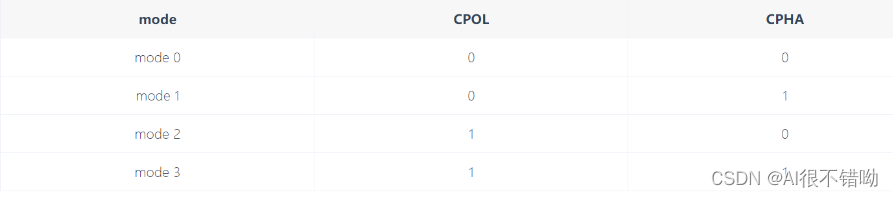

在了解spi的四种工作模式之前,我们需要了解一下 有关寄存器CPOL 和 CPHA 的配置,如下表所示:

展开细说一下它俩到底是干什么的呢?

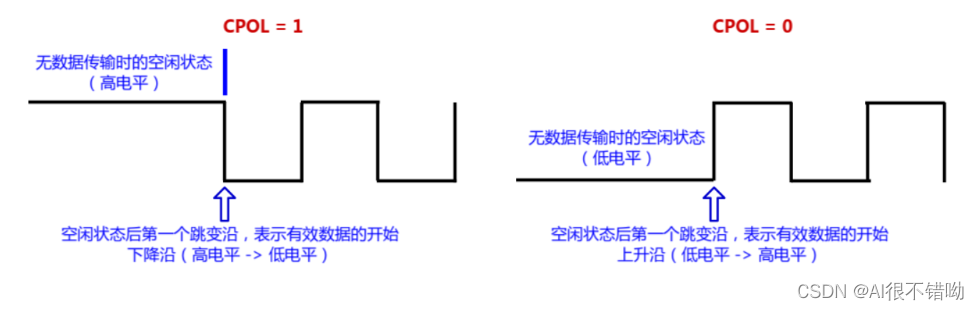

- CPOL就是决定SCLK这个时钟信号线,在没有数据传输的时候的电平状态。

CPOL=0:空闲状态时,SCLK保持低电平

CPOL=1:空闲状态时,SCLK保持高电平

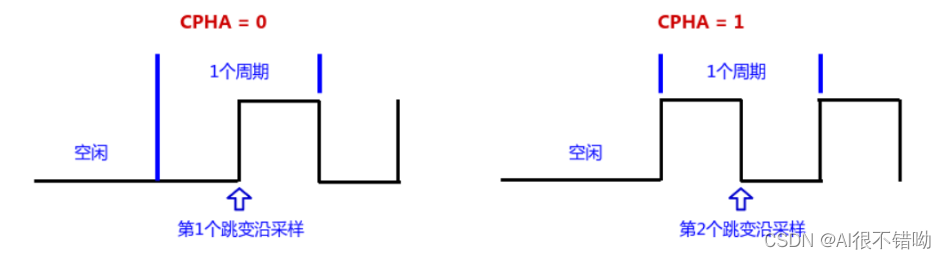

- CPHA就是决定数据位传输是从第一个时钟(SCLK)边沿开始,还是第二个从二个时钟(SCLK)边沿开始。

CPHA=0:数据从第一个时钟(SLCK)边沿开始采集

CPHA=1:数据从第二个时钟(SLCK)边沿开始采集

4.2.2 四种模式

总之,了解完这两个寄存器之后,SPI的四种模式其实就是这两个寄存器的组合:

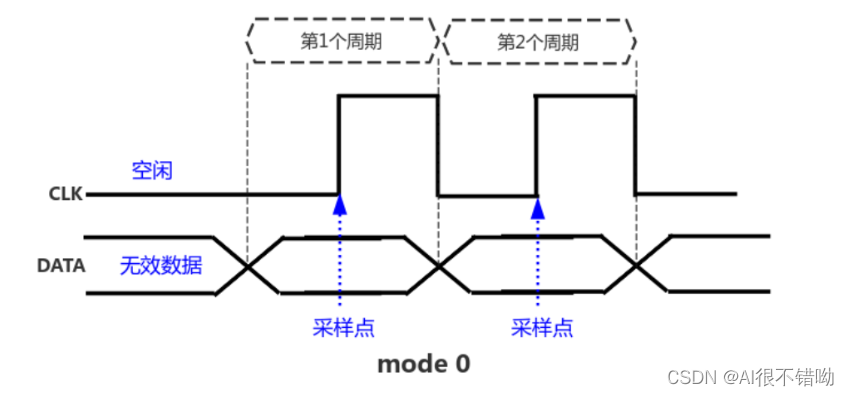

- 模式0(CPOL=0,CPHA=0)

CPOL = 0:空闲时是低电平,第1个跳变沿是上升沿,第2个跳变沿是下降沿

CPHA = 0:数据在第1个跳变沿(上升沿)采样

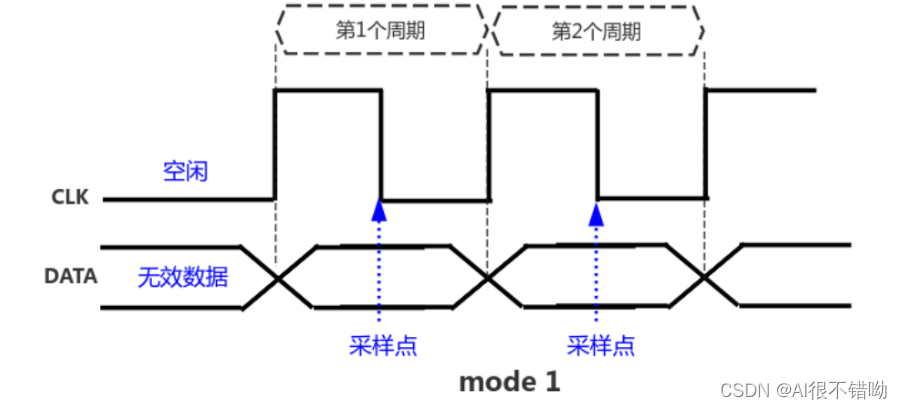

- 模式1(CPOL=0,CPHA=1)

CPOL = 0:空闲时是低电平,第1个跳变沿是上升沿,第2个跳变沿是下降沿

CPHA = 1:数据在第2个跳变沿(下降沿)采样

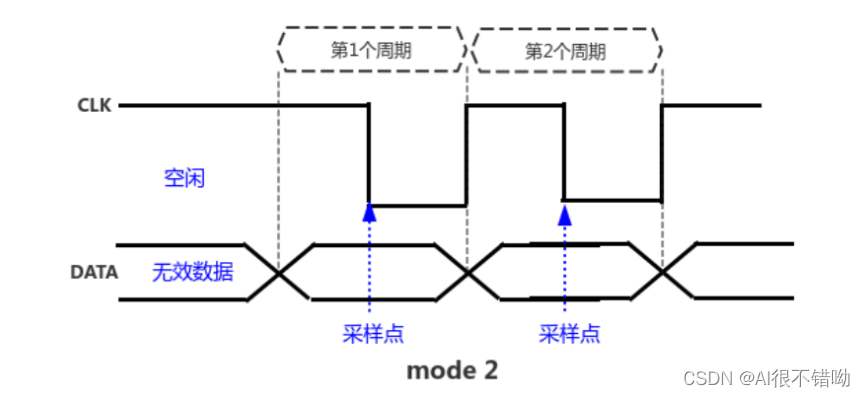

- 模式2(CPOL=1,CPHA=0)

CPOL = 1:空闲时是高电平,第1个跳变沿是下降沿,第2个跳变沿是上升沿

CPHA = 0:数据在第1个跳变沿(下降沿)采样

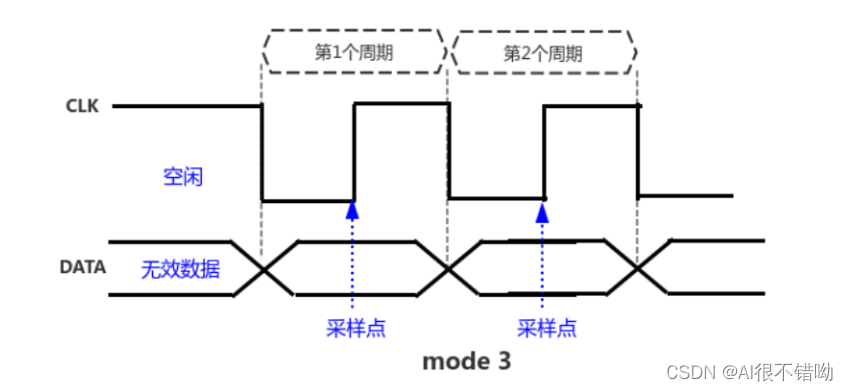

- 模式3(CPOL=1,CPHA=1)

CPOL = 1:空闲时是高电平,第1个跳变沿是下降沿,第2个跳变沿是上升沿

CPHA = 1:数据在第2个跳变沿(上升沿)采样

4.2.3 总结

不同的模式,SCLK空闲时间电平状态和数据采样起点不同!!!

5. GPIO

GPIO(英语:General-purpose input/output),通用型输入输出的简称,功能类似 8051 的P0—P3,其接脚可以供使用者由程控自由使用,PIN 脚依现实考量可作为通用输入(GPI)或通用输出(GPO)或通用输入与输出(GPIO),如当 clk generator, chip select 等。

接口至少有两个寄存器,即“通用 IO 控制寄存器”与“通用 IO 数据寄存器”。

数据寄存器的各位都直接引到芯片外部,而对这种寄存器中每一位的作用,即每一位的信号流通方向,则可以通过控制寄存器中对应位独立的加以设置。

6. JTAG 接口

6.1 概述

JTAG(Joint Test Action Group,联合测试工作组)是一种国际标准测试协议,主要用于芯片内部测试。标准的 JTAG 接口是 4 线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

6.2 功能

1.下载器,即下载软件到 FLASH 里。

2. DEBUG,在线进行调试。可以边运行观察硬件的信息,如查看内存。

3. 边界扫描,可以访问芯片内部的信号逻辑状态,还有芯片引脚的状态等等。

6.3 详解

具有 JTAG 口的芯片都有如下 JTAG 引脚定义:

TCK——测试时钟输入;

TDI——测试数据输入,数据通过 TDI 输入 JTAG 口;

TDO——测试数据输出,数据通过 TDO 从 JTAG 口输出;

TMS——测试模式选择,TMS 用来设置 JTAG 口处于某种特定的测试模式。

可选引脚 TRST——测试复位,输入引脚,低电平有效。

7. 指令执行步骤

几乎所有的冯·诺伊曼型计算机的 CPU,其工作都可以分为 5 个阶段:

-

取指令阶段

取指令(Instruction Fetch,IF)阶段是将一条指令从主存中取到指令寄存器的过程。程序计数器 PC 中的数值,用来指示当前指令在主存中的位置。 -

指令译码阶段

取出指令后,计算机立即进入指令译码(Instruction Decode,ID)阶段。在指令译码阶段,指令译码器按照预定的指令格式,对取回的指令进行拆分和解释,识别区分出不同的指令类别以及各种获取操作数的方法。在组合逻辑控制的计算机中,指令译码器对不同的指令操作码产生不同的控制电位,以形成不同的微操作序列;在微程序控制的计算机中,指令译码器用指令操作码来找到执行该指令的微程序的入口,并从此入口开始执行。 -

访存取数阶段

根据指令需要,有可能要访问主存,读取操作数,这样就进入了访存取数(Memory,MEM)阶段。此阶段的任务是:根据指令地址码,得到操作数在主存中的地址,并从主存中读取该操作数用于运算。 -

执行指令阶段

在取指令和指令译码阶段之后,接着进入执行指令(Execute,EX)阶段。此阶段的任务是完成指令所规定的各种操作,具体实现指令的功能。为此,CPU 的不同部分被连接起来,以执行所需的操作。例如,如果要求完成一个加法运算,算术逻辑单元 ALU 将被连接到一组输入和一组输出,输入端提供需要相加的数值,输出端将含有最后的运算结果。 -

结果写回阶段

作为最后一个阶段,结果写回(Writeback,WB)阶段把执行指令阶段的运行结果数据“写回”到某种存储形式:结果数据经常被写到 CPU 的内部寄存器中,以便被后续的指令快速地存取;在有些情况下,结果数据也可被写入相对较慢、但较廉价且容量较大的主存。许多指令还会改变程序状态字寄存器中标志位的状态,这些标志位标识着不同的操作结果,可被用来影响程序的动作。

8. 晶体与晶振的区别

1)晶振是有源晶振的简称,又叫振荡器。英文名称是oscillator。晶体则是无源晶振的简称,也叫谐振器。英文名称是crystal.

2)无源晶振(晶体)一般是直插两个脚的无极性元件,需要借助时钟电路才能产生振荡信号。常见的有49U、49S封装。

3)有源晶振(晶振)一般是表贴四个脚的封装,内部有时钟电路,只需供电便可产生振荡信号。一般分7050、5032、3225、2520几种封装形式。

1292

1292

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?