目录

3.硅nano-slot波导(很奇特,光在折射率低的地方进行了传输)

1.SOI脊型波导

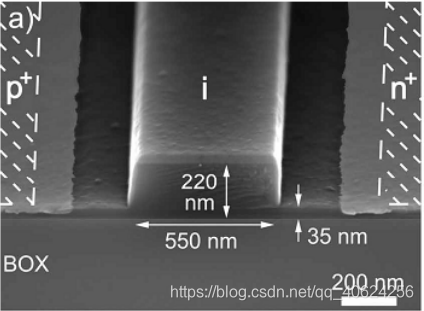

首先脊型波导与直波导的区别在于ridge wg不把silicon全刻到底,如下图留出来35nm的距离,这个留出来的slab可以把电子空穴对有个输运的作用。

ridge wg相对于strip wg而言,side wall比较小,损耗会降低,应用可以做PN junction做调制器,电信号控制光信号,但是尺寸会比strip wg大.

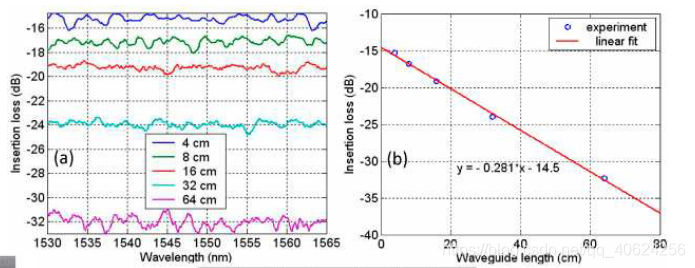

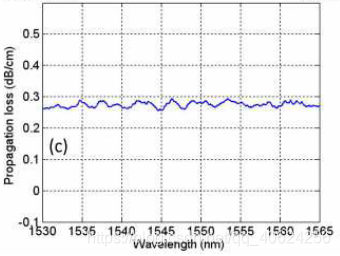

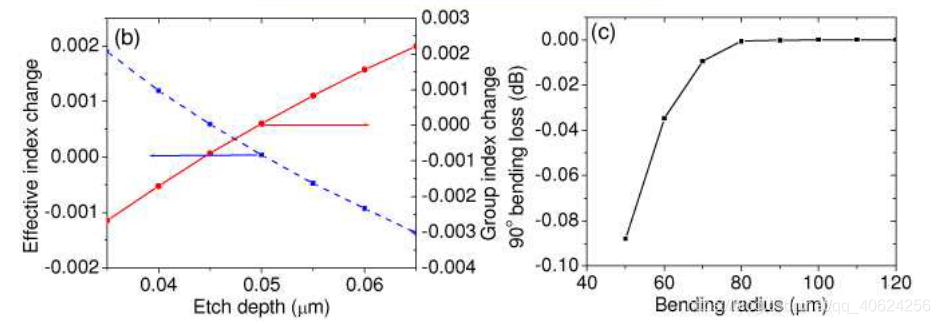

低损耗浅刻蚀SOI脊型波导的插入损耗,传播损耗,弯曲损耗:

这个结构可以用来做波导损耗测试,delayline,by the way光纤的偏转,弯曲都会改变传输光的相位。

这个结构可以用来做波导损耗测试,delayline,by the way光纤的偏转,弯曲都会改变传输光的相位。

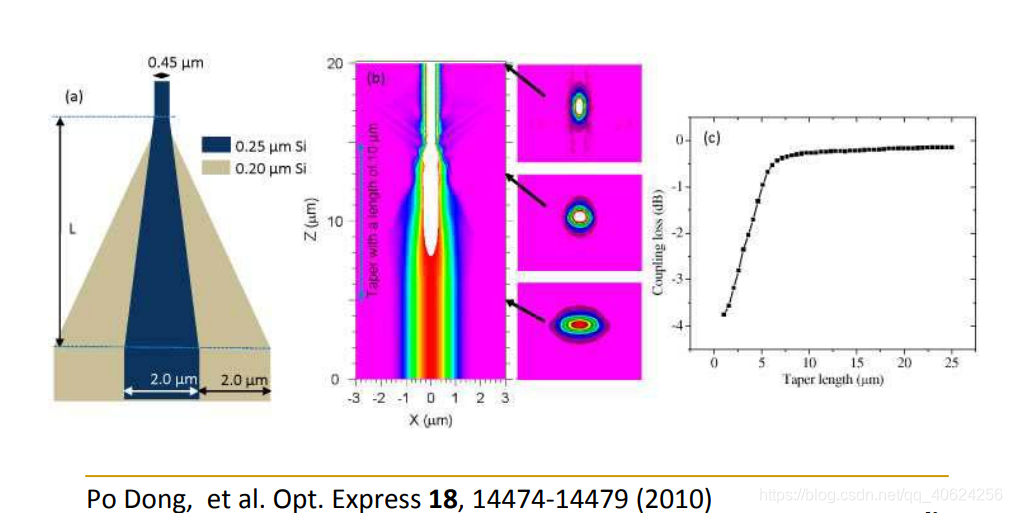

2.taper登场

strip wg 和ridge wg各有优点,前者的弯曲半径可以做到比较小,后者的损耗可以做到更小,所以可以在应用的过程中将他俩联合起来用,这时就需要taper,优化taper结构使两个wg连接损耗降低,比如优化两条边的形状,下图是线性的,可以试试二次曲线的形状。

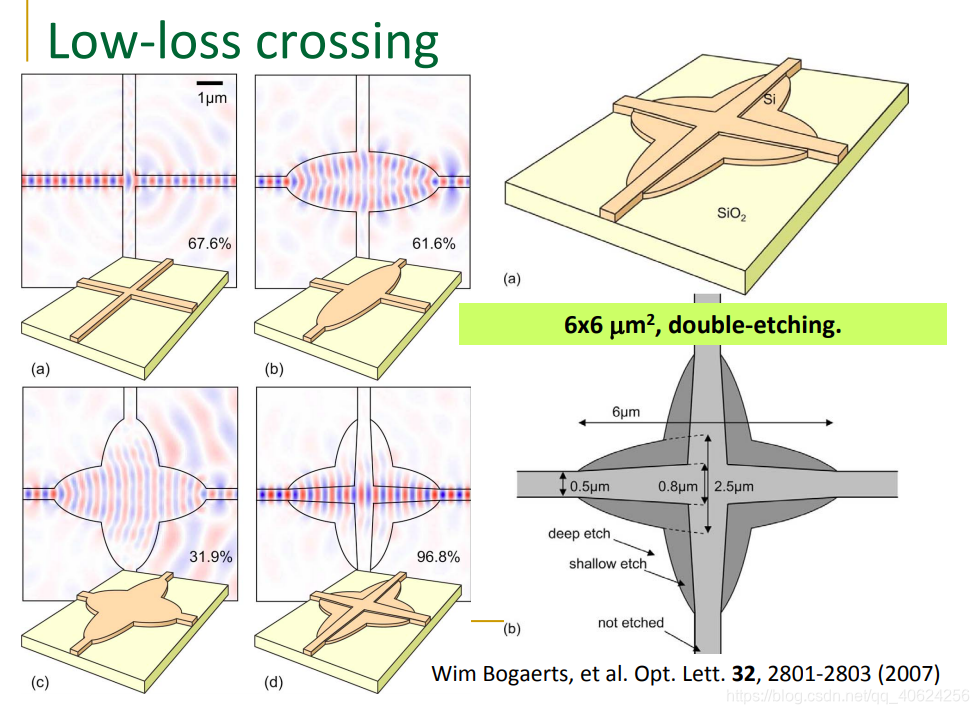

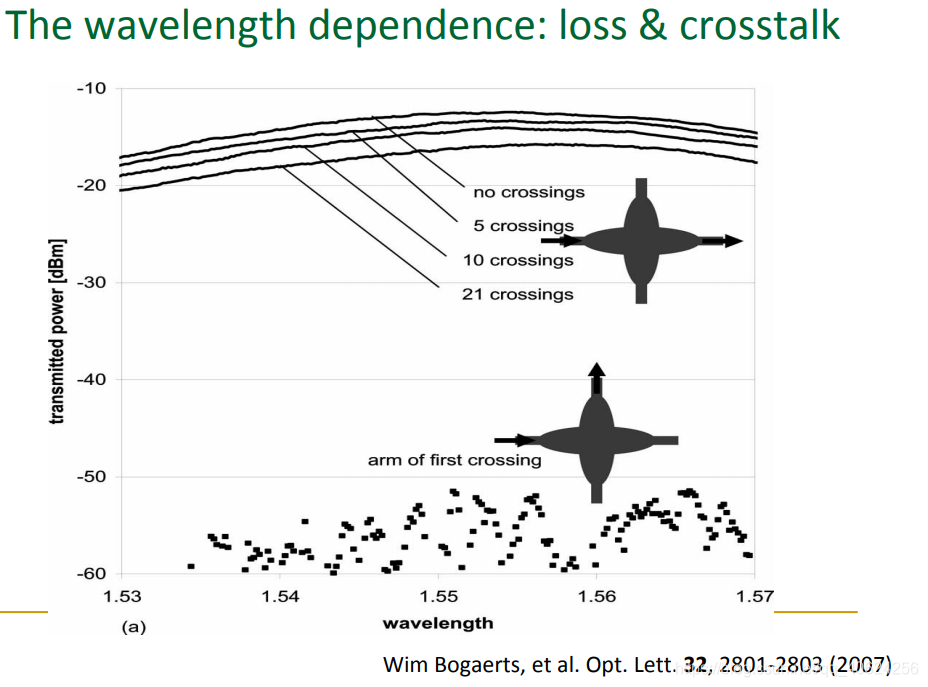

taper还可以用作crossing,光开关,如下图的crossing,要把crossing的损耗降到最低,因为有的光开关需要上百个 这样的crossing,目前可以做到98%左右的传输效率,要不断降低crossing的传输损耗

3.硅nano-slot波导(很奇特,光在折射率低的地方进行了传输)

by the way,光子晶体的应用中光子晶体光纤最成功,它没有非线性的色散,可以传输高功率。

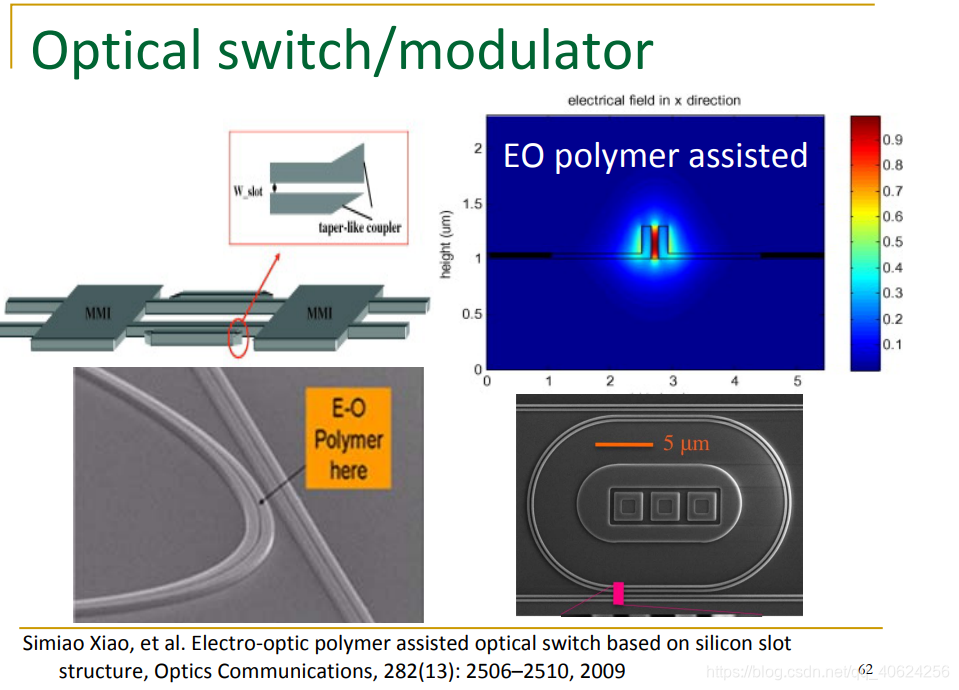

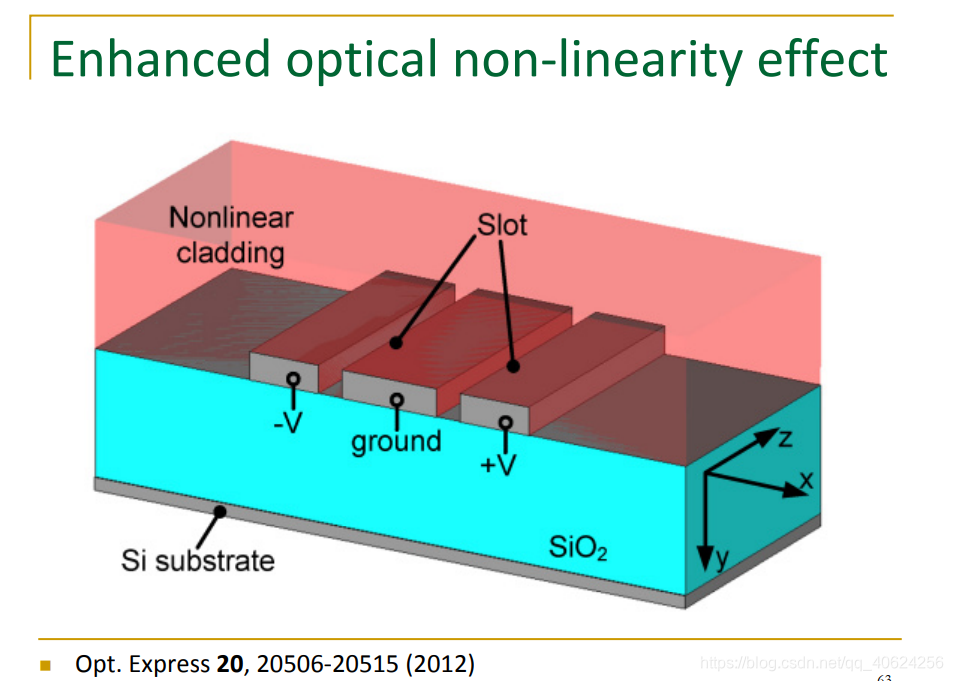

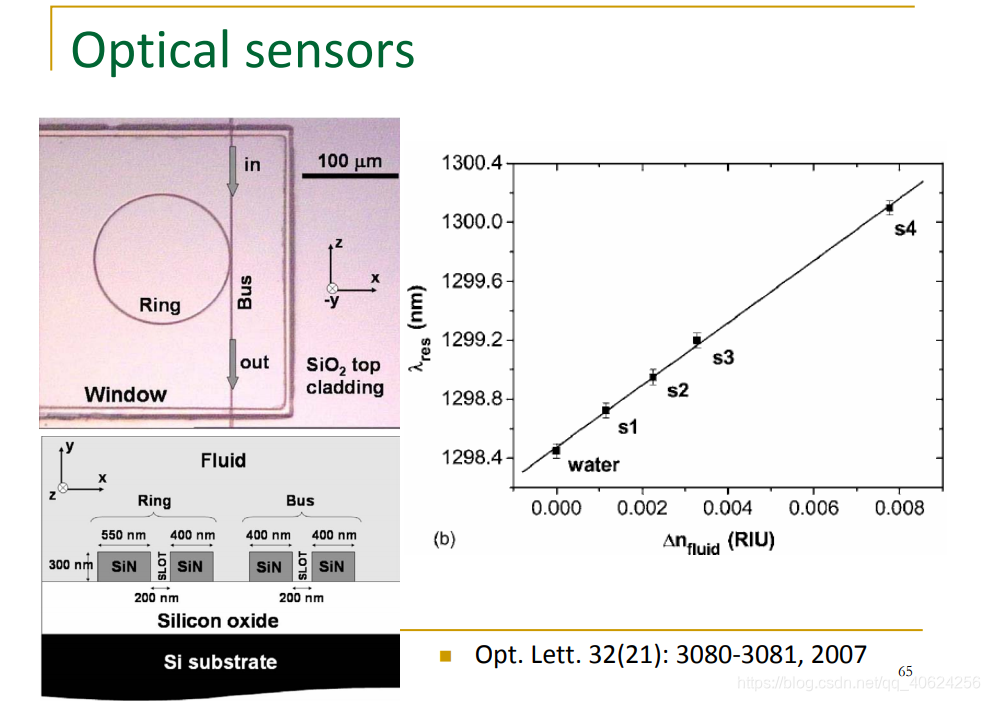

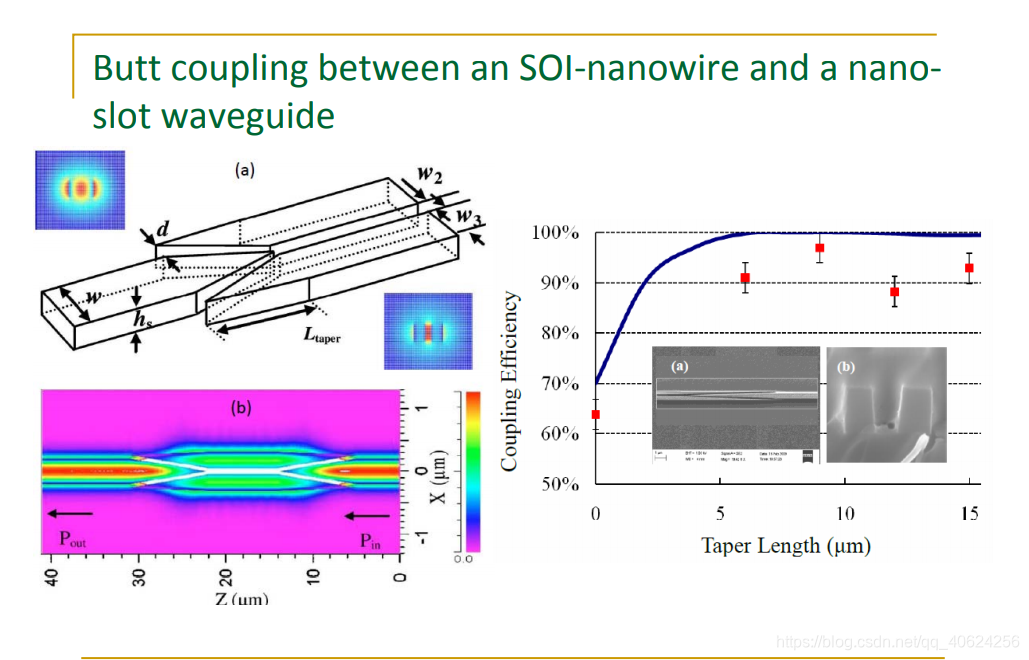

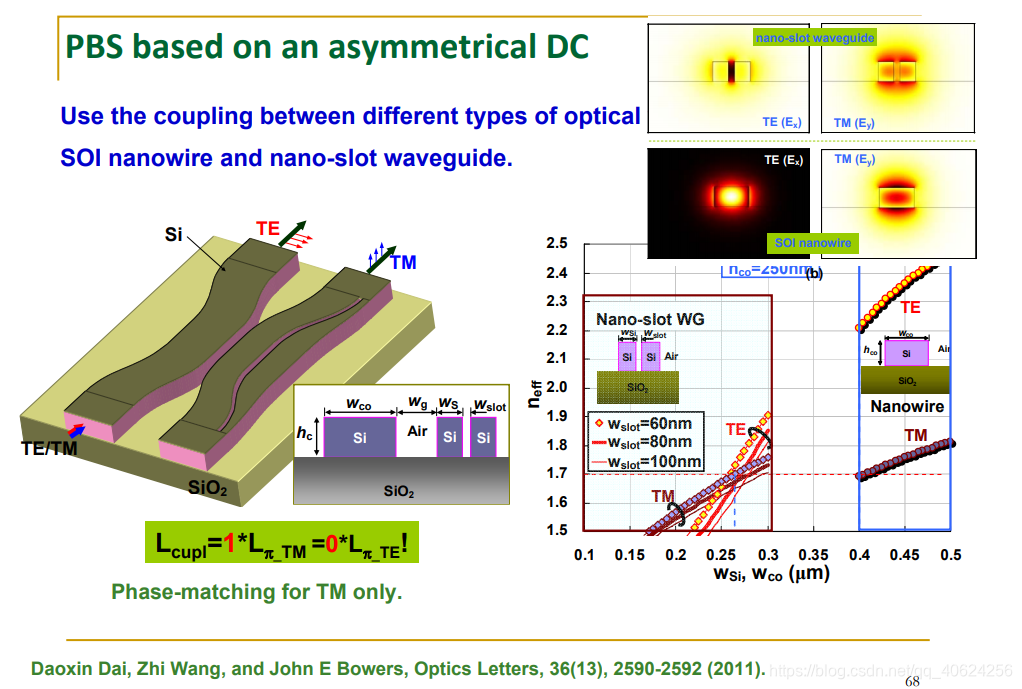

然后slot wg应用有:modulator(将具有电光特性的聚合物填充到slot里,材料和光场overlap高,则调制效率高)以及optical switch,非线性增强,传感,提升耦合效率,色散调控、控制偏振方向等;

总结

SOI nano wg包括:

SOI strip nanowires;

SOI ridge nanowires;

SOI nano-slot waveguides;这些波导形式都可以尝试用taper连接得到更好的特性。

研究的关键特性有:偏振特性,单模条件,损耗(传输损耗,弯曲损耗,散射损耗,耦合损耗,插入损耗),这些都可以从模场分布的方向出发。

2298

2298

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?