目录

8. 最终创建好的FIFO IP核如下(.veo文件!!!):编辑

2.写模块中抓取almos_empty上升沿——消除亚稳态(也可以直接用第二拍almost_empty_syn)

4.至此,写模块终于实现了!整体内容太多,拆分为两篇,见3.2

1. 实验整体框架

FIFO的介绍见视频(本子笔记),不展示,画的有点丑

FIFO读写实验

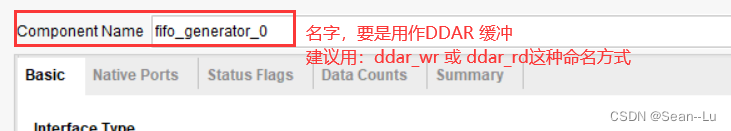

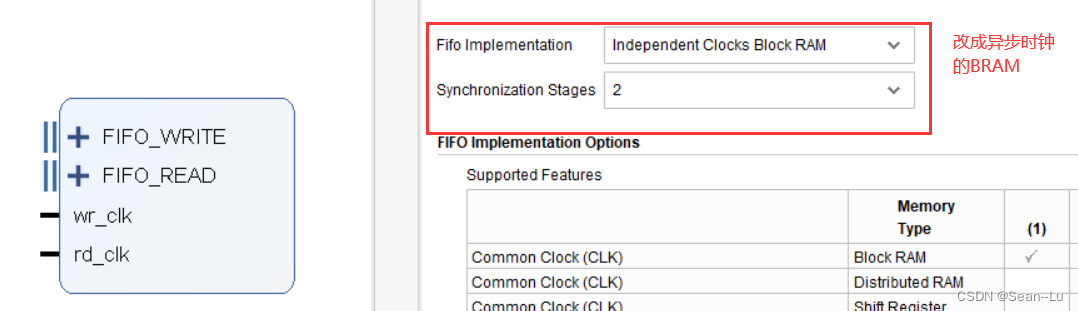

2. 创建FIFO IP核

1.先创建.v文件,因为最终FIFO也是要在.v文件中使用

2.创建FIFP IP核

3.Basic页面介绍

我们的实验简单,无需改名

常规接口就行

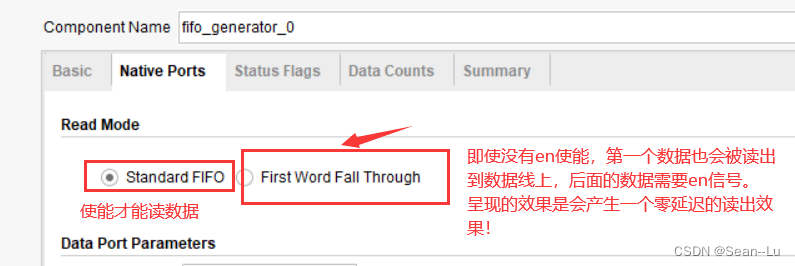

4.Native Ports页面

标准FIFO相当于延迟一个时钟

单双bit输入纠正(应该是纠正,不是注入错误!)

输出寄存器——相当于开关使能的作用,在时序特别复杂时用,需要一个使能打开输出寄存器的功能。

去掉复位端,本次实验不需要,但应该大部分情况下是需要的!

5.Status Flags

这里和FIFO的结构有关,见本子笔记(实验十)

这些都不勾选,简单的学习使用

这里也用不上,默认的就好

6.Data Counts

具体原因,只用了一个时钟,不存在异步!

修改——纠正

7.Summary

本次实验使用到的FIFO IP资源如下

8. 最终创建好的FIFO IP核如下(.veo文件!!!):

3. 例化和驱动代码

1.首先将veo中的例子复制到顶层文件中

2.创建“写FIFO模块”,编写“写模块”

1.写模块输入输出

重要说明:如果是动态读写,写模块是无需“读空(almost_empty)”信号的。

但因为本次实验,想展示:写——写满——再读——读空——再写,的一个功能。所以写模块端需要almost_empty读空信号的反馈,所以fifo_wr模块中需要接入“读空信号”。同理在fifo_rd模块中,我们也接入“写满信号”!!!

由“读空信号”、“写满信号”决定什么时候写数据、写什么数据!

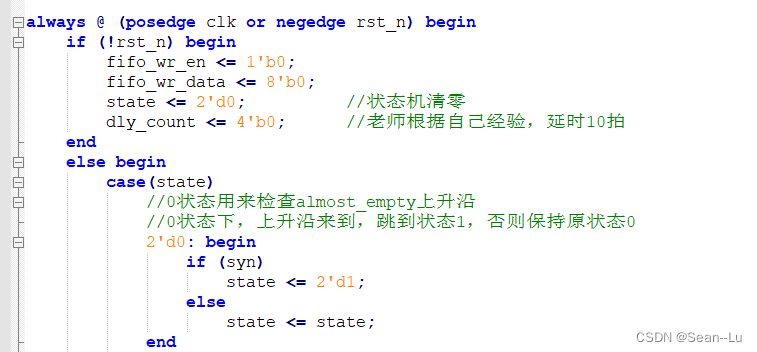

2.写模块中抓取almos_empty上升沿——消除亚稳态(也可以直接用第二拍almost_empty_syn)

3.写数据

注意:给数据赋值,当syn信号(上升沿flag)拉高时,就赋值。

但不能进行立刻赋值,因为FIFO IP核内部的信号更新有一定延迟,立刻赋值可能造成数据丢失。

因此做一个延迟,保证写数据的绝对准确!确保FIFO 内部准备好了再写入数据。

影响:使得always语句块逻辑上不好写,需要状态机,代码容易写。

状态机——Verilog语言的灵魂。

//0状态用来检查almost_empty上升沿

//0状态下,上升沿来到,跳到状态1,否则保持原状态0

//1状态用来做10拍的延迟

//1状态下,就行10拍的延迟后调到状态2——用于写数据,同时打开写使能

//给fifo写入数据

//首先判断almost_full,判断是否将要写满

//而写满信号是无需抓取上升沿的,因为写满信号和写数据都是写时钟下的,同一时钟,无需多余操作。而之前almost_empty是读时钟,到写时钟域是异步时钟,需要抓取一个上升沿!

2854

2854

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?